GATE DRIVE FOR HALF BRIDGE

NOR AZLAN BIN SHAMSUDIN

**MAY 2006**

"I hereby declare that I have read through this report and found that is sufficient in terms of scope and quality to be awarded of the Degree of Bachelor in Electrical Engineering (Industrial Power)"

Signature: .....

Name of Supervisor: Mr. Auzani Bin Jidin

Date: Mei 2006

### **GATE DRIVE FOR HALF BRIDGE**

## NOR AZLAN B. SHAMSUDIN

### B010210077

This Report Is Submitted In Partial Fulfillment of Requirements for the Degree of Bachelor in Electrical Engineering (Industrial Power).

Faculty Of Electrical Engineering

Kolej Universiti Teknikal Kebangsaan Malaysia

May 2006

"I declare that this report is the result of my own research except as cited in the references."

| Signature |                        |

|-----------|------------------------|

| Name      | NOR AZLAN B. SHAMSUDIN |

| Date      | . 4105106.             |

This dedicated to my beloved father and mother

#### ACKNOWLEDGEMENT

Firstly, grateful thank to the God by His blessing I able to finish this report on time, Alhamdulillah.

Here also I like to thanks for those who have give a lot of contribution until this project finish. Thank you very much to my supervisor, Mr. Auzani Bin Jidin that gives a lot of support, advice and idea to me during this project in progress. Not forget to my partners, Rubiah and Hisyam that always behind me when I need help in my project. What a very great teamwork I have here!

Besides that, I like to express my appreciation to all my friends that always give the support to me to finish this project. To the technicians, thank you very much with your co operation in using the lab for my project.

And lastly, to my family that always give the support from this project start until it finish, thank you a lot. I never forget it.

Thank you and may God bless you all.

#### ABSTRACT

The purpose of this project is to design gate drive circuit for half bridge which has special feature to work in two modes of operations. Only one mode of operation can be selected at instant. The two mode of operation are independent mode and dependent mode. Normally only dependent mode are available for the gate drive of the half bridge circuit. In the dependent mode two output signals are produced and both of the signals are complimented to each others. However the gate drive for half bridge with dependent mode of operation cannot be used for some applications such as flyback, push pull converters and SRM drive. For that reasons this project has to overcome that limitation, by introducing the independent mode of operation. In this project the detail explanation will be focused on how to design logic gate circuit to construct the two mode of operations. The simulation results and experimental result will be presented. Both of the results are in close agreement to each other.

#### ABSTRAK

Projek ini bertujuan untuk merekabentuk litar 'gate drive' yang mana dilengkapi dengan aplikasi 'independent'dan juga 'dependent' didalam satu litar yang sama. Litar ini terbahagi kepada dua iaitu litar yang membekal kan isyarat 'independent', isyarat 'dependent' dan juga litar gate drive'. Dimana litar pembekal isyarat yang di rekabentuk dengan rekabentuk yang mampu membekal kan isyarat 'independent' dan juga 'dependent' yang akan memberi isyarat kepada litar 'gate drive' untuk di lengahkan masa antara kedua isyarat tersebut untuk mengelakkan dari berlakunya litar pintas kepada 'power switch'. Daripada simulasi yang telah dilakukan terhadap kedua-dua litar tersebut telah berjaya untuk mendapatkan hasil yang mengikut teori yang telah dipelajari sebelum ini. Hasil keluaran litar telah dibanding beza dengan hasil simulasi dan telah menunjukkan persamaan walaupun terdapat sedikit perbezaan ,perbezaan ini berpunca dari gangguan yang berlaku akibat oleh kepersisan peranti-peranti yang digunakan tidak mencapai tahap spesifikasi yang ideal mengikut apa yang telah disimulasikan ,smbangan yang besar telah dilakukan didalam projek ini adalah dengan merekabentuk litar 'independent' dan 'dependent' didalam satu litar yang sama hanya dengan menggunakan litar logik, kecekapan litar ini bergantung kepada frekuensi yang dibekalkan kepada isyarat masukan kepada litar independent tersebut. Maka disini projek ini boleh lagi dimajukan dengan menganalisis projek ini untuk menghasil kan litar yang lebih berfrekuensi tinggi untuk membekalkan isyarat yang berfrekuensi tinggi kepada 'power switch'.

## TABLE OF CONTENTS

| CHAPTER | CONTENT                             | PAGE |

|---------|-------------------------------------|------|

|         | TITLE                               | ž E  |

|         | ADMISSIONS                          | ii   |

|         | DEDICATIONS                         | iii  |

|         | ACKNOWLEDGMENT                      | iv   |

|         | ABSTRACT                            | V    |

|         | ABSTRAK                             | vi   |

|         | TABLE OF CONTENT                    | X    |

|         | LIST OF TABLE                       | xi   |

|         | LIST OF FIGURES                     | xiii |

|         | LIST OF APPENDICES                  | xiv  |

| 1       | INTRODUCTION                        |      |

|         | 1.1Background of the gate drive     | 1    |

|         | 1.2 literature review               | 2    |

|         | 1.2.1 Previous design               | 2    |

|         | 1.2.2 Contribution and modification | 2    |

|         | 1.2.3 Iris gate drive               | 3    |

|         | 1.2.4 Half bridge gate driver IC    | 4    |

|         | 1.3 Project objective               | 5    |

|         | 1.3.1 Methodology of project        | 6    |

|         | 1.3.2 Scopes of project             | 7    |

|         | 1.3.2.1 Analysis on software        | 7    |

|         | 1.3.2.2 Analysis on hardware        | 7    |

# 2 REVIEW BASIC THEORY ON GATE DRIVE

| 2.1 Introduction                                  | 9     |

|---------------------------------------------------|-------|

| 2.2 Modeling of gate drive                        | 9     |

| 2.3 Block diagram of the gate drive               | 10    |

| 2.4 The operation of the blanking time circuit    | 11    |

| 2.4.1 Inverting- Hysteresis comparator            | 12    |

| 2.4.2 Chosen of blanking time                     | 13    |

| 2.4.3 The blanking time circuit                   | 14    |

| 2.4.4 Dead time theory results                    | 14    |

| 2.4.5 Transient waveform on blanking time circuit | 115   |

| 2.4.6 Voltage charging transient                  | 16    |

| 2.4.7 Voltage discharging transient               | 17    |

| 2.4.8 Different reference ground                  | 18    |

| 2.4.9 The need of electrical isolation            | 18    |

| 2.5 Schematics of optocouplers                    | 19    |

| 2.5.1 The truth table for optocouplers HCPL 3150  | 19    |

| 2.5.2 Recommended specification                   | 20    |

| 2.5.3 Diagram of the optocouplers                 | 20    |

| 2.6 Isolated dc power supply                      | 21    |

| 2.6.1 Introduction of SMPS                        | 21    |

| 2.6.2 The operating of push pull converter        | 22    |

| 2.6.3 The waveform of push pulls converters       | 23    |

| 2.6.4 The advantages and disadvantages of SMPS    | 24    |

| 2.6.5 The explanation of both table 1 and 2       | 25    |

| 2.6.6 SMPS schematics diagram                     | 26    |

| 2.6.7 High frequency transformers                 | 27    |

| 2.6.8 Death time circuit                          | 28    |

| 2.6.9 Association waveform for gate drive         | 29-30 |

|   | 2.7 Associate waveform before and after modification        | 31    |

|---|-------------------------------------------------------------|-------|

|   | 2.7.1 Before modification                                   | 31    |

|   | 2.7.2 After modification                                    | 32    |

|   | 2.8 Design of an independent circuit                        | 33    |

|   | 2.8.1 Truth table of independent circuit                    | 33    |

|   | $2.8.2~\mbox{K-map}$ of the truth table for out A and out B | 34    |

|   | 2.8.3 Schematics of the independent circuit                 | 35    |

|   | 2.8.4 Associate waveform of independent circuit             | 36    |

| 3 | EXPRIMENTAL SET UP                                          |       |

|   | 3.1 Introduction                                            | 37    |

|   | 3.2 Block diagram of the experimental set up                | 38    |

|   | 3.3 Schematics and picture of the hardware                  | 38    |

|   | 3.3.1 Real picture of SMPS                                  | 39    |

|   | 3.3.2 Dead time circuit schematics                          | 39    |

|   | 3.3.3 Real picture of the gate drives                       | 40    |

|   | 3.3.4 Schematics of the independent circuits                | 40    |

|   | 3.3.5 Real picture of the independent circuits              | 41    |

|   | 3.3.6 The complete experimental set up                      | 41    |

| 4 | EXPRIMENTAL RESULT                                          |       |

|   | 4.1 Introduction                                            | 42    |

|   | 4.2 Simulation results                                      | 42    |

|   | 4.2.1 Previous gate drive result                            | 43-44 |

|   | 4.2.2 Analysis of the blanking time                         | 45-46 |

|   | 4.2.3 The transient result by varying the resistors         | 47-48 |

|   |                                                             |       |

|   | 4.3 Independent simulation results                | 49 |

|---|---------------------------------------------------|----|

|   | 4.3.1 Independent and dependent results           | 50 |

|   | 4.3.2 Experimental results on independent circuit | 51 |

|   | 4.3.3 Dependent results                           | 51 |

|   | 4.3.4 Independent results                         | 52 |

| 5 | CONCLUSION AND RECOMMENDATION                     |    |

|   | 5.1.0                                             | 52 |

|   | 5.1 Conclusions                                   | 53 |

|   | 5.2 Recommendations                               | 54 |

|   | REFERENCE                                         | 55 |

# LIST OF TABLES

| NO  | TITLE                 | PAGE |

|-----|-----------------------|------|

| 2.1 | Advantages of SMPS    | 24   |

| 2.2 | Disadvantages of SMPS | 24   |

| 2.3 | Truth table           | 33   |

| 2.4 | K-map for out A       | 34   |

| 2.5 | K-map for out B       | 34   |

# LIST OF FIGURES

| NO     | TITLE                                | PAGE |

|--------|--------------------------------------|------|

| 2.1    | Block diagram of project             | 10   |

|        |                                      | 11   |

| 2.2    | Inverter theory                      | 12   |

| 2.3    | Inverter                             |      |

| 2.4    | Truth table of the inverter          | 12   |

| 2.5    | Inverter waveform                    | 13   |

| 2.6    | Blanking time circuit                | 14   |

| 2.7    | Associate waveform on dead time      | 14   |

| 2.8    | Blanking time waveform               | 15   |

| 2.9    | Charging theory                      | 16   |

| 2.9.1  | Discharging theory                   | 17   |

| 2.9.2  | Converter leg                        | 18   |

| 2.9.3  | Optocouplers diagram 1               | 19   |

| 2.9.4  | Truth table optocouplers             | 19   |

| 2.9.5  | Recommended specification            | 20   |

| 2.9.6  | Optocouplers diagram 2               | 20   |

| 2.9.7  | Push pull diagram                    | 22   |

| 2.9.8  | Associate waveform of push pulls     | 23   |

| 2.9.9  | SMPS diagram                         | 26   |

| 2.9.10 | Transformers                         | 27   |

| 2.9.11 | Dead time diagram                    | 28   |

| 2,9.12 | Theory waveform of gate drive        | 29   |

| 2.9.13 | Blanking time theory waveform        | 29   |

| 2.9.14 | Waveform theory of blanking time     | 31   |

| 2.9.15 | Independent theory waveform          | 32   |

| 2.9.16 | Independent diagram                  | 35   |

| 2917   | Input signal waveform of independent | 36   |

| 2.9.18 | Output signal waveform of independent                   | 36 |

|--------|---------------------------------------------------------|----|

| 3.1    | Block diagram of the experimental set up                | 38 |

| 3.2    | Schematics of the SMPS                                  | 38 |

| 3.3    | SMPS circuit                                            | 39 |

| 3.4    | The dead time circuit schematics                        | 39 |

| 3.5    | Gate drive circuit                                      | 40 |

| 3.6    | Schematics of the logic independent circuits            | 40 |

| 3.7    | logic gate circuit                                      | 41 |

| 3.8    | Complete set up                                         | 41 |

| 4.0    | Gate drive schematics                                   | 43 |

| 4.1    | input signal waveform                                   | 43 |

| 4.2    | Second stage waveform                                   | 43 |

| 4.3    | Third stage waveform                                    | 44 |

| 4.4    | Invert waveform                                         | 44 |

| 4.5    | Optocoupler waveform                                    | 44 |

| 4.6    | Transient waveform with various resistances             | 45 |

| 4.7    | Blanking time with 100 ohm resistors                    | 45 |

| 4.8    | Blanking time with 1 kilo ohm resistances               | 46 |

| 4.9    | Blanking time with 5 kilo ohm resistance                | 46 |

| 4.9.1  | Charging voltage waveform                               | 47 |

| 4.9.2  | Discharging voltage waveform                            | 48 |

| 4.9.3  | Simulation on independent waveform                      | 49 |

| 4.9.4  | Differential between dependent and independent waveform | 50 |

| 4.9.5  | Hardware dependent waveform                             | 51 |

| 496    | Hardware independent waveform                           | 52 |

# LIST OF APPENDICES

| APPENDIX | TITLE                     | PAGE |  |

|----------|---------------------------|------|--|

|          |                           |      |  |

| Δ        | APPLICATION ON GATE DRIVE | 56   |  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background of the gate drive

Gate drive has been widely used in switching application, where the gate drives are the interface between the control circuit and power switch. It's amplified the control signal to a level required to drive the power switch and also provide electrical isolation between power switch and logic level signal processing control circuit. The primary function of this gate drive is to switch on and off in vice versa to the power switch by providing the correct blanking time due to prevent from cross conduction.

We cannot avoid of getting a few problem when designing this gate drives, the objective of this project is to improve the gate drive before that has been design by En Zulkifli by implementing an independent signal. With the proper design of an independent circuit, it is expected to make this gate drive can be used in converter that's needed in independent mode applications and independent mode also.

### 1.2 Literature review

## 1.2.1 The previous design

From the previous research, the gate drive that has been designed by En Zulkifli were only made up to provide only one input signal and used only in switching dependant application, and so the usage of this gate drive were limited. And by implementing the dependant circuit that has been designed the application of this gate drive will able to functioning in both dependant and independent application, also this gate drive before were less reliable that cause by the instability of the ic that does not perform well as it's function and this gate drive were only used for low voltage purposed application.

#### 1.2.2 The contribution and modification

The modification that has been made here are by designing an independent circuit to the gate drive before where now this gate drive will be able to drive an independent application converter such as push pull dc-dc converter and fly back half/full bridge dc-dc converter. Where this both two application needed two input signal instead of one to function. An independent application such as push pull converter needed an independent signal and the independent signal is where both of the signals are independent against each other and the needed of this independent signal are important because there are time when both of the gate signal were turn off and it cannot be done by dependant input signal that only compliment against it's signal and can not provide the simultaneously turn off.

### 1.2.3 IRIS gate drive

### The Mosfet gate drive (TO-220/TO-262) 5 legs in IC packaging

The IRIS Series integrated switchers combine a low-loss HEXFET® power MOSFET with a dual-mode voltage and current control IC and MOSFET gate drivers in a single 5-pin TO-220 or TO-262 package. The devices are optimized for fly back topologies in universal- and single-input, 30 to 180W switched mode power supplies (SMPS).

To allow design flexibility and ruggedness, the IRIS Series integrated switchers include over-voltage protection as well as over-temperature and variable over-current protection.

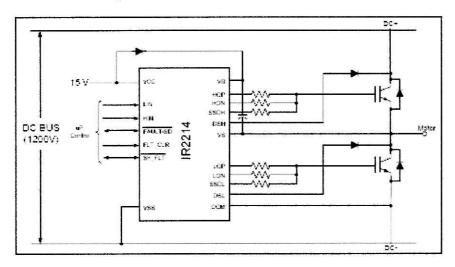

## 1.2.4 Half bridge gate driver IC

# Schematic diagram IR2214

# Characteristic of IC IR2214

| Voffset                                   | 600V or<br>1200V max. |

|-------------------------------------------|-----------------------|

| IO+/- (typ)                               | 2.0 A / 3.0A          |

| Vout                                      | 10.4V - 20V           |

| Deadtime matching (max)                   | 75 nsec               |

| Deadtime (typ)                            | 330 nsec              |

| Desat blanking time (typ)                 | 3 µsec                |

| DSH, DSL input voltage<br>threshold (typ) | 8.0 V                 |

| Soft shutdown time (typ)                  | 9.25 µsec             |

This summary of this product shows the entire data sheet for voltage, current, dead time, blanking time and input voltage threshold. As we can see here the dead time for this gate drive is 330 nanosecond and its shows that the blanking time here are quite fast and its help a lot to increase the speed of the switching.

### 1.3 Project objective

The objectives of this project are as follow:

- i) To understand the operation of the blanking time in the gate drive for half bridge.

- ii) To study the operation of each part in the gate drive for half bridge circuit, consist of isolated dc supply, blanking time circuit and logic gate circuit.

- iii) To design the logic gate circuit using k-map and Boolean's that can provide 2 mode of operation.

- iv) To implement the hardware of logic gate circuit based on the circuit design using Or-Cad P-Spice

Doing analysis and research is the main thing that should be implemented first in this project. On this purpose all the information about gate drives is been gathered and collected from the sources like books, journals, paperwork's and also from the internet as a reference. Beside that the expertise of using Or Cad are also required to fulfill the purpose of this project in order to simulate the circuit and understand more about the function of gate drives by doing on simulation.

### 1.3.1 Methodology of project

Here are the steps or the methodology of the project that has been taken:

- Firstly doing simulation on the previous gate drive design by using Or Cad software.

- Secondly analysis of the simulation results and discuss with the supervisor to seek the solution together.

- iii) Thirdly a new solution been discovered, to implemented the independent signal to the previous design.

- A truth table is made and from the truth table the k-map been made to design an independent circuit.

- v) The circuit been constructing based on the truth table and k-map.

- vi) The new design circuit that has been constructed will be analyzed on Or Cad software.

- vii) The construct circuit was tested to get the similar result as the simulation result and then the circuit been merge with the previous gate drives.

#### 1.3.2 Scopes of project.

### 1.3.2.1 Analysis on software.

Analysis on software will be get going first before the implemented the hardware, software that will be use is Or cad where first step is implemented the design circuit to this software and simulate to see the output on this circuit whether it's according to the correct theory that has been discuss with the supervisor. Although this method has been analyzed and been done but its still far enough from theory before and there's some error that needed to be fix back, are this error are from the circuit or it's the problem of the software itself, it can be possible both way because there's some library in this software are not capable to support the design circuit that contains a component that doesn't have in the library in this software.

### 1.3.2.2 Analysis on hardware.

Analysis on hardware will be done part by part within in building the circuit the analysis will be done to make sure that the connection and placement of the component are in the right order. Oscilloscope will be used to monitor the output waveform on the circuit to see plus to compare with the output waveform from the simulation result. Some calculation will be taken to seek the truth answer to the both display result.

8

## 1.4 Project organization

The rest of project chapter are organized as follows:

Chapter 2: Review of the basic theory of the gate drive circuit completed with independent input signal theory and the differentiate of the linear and SMPS (switch mode power supply) power supply, and also this chapter explain the type and functionality of the transformers that been used. This chapter also will provide expected result from the projects. This chapter also will show how the truth table is been made and directly shown how the independent circuit was made from the truth table.

Chapter 3: This chapter describe about the hardware implementing components that been used, and also all the set up components for the gate drives and independent circuit.

Chapter 4: Comparing the simulation result along side with the experimental result, to show that the objectives of this project are been achieved to provide an independent circuit signal to the gate drive.

Chapter 5: Give the conclusion and suggestion to the project