### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

# A Study of Design for Environment Using Lifecycle Approach for Semiconductor Packaging Processes

Thesis submitted in accordance with the requirements of the

Universiti Teknikal Malaysia Melaka for the Bachelor's Degree of

Manufacturing Engineering (Design)

By

Nurul Hidayah bt. Arshad

Faculty of Manufacturing Engineering

May 2007

### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## BORANG PENGESAHAN STATUS TESIS\*

| JUDUL: A STUDY OF DESIGN SEMICONDUCTOR SESI PENGAJIAN: 2006/20           | ON FOR ENVIRONMENT USING LIFE CYCLE APPROACH FOR PACKAGING PROCESSES                                                                                                                           |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3L31 FLINGAJIAN . 2006/20                                                | <u>07</u>                                                                                                                                                                                      |

| Saya <u>NURUL HIDAYAH BT</u>                                             | (HURUF BESAR)                                                                                                                                                                                  |

| mengaku membenarkan te<br>Universiti Teknikal Malaysi<br>berikut:        | sis (PSM/Sarjana/Doktor Falsafah) ini disimpan di<br>a Melaka (UTeM) dengan syarat-syarat kegunaan seperti                                                                                     |

| <ol><li>Perpustakaan Universiti<br/>untuk tujuan pengajian</li></ol>     | an membuat salinan tesis ini sebagai bahan pertukaran                                                                                                                                          |

| SULIT                                                                    | (Mengandungi maklumat yang berdarjah keselamatan<br>atau kepentingan Malaysia yang termaktub di dalam<br>AKTA RAHSIA RASMI 1972)                                                               |

| TERHAD                                                                   | (Mengandungi maklumat TERHAD yang telah ditentukan oleh organisasi/badan di mana penyelidikan dijalankan)                                                                                      |

| √/ TIDAK TERHAD                                                          |                                                                                                                                                                                                |

| (TANDATANCAN DEN                                                         | Disahkan oleh:                                                                                                                                                                                 |

| (TANDATANGAN PEN                                                         | IULIS) (TANDATANGAN PENYELIA)                                                                                                                                                                  |

| Alamat Tetap:<br>LOT 460, KM10, KG KETAP<br>MUKIM PERNU, 75460<br>MELAKA | ANG  Cop Rasmi: NIK MOHD. FARID BIN CHE ZAINAL ABIDIN  Jurutera Pengajar  Fakulti Kejuruteraan Pembuatan  Universiti Teknikal Malavsia Melaka  Karung Berbut di 1200 . Ler Keroh  75450 Melanu |

| Tarikh: <u>17 May 2007</u>                                               | Tarikh: 19/3/2001                                                                                                                                                                              |

<sup>\*</sup> Tesis dimaksudkan sebagai tesis bagi Ijazah Doktor Falsafah dan Sarjana secara penyelidikan, atau disertasi bagi pengajian secara kerja kursus dan penyelidikan, atau Laporan Projek Sarjana Muda (PSM). \*\* Jika tesis ini SULIT atau TERHAD, sila lampirkan surat daripada pihak berkuasa/organisasi berkenaan dengan menyatakan sekali sebab dan tempoh tesis ini perlu dikelaskan sebagai SULIT atau TERHAD.

### **APPROVAL**

This thesis submitted to the senate of UTeM and has been accepted as partial fulfillment of the requirements for the Bachelor's Degree of Manufacturing Engineering (Design). The members of the supervisory committee are as follow:

Main Supervisor

(Official Stamp & Date)

### **DECLARATION**

"I hereby declare that this report and its entire contents is my own work unless specific reference and figure are made in the text. This work is submitted in partially fulfillment of Bachelor's Degree in Manufacturing Engineering (Design) and has not been submitted for any other qualification in any other institution."

| Signature     |   | 19.                      |

|---------------|---|--------------------------|

| Author's Name |   | NURUL HIDA-JAH BY ARTHAD |

| Date          | • | 29/5/07                  |

### **ABSTRACT**

The greatest opportunity to reduce the environmental impact of a new product occurs during the design phase of its life cycle. Design for Environment (DfE) tools, when implemented, become part of the product development process. DfE tools are one way to assess environmental impact of a product. This paper is focusing on the electronic product of semiconductors which the environmental impact of the processes are evaluated. Tools used in this paper are simple checklist questions and Environmentally Responsible Process-Assessment matrix. This study is conducted in a semiconductor company where the processes involves are evaluated in terms of its contribution to the environment. The environmental concerns that were identified early in the process development can be most effectively and economically resolved and life-cycles studies and DfE can be used as tools to aid in decision-making.

### **ABSTRAK**

Peluang untuk mungurangkan impak terhadap alam sekitar bagi sesuatu produk baru wujud semasa di peringkat merekabentuk produk sepanjang kitaran hidup produk itu. Apabila rekeabentuk untuk alam sekitar diaplikasikan, ia merupakan sudah terlibat dalam perkembangan penghasilan produk. Kaedah merekabentuk untuk alam sekitar merupakan salah satu langkah menganalisa impak yang terhasil daripada sesuatu produk terhadap alam sekitar. Kajian kertas kerja ini tertumpu pada alat electronik seperti semikonduktor dimana impak terhadap alam sekitar diselidik dan dinilai untuk setiap proses yang dilalui. Antara kaedah yang digunakan dalam projek ini adalah soal selidik, dan "Environmentally Responsible Process-Assessment" matriks. Projek ini mengkaji jenis-jenis pencemaran dan gangguan yang dihasilkan oleh produk terhadap alam sekitar sepanjang kitaran hidup produk itu. Kajian ini dilakukan di sebuah syarikat pengeluar semikonduktor. Daripada kajian, didapati, kaedah ERPA ini sesuai untuk digunakan pada peringkat awal pemajuan proses untuk sesebuah produk. Kaedahkaedah yang digunakan dalam projek ini memberi banyak maklumat dalam penilaian pencemaran dalam setiap peringkat kitaran hidup dan rekabentuk untuk alam sekitar sesuai digunakan sebagai kaedah membuat keputusan.

### DEDICATION

For My Dear Mama and Ayah.

### **ACKNOWLEDGEMENT**

I would like to thank the following individuals, in no particular order, for graciously taking the time out of their busy day to patiently answer my questions and giving their opinions and thoughts. Any mistakes are, of course my own.

Dr. Arshad Kassim, Rosdiadi Ramli, Nor Hayati Rahim, Theresa Tan, En Nik Mohd Farid, Khalil b. Omar, my dearest brothers and sisters and last but not least my fellow friends.

# TABLE OF CONTENTS

| Abst | tract                                   | i   |

|------|-----------------------------------------|-----|

| Abst | trak                                    | ii  |

| Ded  | ication                                 | iii |

| Ack  | nowledgement                            | iv  |

| Tabl | le of contents                          | v   |

| List | of Figures                              | vii |

| List | of Tables                               | x   |

|      |                                         |     |

| 1.0  | INTRODUCTION                            | 1   |

|      | 1.1. Introduction of Research           | 1   |

|      | 1.2. Objective of research              | 3   |

|      | 1.3. Problem statement                  | 3   |

|      | 1.4. Scope of research                  | 4   |

| 2.   | LITERATURE REVIEW                       | 5   |

|      | 2.1. Introduction                       | 5   |

|      | 2.2. Design for Environment.            | 6   |

|      | 2.2.1. Basic principles of DfE          | 8   |

|      | 2.2.2. DfE strategies                   | 9   |

|      | 2.2.3. Benefits of DfE implementation   | 10  |

|      | 2.3. Life Cycle Concept                 | 13  |

|      | 2.4. DfE Tools with Life Cycle Approach | 20  |

|      | 2.5. DfE Tools                          | 22  |

|      | 2.6. Streamlined Life Cycle Assessments | 26  |

|      | 2.7. Environmental Impact               | 28  |

| 3. | METHODOLOGY.                                             | 31 |

|----|----------------------------------------------------------|----|

|    | 3.1. Introduction                                        | 31 |

|    | 3.2. Title Definition.                                   | 31 |

|    | 3.3. Objectives                                          | 32 |

|    | 3.4. Problem Statement Identification                    | 32 |

|    | 3.5. Gantt chart                                         | 32 |

|    | 3.6. Literature review.                                  | 34 |

|    | 3.7. Selection of DfE tools                              | 34 |

|    | 3.8. Determine Packaging Processes of MicroArray Package | 34 |

|    | 3.9. Define Study Scope.                                 | 35 |

|    | 3.10. Identify exchanges in the Processes involves       | 35 |

|    | 3.11. Evaluation using ERPA                              | 35 |

|    | 3.12. Conclusion.                                        | 36 |

|    |                                                          |    |

| 4. | COMPANY BACKGROUND                                       | 37 |

|    | 4.0. National Semiconductor (M) Sdn. Bhd                 | 37 |

|    | 4.1. NSEM Manufacturing Process Flow.                    | 38 |

|    | 4.2. CASE STUDY: Semiconductor Product                   | 39 |

|    | 4.3. Process Definition.                                 | 42 |

|    | 4.3.1 Wafer Lamination.                                  | 42 |

|    | 4.3.2 Wafer Backgrind                                    | 43 |

|    | 4.3.3 Wafer Mounting                                     | 44 |

|    | 4.3.4 Wafer Saw                                          | 45 |

|    | 4.3.5 UV Cure                                            | 47 |

|    | 4.3.6 Die attach                                         | 48 |

|    | 4.3.7 Poly Cure                                          | 50 |

|    | 4.3.8 Wire bonding                                       | 50 |

|    | 4.3.9 Molding                                            | 53 |

|    | 4.3.10 Detaping                                          | 54 |

|    | 4.3.11 Post Mold Cure                                    | 55 |

|    | 4.3.12 Electro Deflash                                   | 55 |

|     |        | 4.3.13 Marking                                | 56 |

|-----|--------|-----------------------------------------------|----|

|     |        | 4.3.14 Ball Attach                            | 56 |

|     |        | 4.3.15 Strip Mounting.                        | 57 |

|     |        | 4.3.16 Package Saw/ Singulation               | 59 |

| 5.  | CASI   | E STUDY                                       | 60 |

|     | 5.1.   | Process Assessment Method                     | 61 |

|     | 5.2.   | Environmental Concerns                        | 64 |

| 6.  | RES    | ULTS                                          | 68 |

|     | 6.1    | Introduction                                  | 68 |

|     | 6.2    | Environmentally Responsible Assessment Matrix | 69 |

|     | 6.3    | Plotted Targets                               | 71 |

| 7.  | DISC   | CUSSIONS                                      | 77 |

|     | 7.1    | Introduction                                  | 77 |

| 8.  | CON    | NCLUSIONS AND RECOMMENDATION                  | 81 |

|     | 8.1    | Conclusion                                    | 81 |

|     | 8.2    | Recommendations                               | 81 |

| REI | EREN   | CES                                           | 82 |

| APF | PENDIC | CES                                           |    |

| A   | Ghan   | ntt Chart                                     |    |

| В   | Chec   | klist Questions                               |    |

| C   | Bann   | ned and Reported Substance in NSEM            |    |

| D   | Micro  | oArray Chemical Compositions                  |    |

# LIST OF FIGURES

| 2.1  | Life Cycle stages of a typical product and associated environmental |    |

|------|---------------------------------------------------------------------|----|

|      | impact                                                              | 8  |

| 2.2  | Product life cycles                                                 | 15 |

| 2.3  | Main phases of physical life cycle and interaction                  | 16 |

| 2.4  | Phases of material production                                       | 17 |

| 2.5  | Phases of product manufacture                                       | 18 |

| 2.6  | A partial view of a flowchart used by Medtronic. Inc to implement   |    |

|      | design for the environment                                          | 24 |

| 2.7  | DFE matrix example                                                  | 25 |

|      |                                                                     |    |

| 4.1  | National Semiconductor Sdn Bhd, Melaka                              | 37 |

| 4.2  | MicroArray Package                                                  | 39 |

| 4.3  | Cross section of MicroArray package                                 | 40 |

| 4.4  | Lamination Tape                                                     | 44 |

| 4.5  | Wafer Peeling after Lamination                                      | 44 |

| 4.6  | Wafer mount process                                                 | 44 |

| 4.7  | Laminated wafer ready to proceed to wafer saw                       | 45 |

| 4.8  | A grinder employs a rotating grinding wheel to thin semiconductor   | 46 |

|      | wafers                                                              |    |

| 4.9  | Photo of Backgrind Process                                          | 46 |

| 4.10 | Wafer mounting process                                              | 47 |

| 4.11 | Wafer saw blades                                                    | 48 |

| 4.12 | Kerf width                                                          | 48 |

| 4.13 | Diamond saw cut wafer into dies                                     | 49 |

| 4.14 | Machine Wafer Saw                                                   | 49 |

| 4.15 | Die Attach process                                                  | 50 |

| 4.16 | Die attach machine                   | 51 |

|------|--------------------------------------|----|

| 4.17 | Wire loop                            | 53 |

| 4.18 | Free-air ball                        | 53 |

| 4.19 | Gold ball bond                       | 54 |

| 4.20 | Gold wedge on the lead finger        | 54 |

| 4.21 | Wire bonders machine                 | 54 |

| 4.22 | Mold chases                          | 55 |

| 4.23 | After molding process                | 55 |

| 4.24 | Automold system                      | 56 |

| 4.25 | Robot grip to pull the tape          | 56 |

| 4.26 | Laser arking machine                 | 58 |

| 4.27 | Laser marking process                | 58 |

| 4.28 | Different solder ball size           | 59 |

| 4.29 | Solder ball attached to the compound | 60 |

| 4.30 | Ball Mounting machine                | 60 |

| 5.1  | Life cycle stages                    | 62 |

| 6.1  | Wafer saw target plot                | 73 |

| 6.2  | Die Attach target plot               | 73 |

| 6.3  | Wirebond target plot                 | 74 |

| 6.4  | Encapsulation target plot            | 74 |

| 6.5  | Laser marking target plot            | 75 |

| 6.6  | Ball attach target plot              | 75 |

| 67   | Singulation target plot              | 76 |

## LIST OF TABLES

| 1 | DfE strategies                                                   | 8  |

|---|------------------------------------------------------------------|----|

| 2 | Motorola's life-cycle matrix (Graedel, 1998)                     | 27 |

| 3 | The Environmentally responsible process-assessment matrix        | 66 |

| 4 | Environmentally responsible process assessment matrix result for |    |

|   | each process                                                     | 70 |

# CHAPTER 1

### INTRODUCTION

### 1.1 Introduction of Research

Environmentally responsible product development (ERPD), also known as environmentally benign manufacturing, considers both environmental impacts and economic objectives during the numerous and diverse activities of product development and manufacturing. ERPD seeks to develop energy-efficient and environmentally benign products. Products generate environmental impacts from extracting and processing raw materials throughout their life cycle; during manufacturing, assembly, and distribution; due to their packaging, use, and maintenance; and at their end of their life. There are many ways to minimize these environmental impacts. Studies demonstrate the greatest opportunity for ERPD occurs during the product design phases. The decisions that are made during these phases determine most of the product's environmental impact. Although ERPD requires extra effort, it not only protects the environment but also reduces life-cycle costs by decreasing energy use, reducing raw material requirements, and avoiding pollution control.

Consequently, manufacturing companies have spent a great deal of effort developing tools and to help designers create kind-to-environmental product. Two major classes of tools are Life Cycle Assessment (LCA) and Design for Environment (DfE) tools. LCA provides a fundamental methodology that evaluates and analyze the environmental

impact generated over the life-cycle of a product. DfE tools are design decision support tools that help a designer improving product design.

Many obstacles to the effective use of LCA and DfE tools have been noted. Two of the most significant obstacles are the difficulties acquiring the needed data and the challenges developing realistic, appropriate metrics of environmental impact. Consequently, LCA and DfE tools are, generally, not integrated with the other activities and tools used in the product development process. That is the information flow and decision-making required for existing LCA and DfE tools to be effective is inconsistent with the information flow and decision-making present in product development organizations. The result is often a post-design, standalone, environmental review of a product.

This study focuses on the application of Design for Environment tools in determining the environmental impacts throughout semiconductor packaging processes. Design for Environment (DfE) is a product design approach which gains so much attention due to the fact that world is threatens by many kinds of pollutions. Nowadays, people in society are beginning to focus more on the importance of the environment preservation. Surrounding water, air and ground have been contaminated by the pollutions and continue to increase day by day. Many citizens are becoming more concerned with the environmental practices of the industries that surround them. Even government has taken a step forward by authorize and setup environmental regulations, policies and procedures which restrict industry's environmental practices. As a result, every industry is forced to improve their environmental record to produce greener products and use greener processes. Everything in this world gives a great impact to the environment. Companies in various parts of the world are adopting the design for environment concept in their business.

The research of this study involves the application and the implementations of DfE with life cycle approach in a product development and the effects that arose from the

impact especially related to semiconductor packaging processes. The processes that semiconductor goes through contribute high level of environmental impact. And through identification of the stages in product life cycles that lead to pollutant and waste formation, the method of Environmentally Responsible Process-Assessment Matrix (ERPA) is able to identify the level of waste each process contributes. This study is also focusing on what will happen to the semiconductor product after customer-used and approaching the end of its life as well as understanding the product development relationship between the life cycle and end-of-life of a product.

### 1.2 Objective of research

The objective of this study is:

- To identify and determine the manufacturing processes of microArray package

- ii) To understand the importance of Design for Environment in productions of a semiconductor package using ERPA methodology.

- iii) To determine what types of pollutions, wastes and emissions to air, water and land the processes will contribute over a life-cycle

- iv) To find out what will happen to the product once it approaches its end of life.

#### 1.3 Problem statement

Semiconductor industry is one of the vast growing industries with new types of semiconductor product being introduced every year. It is also known to be one of the industries that contribute high environmental impact but they have set environmental performance goals for its processes and operations. Semiconductor is one of the main

trigger of technology development these days. However, the convenience provided by semiconductors also has a downside - pollution of air, water and ground, contaminations, wastes and exploitation of land in processes during the semiconductor packaging process. Threats to the environment have become more and more severe as new semiconductors are introduced like growing mushrooms. Every product goes through the same life cycle stages where it produces different kinds of threats to the environment during its production. Therefore, this study is focusing on what are the environmental contributions from the packaging processes of semiconductor by studying the environmental concerns of a MicroArray package using Graedel and Allenby's Environmentally Resposible Process-Assessment Matrix.

### 1.4 Scope of research

The scopes of this study are:

- i) Researching the Processes of Semiconductor packaging

- Researching the environmental concerns throughout semiconductor's packaging processes.

- iii) Input and output identification of each process.

# CHAPTER 2 LITERATURE REVIEW

#### 2.1 Introduction

Traditionally, the most important objectives of manufacturing industries are productivity and quality improvement, but now environmental considerations are gradually being integrated into industrial operations. Government bodies, consumers and manufacturers are now requiring an assessment of the environmental quality of certain products. These include finding ways on how to minimize solid wastes generation, water and energy consumption and even greening the supply chain of process industries. Moreover, there is already an increasing pressure on the improvement of process efficiencies on different chemical and process industries.

Manufacturing industries have been using various end-of-pipe treatments technology but using inherently clean processes can minimize dependence on these. This entails the incorporation of environmental factors into the process design for the optimization of environmental performance of a product throughout its life cycle that includes the selection of which raw material or component is the best option to consider which is known as the Design for Environment or DFE and how it is analyzed using several different DfE tools and LCA tools.

This chapter review about the sources and researches that have been done before especially related to Design for Environment (DfE) and Life Cycle Assessment (LCA).

Definitions, principles, methods, applications and implementation of design for environment and LCA concept is reviewed and summarized. Taking the examples and concept of the research done by others, it can be applied in this study.

### 2.2 Design for Environment

J.M Yarwood and D.E Eagan define Design for Environment as "a systematic way of incorporating environmental attributes into the design of a product". In other word, it is an approach that considers the environmental attributes of the entire life-cycle of a product with the aim of eliminating or minimizing any damage to the environment. DfE has three unique characteristics of DfE (Yarwood and Eagan, 1998):

- i) The entire life-cycle of a product is considered.

- ii) Point of application is early in the product realization process.

- iii) Decisions are made using a set of values consistent with industrial ecology, integrative systems thinking or another framework.

Design for the Environment (DfE) has been the area of receiving the most emphasis by engineers (Ishii, 1998). Graedel and Allenby (1995) mention design as the stage that has the strongest influence on environmental impact. DfE, an integral component of the "design for X" paradigm, covers a wide range of product development activities including such tasks as choosing materials, examining the product usage phase to reduce environmental impact, designing for energy efficiency, minimizing industrial residues during manufacturing, designing for recycling, etc. This shows that environment has becoming a major consideration in designing a product in every aspect.

Moreover, Robert Hill (2001) quoted that DfE is "the systematic application of environmental and human health considerations at the product design stage". Giudice et al (2006) pointed out that DfE can be defined as a methodology directed at the systematic reduction or elimination of the environmental impacts implicated in the

whole life cycle of a product, from the extraction of raw materials to disposal. The methodology is based on evaluating the potential impacts throughout the entire course of the design process. He also added that DfE is characterized by two other aspects, particularly:

- i) The dual level of intervention, regarding both products and processes.

- ii) The proactive action intervention, based on the presupposition of the greater efficacy of intervening early in the product development process.

Fiksel and Wapman (1994) defined design for environment (DFE) as "the systematic consideration, during new production and process development, of design issues associated with environmental safety and health over the full product life-cycle".

Horvath, Hendrikson, Lave and McMichael (1995) stated three main goals of DFE: (1) minimize the use of non-renewable resources, (2) effectively manage renewable resources, and (3) minimize toxic release to the environment. Mizuki, Snadbond and Pitts (1996) explained that DFE requires the coordination of several design- and databased activities such as environmental impact metrics, data and database management, and design optimization (including cost assessments). The environmental impact metric is defined by Veroutis and Fava (1996) as "an algorithmic interpretation of levels of performance within an environmental criterion". The environmental criterion is the environmental attribute of the product. All of these environmental criteria can be translated into metric, and can be used to assist decision-making when the product is being developed.

All the authors emphasize that designing stage is related closely with the environmental contact. Basically, designing stage is shown to be the most important stage to take environmental impact into account in order to come out with environmental-friendly product or process. Only that Giudice (2006) prefer to consider the whole life cycle of a product give great environmental impact.

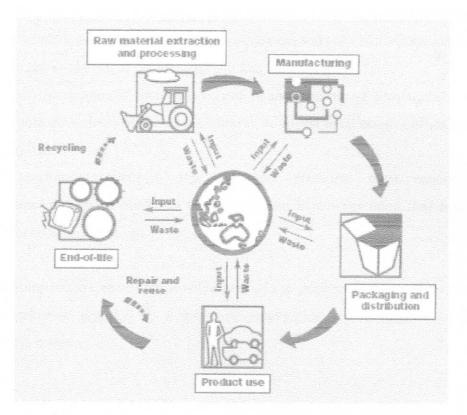

Figure 2.1: Life cycle stages of a typical product and associated environmental impact.

Adapted from Product Innovation The Green Advantage, An Introduction to

Design for Environment for Australian Business

### 2.2.1 Basic principles of DfE

DfE is related closely to technology and the environment. Giudice, La Rosa and Risiano stated that some reflections on the relation between technology and the environment evidence the fundamental principles that can serve as the basis of more effective methodologies for their complete integration:

- (a) The methodologies must be wide-ranging and based on systemic statements.

- (b) The approach must be multidisciplinary; where it must include technical, legal, economic and political aspects.

- (c) Technology plays a key role in the solution of environmental problems; it is therefore necessary to encourage implementation of environmental protection in the evolution of process and product technologies.

- (d) All the economic factors involved in the process of developing industrial products must incorporate a system of environmental constraints as extensive as possible.

- (e) Development policies and legislative pressures must encourage the development of programs of research and experimentation that support the innovations required by these changes.

These principles require the direct involvement of the product design and development process in industrial practice, as a vector of propagation and integration of the new environmental needs

### 2.2.2 DfE strategies

When it comes to strategies, DfE can be implemented using various types of strategies according to company's basis program. Strategies can be refined and developed to suit different products and the organizations and form the basis of a company's DfE program.

Take for example, the National Centre for Design at the Royal Melbourne Institute of Technology (RMIT) has identified a series of DfE strategies to reduce environmental impacts at each stage of the life cycle (see Table 1). The National Centre for design focus more on every steps of the product life cycle to reflect environment into account.

Table 1: DfE strategies

| Product Stage                                   | DfE Strategies                                                                                                                                                                                                                           |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Raw material extraction and processing          | <ul> <li>Design for resource conservation</li> <li>Design for low –impact materials</li> <li>Design for bio-diversity conservation</li> </ul>                                                                                            |

| Manufacturing / Packaging and     Distributions | <ul> <li>Design for cleaner product</li> <li>Design for low-impact packaging</li> <li>Design for efficient distributions</li> </ul>                                                                                                      |

| 3. Product Use                                  | <ul> <li>Design for energy efficiency</li> <li>Design for water conservation</li> <li>Design for minimal consumption</li> <li>Design for low-impact use</li> <li>Design for service and repair</li> <li>Design for durability</li> </ul> |

| 4. End of Life                                  | <ul> <li>Design for reuse</li> <li>Design for re-manufacture</li> <li>Design for disassembly</li> <li>Design for recycling</li> <li>Design for safe disposal</li> </ul>                                                                  |

### 2.2.3 Benefits of DfE

DfE can also provide a means for establishing a long-term strategic vision of a company's future products and operations. In general, DfE is an enabling force to shape more sustainable patterns of production and consumption. Other benefits of