"I / We admit that to have read this report and it has followed the scope and quality in partial fulfillment of requirements for The Bachelor Degree of Electronic Engineering (Computer Engineering)."

Signature Supervisor Name Date

÷

Z 0 :

: En. Nor Zaidi Bin Haron : 5/5/2006

## DESIGN OF FINITE STATE MACHINE MEMORY BUILT-IN SELF TEST

## SITI AISAH BINTI MAT JUNOS @ YUNUS

This Report Is Submitted In Partial Fulfillment of Requirements For The Bachelor Degree of Electronic Engineering (Computer Engineering)

> Faculty of Electronic Engineering and Computer Engineering Kolej Universiti Teknikal Kebangsaan Malaysia

> > **APRIL 2006**

÷.

C Universiti Teknikal Malaysia Melaka

"Hereby the author declares that all the material presented in this thesis to be the effort of the author herself. Any kind of materials that is not the effort of the author has been stated clearly in the references."

Signature

÷

: change

Author Name : Siti Aisah Binti Mat Junos @ Yunus Date : 05/05/2006 Dedicated to:

Mak, Ayah, Adik Ya, Kak Ba, Kak Da, Kak Yah, Abang, family and my beloved friends for giving me unconditional love and caring.....

÷

#### ACKNOWLEDGEMENT

First of all, I would like to thank Allah the All Mighty, which with his bless, I manage to complete this thesis.

I would like to express our greatest gratitude and sincere thanks to my supervisor, Mr. Nor Zaidi Haron, for accepting me as his project student and for his valuable ideas, advice and help in the supervision and discussions of this Final Year Project. In fact, he gave me guidance when obstacles arise throughout this period of time. Once again, I thank him for his tolerance and endeavors.

I am especially grateful to my mother, sister and members of my family, for all their support and understanding along my study. Lastly, my grateful goes to all my colleagues who give me guidance and help in completing this project.

41

## ABSTRACT

v

This project is designing a Design for Test (DfT) technique to test embedded memory called Finite State Machine (FSM) Memory Built–In Self Test (MBIST). The design is written using Very High Speed Integrated Circuit Hardware Design Language, (VHDL) based on the FSM architecture. The architecture will be modelled using Register Transfer Level (RTL) abstraction. A simulation on two testing algorithms is implemented on this architecture. Evaluation on area and testing time of these algorithms are carried out. The area is referring to number of logic gates used to build the circuit. While, the testing time is the completion time for testing the embedded Memory. Lastly, a comparison to Microcode Memory Built–In Self Test (MBIST) architecture evaluation is performed.

4

### ABSTRAK

Projek ini ialah merekabentuk satu Teknik Reka Bentuk untuk Pengujian, (DfT) bagi menguji memori yang terbenam yang dikenali sebagai Terbina dalam Pengujian Sendiri Memori dengan Mesin Keadaan Terhingga (Finite State Machine Memory Built-In Self Test). Rekabentuk ini ditulis menggunakan pembangunan perisian melalui perisian Very High Speed Integrated Circuit Hardware Design Language, (VHDL) berdasarkan senibina Mesin Keadaan Terhingga, (FSM). Senibina projek ini akan dimodelkan menggunakan Peniskalaan Peringkat Pemindahan Daftar, (Register Transfer Level). Dua algoritma pengujian yang diimplementasikan ke atas senibina tersebut adalah untuk proses simulasi. Penilaian ke atas kawasan dan masa pengujian bagi algoritma tersebut akan dilakukan. Kawasan pengujian merujuk kepada bilangan logik get yang digunakan dalam membina litar tersebut. Sementara bagi masa pengujian adalah masa yang diperlukan untuk menyiapkan pengujian memori yang terbenam. Akhirnya, satu penilaian di laksanakan bagi menunjukkan perbezaan dengan teknik senibina Mikrokod bagi Terbina dalam Pengujian Sendiri Memori, (MBIST).

## CONTENTS

## CHAPTER TITLE

## PAGE

| PROJECT TITLE         | i   |

|-----------------------|-----|

| DECLARATION           | ii  |

| DEDICATION            | ш   |

| ACKNOWLEDGEMENT       | iv  |

| ABSTRACT              | v   |

| ABSTRAK               | vi  |

| CONTENTS              | vii |

| LIST OF TABLES        | xi  |

| LIST OF FIGURES       | xii |

| LIST OF ABBREVIATIONS | xiv |

# I INTRODUCTION

| 1.1 | BACK  | GROUND OF PROJECT                            | 1 |

|-----|-------|----------------------------------------------|---|

|     | 1.1.1 | Design for Test, (DfT) Techniques            | 2 |

|     |       | 1.1.1.1 Bed-of Nails and In-Circuit Testing  | 3 |

|     |       | 1.1.1.2 Scan Method                          | 4 |

|     |       | 1.1.1.3 Bulit-In Self Test, (BIST) Technique | 5 |

|     | 1.1.2 | Motivation of BIST versus ATE                | 6 |

| 1.2 | OBJE  | CTIVE OF PROJECT                             | 7 |

| 1.3 | SCOP  | E OF PROJECT                                 | 8 |

| 1.4 | METH  | IOD OF PROJECT                               | 8 |

| 1.5 | SUM   | MARY OF THESIS                               | 9 |

# II LITERATURE REVIEW

| 2.1 | INTRODUCTION |                                           |    |

|-----|--------------|-------------------------------------------|----|

| 2.2 | MEM          | ORY FAULT MODELS                          | 10 |

|     | 2.2.1        | Stuck At Faults Model (SAF)               | 12 |

|     | 2.2.2        | Transition Faults Model (TF)              | 13 |

|     | 2.2.3        | Coupling Fault Model (CF)                 | 14 |

|     |              | 2.2.3.1 Inversion Coupling Faults         | 14 |

|     |              | 2.2.3.2 Idempotent Coupling Faults        | 14 |

|     |              | 2.2.3.3 State Coupling Faults             | 15 |

|     | 2.2.4        | Data Retention Faults (DRF)               | 16 |

| 2.3 | MEM          | ORY TEST PATTERN ALGORITHMS               | 16 |

|     | 2.3.1        | March Patterns                            | 16 |

|     |              | 2.3.1.1 March A                           | 17 |

|     |              | 2.3.1.2 March B                           | 17 |

|     |              | 2.3.1.3 March C                           | 18 |

|     |              | 2.3.1.4 March C -                         | 18 |

|     | 2.3.2        | MATS Patterns                             | 19 |

|     |              | 2.3.2.1 MATS                              | 19 |

|     |              | 2.3.2.2 MATS +                            | 20 |

|     | 2.3.3        | Analysis of the Memory Testing Algorithms | 21 |

| 2.4 | GENE         | TRIC ARCHITECTURE OF MEMORY BIST          | 21 |

| 2.5 | FINIT        | E STATE MACHINE MEMORY BIST               | 23 |

|     | 2.5.1        | Architecture of FSM Memory BIST           | 23 |

|     | 2.5.2        | Concept of FSM based Memory BIST          | 24 |

|     |              | 2.5.2.1 Counters                          | 26 |

| 2.6 | MICR         | OCODE MEMORY BIST                         | 26 |

|     | 2.6.1        | Architecture of Microcode                 | 26 |

|     | 2.6.2        | Microcode Instruction                     | 28 |

| 2.7 | COM          | PARISON BETWEEN FINITE STATE              | 29 |

|     | MACI         | HINE AND MICROCODE MEMORY BIST            |    |

# III METHODOLOGY

| 3.1 | INTRODUCTION                                | 30 |

|-----|---------------------------------------------|----|

| 3.2 | FPGA DESIGN FLOW                            | 32 |

| 3.3 | TOP LEVEL SYSTEM DESIGN                     | 35 |

| 3.4 | SINGLE COMPONENT DESIGN                     | 37 |

|     | 3.4.1 Finite State Machine MBIST Controller | 37 |

|     | 3.4.2 Test Collar                           | 39 |

|     | 3.4.3 Memory Under Test                     | 41 |

| 3.5 | HARDWARE DESCRIPTION LANGUAGE (HDL)         | 41 |

|     | DESIGN ENTRY                                |    |

| 3.6 | BEHAVIOUR SIMULATION                        | 44 |

| 3.7 | DESIGN SYNTHESIS                            | 45 |

|     |                                             |    |

# IV RESULTS AND ANALYSIS

| 4.1 | INTRODUCTION                               |    |  |

|-----|--------------------------------------------|----|--|

| 4.2 | AREA AND SPEED SYNTHESIS SUMMARY           | 47 |  |

|     | 4.2.1 Comparison between March C- and MATS | 47 |  |

|     | Algorithms                                 |    |  |

|     | 4.2.2 Comparison of March C- Algorithm     | 48 |  |

|     | 4.2.3 Comparison of MATS Algorithm         | 50 |  |

| 4.3 | TESTING TIME                               | 51 |  |

|     | 4.3.1 Comparison between March C- and MATS | 51 |  |

|     | 4.3.2 Comparison of March C- Algorithm     | 52 |  |

|     | 4.3.3 Comparison of MATS Algorithm         | 53 |  |

| 4.4 | FAULT FREE SIMULATION WAVEFORM             | 53 |  |

| 4.5 | STUCK AT FAULT SIMULATION WAVEFORM         | 55 |  |

| 4.6 | REGISTER TRANSFER LEVEL SCHEMATIC          | 57 |  |

| 4.7 | SUMMARY                                    | 60 |  |

ix

## V CONCLUSION AND SUGGESTION

4

| 5.1 | CONCLUSION | 61 |

|-----|------------|----|

| 5.2 | SUGGESTION | 63 |

| REI | FERENCES   | 64 |

C Universiti Teknikal Malaysia Melaka

## LIST OF TABLES

NO TITLE

PAGE

| 2.1 | Description of the March A Pattern [5]                           | 17 |

|-----|------------------------------------------------------------------|----|

| 2.2 | Description of the March B Pattern [5]                           | 18 |

| 2.3 | Description of the March C Pattern [5]                           | 18 |

| 2.4 | Description of the March C- Pattern [5]                          | 19 |

| 2.5 | Description of the MATS Pattern [5]                              | 19 |

| 2.6 | Description of the MATS + Pattern [5]                            | 20 |

| 2.7 | Summary of classification for Memory Test Pattern Algorithms [5] | 20 |

| 2.8 | The Six Test Pattern of Algorithms' Fault Coverage               | 21 |

| 2.9 | Comparison of Two Memory BIST Controller                         | 29 |

| 4.1 | Synthesis on Area of Different Algorithm                         | 47 |

| 4.2 | Synthesis on Speed of Different Algorithm                        | 48 |

| 4.3 | Synthesis on Area of March C- Algorithm                          | 49 |

| 4.4 | Synthesis on Speed of March C- Algorithm                         | 49 |

| 4.5 | Synthesis on Area of MATS Algorithm                              | 50 |

| 4.6 | Synthesis on Speed of MATS Algorithm                             | 50 |

| 4.7 | Testing Time between March C- and MATS Algorithms                | 51 |

| 4.8 | Testing Time between FSM and Microcode for March C- Algorithms   | 52 |

| 4.9 | Testing Time between FSM and Microcode for MATS Algorithms       | 53 |

ġ.

C Universiti Teknikal Malaysia Melaka

xi

# LIST OF FIGURES

| NO | TITLE |

|----|-------|

| no | TITLE |

# PAGE

| 1.1  | Scan Path Principle [simplified from 7]                         | 4  |

|------|-----------------------------------------------------------------|----|

| 1.2  | General BIST Architecture [simplified from 5]                   | 5  |

| 1.3  | Basic Principle of Testing [3]                                  | 6  |

| 2.1  | Abstraction Levels for Fault Modeling                           | 11 |

| 2.2  | Abstraction Levels for Fault Modeling                           | 12 |

| 2.3  | Markov Diagram for a Stuck at "0" Cell [5]                      | 13 |

| 2.4  | Markov Diagram of a Transition Faults Model [5]                 | 13 |

| 2.5  | Markov Diagram for a Coupling Fault [5]                         | 15 |

| 2.6  | Memory to Memory BIST Interaction                               | 22 |

| 2.7  | Hardwired- FSM based Memory BIST [8]                            | 23 |

| 2.8  | A Finite State Machine BIST Block Diagram [5]                   | 25 |

| 2.9  | A Microcode BIST Block Diagram [5]                              | 27 |

| 2.10 | Microcode Instruction Control [5]                               | 28 |

| 3.1  | Method of Implemented the Full of Project                       | 31 |

| 3.2  | FPGA Design Flow Block Diagram [10]                             | 32 |

| 3.3  | Design Entry Flow Block Diagram                                 | 33 |

| 3.4  | Design Synthesis and Design Implement Flows Block Diagram       | 34 |

| 3.5  | The Entire of Memory BIST Block Diagram                         | 36 |

| 3.6  | The Signal in FSM Memory BIST Controller Block Diagram          | 38 |

| 3.7  | (a) The example of Pass Cycle and (b) The example of Fail Cycle | 39 |

| 3.8  | The Flows Chart of the Test Collar Designing                    | 40 |

| 3.9  | Top Level System Design in Module View Xilinx ISE        | 42 |

|------|----------------------------------------------------------|----|

| 3.10 | The Example of Behavioral Architecture Design Entry      | 43 |

| 3.11 | The Process of Simulation in Xilinx ISE Software         | 44 |

| 3.12 | The Properties of Synthesis in Xilinx ISE Software       | 45 |

| 4.1  | FSM Memory BIST Testing Faults Free SRAM in Normal Mode  | 54 |

| 4.2  | FSM Memory BIST Testing Faults Free SRAM in BIST Mode    | 55 |

| 4.3  | FSM Memory BIST Testing Stuck At Fault SRAM at Address 3 | 56 |

| 4.4  | FSM Memory BIST Testing Stuck At Fault SRAM at Address 5 | 56 |

| 4.5  | Entity MATS Algorithm Design                             | 57 |

| 4.6  | MATS Algorithm Block Diagram                             | 58 |

| 4.7  | Behavioral MATS Architecture in VHDL codes               | 58 |

| 4.8  | (a) MATS Block Diagram Design Hierarchy                  | 59 |

|      | (b) MATS Interpretation into Gate Logic                  | 59 |

|      |                                                          |    |

.

## LIST OF ABBREVIATIONS

| ATE   | ÷.,            | Automatic Test Equipment       |

|-------|----------------|--------------------------------|

| BIST  | -              | Built-In Self Test             |

| CE    |                | Chip Enable                    |

| CF    | -              | Coupling Faults                |

| CUT   | -              | Circuit Under Test             |

| DfT   | - :            | Design for Test                |

| DRF   | ÷              | Data Retention Faults          |

| FPGA  | 4              | Field Programmable Gate Array  |

| FSM   |                | Finite State Machine           |

| HDL   | 4              | Hardware Description Language  |

| IC    |                | Integrated Circuit             |

| LFSR  | 40             | Linear Feedback Shift Register |

| MBIST | -              | Memory Built-In Self Test      |

| MUT   |                | Memory Under Test              |

| MUX   | -              | Multiplexer                    |

| OE    | -              | Read Enable                    |

| PCB   | - <del>.</del> | Printed Circuit Board          |

| RAM   | -              | Random Access Memory           |

| ROM   | -              | Read Only Memory               |

| RTL   |                | Register Transfer Level        |

| SAF   | -              | Stuck At Faults                |

| SoC   | ÷.             | System on Chip                 |

| SRAM  |                | Static Random Access Memory    |

|       |                |                                |

| TF   | - | Transition Faults                                       |

|------|---|---------------------------------------------------------|

| VHDL | - | Very High Speed Integrated Circuit Hardware Description |

|      |   | Language                                                |

| WE   | ÷ | Write Enable                                            |

1.2

### **CHAPTER I**

#### INTRODUCTION

Chapter 1 starts with the background of the project. It is followed by objectives and scope of the project. The overview method of project is presented in fourth part and lastly summary of the thesis is described.

### 1.1 BACKGROUND OF PROJECT

Design for Test, (DfT) is a philosophy to overcome the complete product testing problem. Built-In Self Test, (BIST) is the one of technique used in this philosophy. According to the Memory Built-In Self Test, (MBIST) technique, the embedded memories becoming a major part in System on Chip (SoC). The density of this component is bigger and larger to due the number of data to be stored. However, the increase in circuit complexity was because the embedded memories testing more challenging. Among the problem encountered while testing the memories are:

C Universiti Teknikal Malaysia Melaka

- Controllability of the logic elements problem. The Controllability is to produce any desired values on the internal signal of the circuit by applying an appropriate test vector input combination to the primary inputs.

- ii) Observability of the logic elements problem. The observability is any internal signal can be propagated to a primary output for comparison with an expected value by the application of an appropriate primary input combination.

- iii) Insufficient fault coverage in the embedded memory testing.

- iv) The increasing testing data to be stored and analysed.

- v) New sophisticated and expensive testers are needed to test the embedded memory.

- vi) Tomorrow's memories cannot be tested by today's testers. New version of memories one invented everyday. The tester cannot cope with the new fault that might be occurred.

### 1.1.1 Design for Test, (DfT) Techniques

Design for Test is a design philosophy which suggests that the problem of testing complex circuit can be improved. DfT technique range from a simple set of guide lines to a formal set of design rules [1]. The objective of developing DfT methods are to facilitate the testing of complex sequential circuits. The purpose of testing is to ensure before fabrication, the circuit behavior satisfies the intent of the designer which is free from functional or logical design errors and to detect faulty devices after fabrication. It is also can improve the IC testability in terms of controllability, observability and predictability of signal values on nodes inside the circuit [6]. The evolutions of test methods for embedded memories are:

- i) Bed-of Nails and In-Circuit Testing

- ii) Scan Method

- iii) Built-In Self Test, (BIST) Technique

#### 1.1.1.1 Bed-of Nails and In-Circuit Testing

Digital circuits that are fabricated on a single PCB, observability is obtained by using every pin of every IC as a test point. This is achieved by building a special test fixture that matches the layout of the PCB and contains a spring-loaded pin (nail) at each IC-pin position. The PCB is placed on this bed of nails, and the nails are connected to an automatic tester that can monitor each pin as required by a test program. Disadvantage of this technique are [7]:

- The rise of high density surface mount packaging has made Bed-of Nails Testing more difficult. Components may be mounted on both sides of the PCB; a special test fixture called a clamp shell may be needed to connect nails to both sides of the PCB.

- The pins of many surface mount devices are so small and their spacing is so tight (25 mils or less), that it may be impossible to reliably land a test pin on them.

### 1.1.1.2 Scan Method

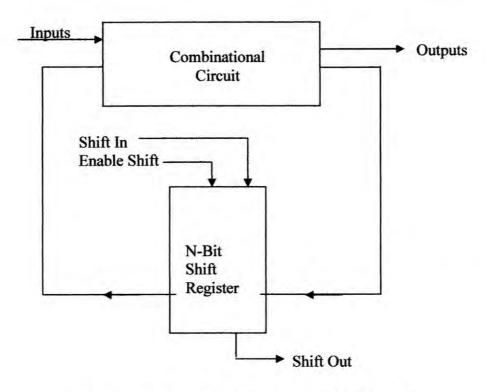

A scan method attempts to control and observe the internal signals of a circuit using only a small number of test points [7]. It is consider as any digital circuit to be a collection of flip-flops or other storage elements interconnected by combinational logic and is concerned with controlling and observing the state of the storage elements. It does this by providing two operation modes: a normal mode and a scan mode in which all of storage elements are reorganized into a giant shift register. In scan mode, the state of the circuit and storage elements can be read out by n shifts (observability), and a new state can be loaded at the same time (controllability). Figure 1.1 illustrates this scan method circuitry.

Figure 1.1: Scan Path Principle [simplified from 7].

÷

#### 1.1.1.3 Built-In Self Test, (BIST) Technique

Built-In Self Test, or BIST, is the technique of integrate the functionality of an automatic test system onto a chip. BIST is a design for testability Design for Test, (DfT) technique in which testing (test generation and test application) is accomplished through built in hardware features [5].

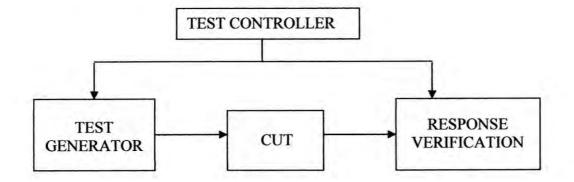

The general BIST architecture is a BIST test controller which controls the BIST circuit, test generator which generates the test address sequence, response verification as a comparator which compares the memory output response with the expected correct data and Circuit Under Test (CUT) as shown in Figure 1.2.

The BIST controller can be implemented by either hardwired logic in the form of a Finite State Machine (FSM), microcode controller or processor-based.

Figure 1.2: General BIST Architecture [simplified from 5].

. . .

5

#### 1.1.2 Motivation of BIST versus ATE

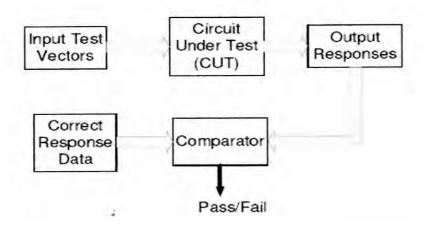

There are two main approaches for testing embedded memories: external test by direct access using Automatic Test Equipment, (ATE) and internal testing using Built-In Self Test (BIST). When external testing is employed, the input test vectors and correct response data are stored in the ATE memory. For external testing, the comparison is carried out on the tester.

ATE limitations make BIST technology an attractive alternative to external test for complex chips. BIST is a Design for Test (DfT) method where part of the circuit is used to test the circuit itself where the test vectors are generated and test responses are analyzed on-chip.

ATE, as well as very long testing time since tester channels are timeshared by different memories under test. On the other hand, BIST provides at-speed and highbandwidth access to the embedded memory cores and it only needs a low cost to initialize the test sessions and to inspect the final results either status bits pass or fail. However, although BIST is may induce excessive power, in addition to performance and area overhead [3].

Figure 1.3: Basic Principle of Testing [3].

(C) Universiti Teknikal Malaysia Melaka

The advantages of the BIST compared to ATE are:

- i) Provides efficient testing of the embedded components and interconnections.

- ii) Permit circuits to be tested at speed.

- iii) Reduce the test time and cost the large size of embedded memory.

- iv) Reduce the volume of test data.

- v) Better fault coverage, special test structures can be incorporated onto the chips.

- vi) Produce an alternative to costly Automatic Test Equipment, (ATE).

- vii) Well designed testing, the same hardware can test chips, boards and system.

### **1.2 OBJECTIVE OF PROJECT**

The objectives of the project are:

- i) To Study Design for Test (DfT) techniques to test embedded memory.

- Learn the way to design a logic circuit using Very High Speed Integrated Circuit Hardware Description Language (VHDL) software.

- iii) To Design Finite State Machine (FSM) Memory Built-In Self Test (MBIST) using VHDL.

- iv) To simulate, synthesis and verify the design.

12

v) To evaluate the area and time based on the implementation of the algorithms.

#### **1.3 SCOPE OF PROJECT**

There are the scopes of the project:

- Software-based project which is to design FSM Memory BIST architecture for testing embedded memory.

- ii) Implementation of two memory testing algorithms as FSM Memory controller.

- iii) Evaluation the area and time based on the implementation of the algorithms.

- iv) Target completion is simulation on fault SRAM Memory.

### 1.4 METHOD OF PROJECT

Several steps are gone through in completing this design. Firstly, make some study is made understood the overall specification of the project. Reading on the past journals and books is done to gain the knowledge for achieving the objectives.

By referring the information and data obtained through the study, the overall functional block diagram of the Finite State Machine controller is sketched using the top-down level design. This is a design technique that starts with the highest level of an idea to block diagram and works its way down the single component in block diagram. From that, the state diagram of the algorithms FSM controller is derived and translated in VHDL programming. The VHDL program is checked it syntax to ensure error free.

After that, the program is simulated by testing fault SRAM Memory to verify the functionality of the design. Lastly, the designs are synthesised its area and time testing