# A STUDY ON CURRENT CARRYING CAPACITY OF DOUBLE LAYER PCB

### MOHD AMIRUL FARUQI BIN ISMAIL

# BACHELOR OF ELECTRICAL ENGINEERING (INDUSTRIAL POWER)

2<sup>nd</sup> JULY 2012

" I hereby declare that I have read through this report entitle "A Study on Current Carrying Capacity of Double Layer PCB" and found that has comply the partial fulfillment for awarding the degree of Bachelor of Electrical Engineering (Industrial Power)"

| Signature         | : |  |

|-------------------|---|--|

| Supervisor's name | : |  |

| Date              | : |  |

### A STUDY ON CURRENT CARRYING CAPACITY OF DOUBLE LAYER PCB

MOHD AMIRUL FARUQI BIN ISMAIL

A report submitted in partial fulfillment of the requirements for the degree of Electrical Engineering (Industrial Power)

> Faculty of Electrical Engineering UNIVERSITI TEKNIKAL MALAYSIA MELAKA

> > JUN 2012

C Universiti Teknikal Malaysia Melaka

I declare that this report entitle "A Study on Current Carrying Capacity of Double Layer PCB" is the result of my own research except as cited in the references. The report has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | : |  |

|-----------|---|--|

| Name      | : |  |

| Date      | : |  |

To my beloved mother and father

#### ACKNOWLEDGEMENT

Firstly, I praise to my gratitude to God for lending me a good health and patience to face all the difficulties that occurred during completed my bachelor degree final year project.

Subsequently, I would like to take this opportunity to express my sincere appreciation to my supervisor, Miss Arfah Binti Ahmad for her continuous guidance and supports, significant suggestions and critiques as well as for being an excellent supervisor. I am really appreciated very much on what she has done and a million thanks to her.

After that, I also wish to acknowledge the contributions and valuable advice provided by my lectures, who have taught me over the years in Universiti Teknikal Malaysia Melaka (UTeM). They have given me the basic principle of Electrical Engineering, and this invaluable knowledge has provided me a firm foundation for doing this project.

To my beloved family, I would like to forward my grateful to them for their continuous support during my study period, their tolerance and kindness. Finally, I would like to thank everyone who has contributed during my First Bachelor Degree final year project. This project would have been a much more difficult without their patience, guidance and flexibility.

#### ABSTRACT

This project is related with analyzing current carrying capacity (CCC) of a double layer PCB by using statistical approach. In recent years, the design of printed circuit board (PCB) current carrying capacity such as laptop has become increasingly dense with miniaturization of electronic packing. Hence, it is important to design PCB traces for this purpose. The aim of this project is to determine factors that influence current carrying capacity and thermal dissipation and the relation between these variables. This project focuses the double layer of PCB, current injection on traces, traces width, and traces bended corner. The fixed factors are length and room temperature. For the PCB design, PCB Express software was used to ease and save time for the process of designing the width and angle of the desired traces in this study. After the PCB design has been made, that PCB would undergo the process of etching to remove excess traces etching that are not used on the board. Since for the experiment, the current was injected into the PCB traces, after 10 minutes then the temperature of that PCB traces to be stable and the data will be captured using the FLIR Thermal Imager. To ensure that data is accurate, these data taken as 5 times for each PCB traces. Temperature rises on PCB due to a few parameters where some parameters have no significant impact on the temperature rise. It describe about correlations between electrical current and temperature rise of the trace. When there is temperature rise due to distribution and heat dissipation during the flow of current in the PCB traces, this may cause PCB fails to operate normally and causing damage to the PCB operations.

#### ABSTRAK

Projek ini berkaitan dengan mengkaji keupayaan pengaliran arus (CCC) bagi dua lapisan papan litar bercetak (PCB) dengan menggunakan pendekatan statistik. Sejak beberapa tahun kebelakangan ini, reka bentuk PCB seperti komputer riba telah menjadi semakin padat dengan pengecilan saiz dan kepadatan elektronik. Oleh itu, ia adalah penting untuk merekabentuk pengalir PCB bagi tujuan tersebut. Tujuan projek ini adalah untuk menentukan faktor-faktor yang mempengaruhi keupayaan pengaliran arus dan kelesapan haba serta hubungan antara pembolehubah-pembolehubah ini. Projek ini tertumpu kepada dua lapisan PCB, arus masukan pada pengalir, kelebaran pengalir, dan sudut pengalir. Faktor-faktor yang tetap pula adalah panjang pengalir dan suhu bilik. Untuk reka bentuk PCB pula, perisian PCB Express digunakan untuk memudahkan dan menjimatkan masa untuk proses mereka-bentuk kelebaran dan sudut pengalir yang diingini dalam kajian ini. Selepas reka bentuk PCB telah dibuat, PCB tersebut akan menjalani proses goresan untuk membuang pengalir-pengalir lebihan yang tidak digunakan atas papan. Ketika eksperimen, arus akan dialirkan ke pengalir pada PCB. Selepas 10 minit, suhu pada pengalir pada PCB akan stabil dan data akan diambil menggunakan FLIR Thermal Imager. Untuk memastikan yang data adalah tepat, data perlulah diambil sebayak 5 kali untuk setiap pengalir pada PCB. Kenaikan suhu pengalir pada PCB adalah disebabkan oleh beberapa parameter dan beberapa parameter juga tidak memberi kesan kepada kenaikan suhu pengalir. Ia menghuraikan tentang hubung kait diantara arus elektrik dan kenaikan suhu pengalir. Apabila terdapat kenaikan suhu disebabkan pengagihan dan kelesapan haba semasa aliran arus yang melalui pengalir PCB, ini boleh menyebabkan PCB gagal untuk beroperasi seperti biasa dan mengakibatkan kemusnahan bagi operasi PCB.

## TABLE OF CONTENTS

| CHAPTER | TITI | LE                                              | PAGE     |

|---------|------|-------------------------------------------------|----------|

|         | ACK  | NOWLEDGEMENT                                    | ii       |

|         | ABS  | TRACT                                           | iii      |

|         | TAB  | LE OF CONTENTS                                  | v        |

|         | LIST | <b>COFFIGURES</b>                               | viii     |

|         | LIST | <b>FOF TABLES</b>                               | ix       |

|         | LIST | <b>COF APPENDICES</b>                           | X        |

| 1       | INT  | RODUCTION                                       | 1        |

|         | 1.1  | Background                                      | 1        |

|         | 1.2  | Problem statement                               | 2        |

|         | 1.3  | Objectives                                      | 2        |

|         | 1.4  | Scopes                                          | 3        |

| 2       | LITI | ERATURE REVIEW                                  | 4        |

|         | 2.1  | Introduction                                    | 4        |

|         | 2.2  | New correlations between electrical current and | 5        |

|         |      | temperature rise in PCB traces                  | 3        |

|         |      | 2.2.1 FR-4 base material PCB                    | 5        |

|         |      | 2.2.2 Traces on ceramics substrate              | 6        |

|         |      | 2.2.3 Trace thickness other than $35\mu m$      | 7        |

|         | 2.3  | On current carrying capacities of PCB traces    | 7        |

|         | 2.4  | Thermal design guideline of PCB traces under I  | DC 8     |

|         |      | and AC current                                  | 0        |

|         |      | 2.4.1 Improvement of PCB trace thermal designed | gn<br>10 |

|         | o -  | guideline                                       | 10       |

|         | 2.5  | Current carrying capacity                       | 12       |

|         | 2.6  | Literature review discussion                    | 14       |

| CHAPTER |     |        | Т                       | ITLE                                                   | PAGE |

|---------|-----|--------|-------------------------|--------------------------------------------------------|------|

| 3       | MET | THODO  | DLOGY                   |                                                        | 15   |

|         | 3.1 | Introd | uction                  |                                                        | 15   |

|         | 3.2 | Metho  | dology chart            |                                                        | 15   |

|         |     | 3.2.1  | Method 1: Fin           | nd source and study                                    | 16   |

|         |     | 3.2.2  | Method 2: De            | esign PCB                                              | 16   |

|         |     | 3.2.3  | Method 3: Ex            | periment and data capture                              | 17   |

|         |     | 3.2.4  | Method 4: Re            | sult, analysis and discussion                          | 19   |

| 4       | RES | ULTS A | AND ANALYS              | SIS                                                    | 20   |

|         | 4.1 | Introd | uction                  |                                                        | 20   |

|         | 4.2 | Exper  | imental results         |                                                        | 20   |

|         |     | 4.2.1  | Results captu           | red for varied width                                   | 20   |

|         | 4.3 | Data a | nalysis                 |                                                        | 21   |

|         |     | 4.3.1  | Analysis of te          | emperature rise ( $\Delta T$ ), current                | 21   |

|         |     |        | ( <i>I</i> ), and width | (A) for straight line                                  | 21   |

|         |     | 4.3.2  | Regression ar           | alysis for straight line copper                        | 22   |

|         |     |        | trace                   |                                                        |      |

|         |     |        | 4.3.2.1 Reg             | gression analysis: <i>ln</i> ( <i>I</i> ) Vs <i>ln</i> | 23   |

|         |     |        | (A)                     | , $ln (\Delta T)$                                      | 23   |

|         |     | 4.3.3  | Analysis of c           | urrent (I), temperature rise                           | 25   |

|         |     |        | $(\Delta T)$ , and wid  | th $(A)$ for bended corner                             | 23   |

|         |     | 4.3.4  | Regression ar           | alysis for bended corner                               | 27   |

|         |     |        | copper trace            |                                                        | 21   |

|         |     |        | 4.3.4.1 Reg             | gression analysis: ln (I) Vs ln                        | 27   |

|         |     |        | (A)                     | , $ln(\Delta T)$                                       | 21   |

|         |     | 4.3.5  | Analysis after          | transformation data for                                | 30   |

|         |     |        | bended corne            | r                                                      | 50   |

|         |     |        | 4.3.5.1 Reg             | gression analysis: $ln(\sqrt{I})$ Vs $ln$              | 30   |

|         |     |        | (A)                     | , $ln (\Delta T)$                                      | 50   |

|         |     | 4.3.6  | The regressio           | n model equation                                       | 32   |

|         |     |        |                         | del equation for straight line per trace               | 32   |

vi

| CHAPTER |      | TITLE                                                 | PAGE |

|---------|------|-------------------------------------------------------|------|

|         |      | 4.3.6.2 Model equation for bended corner copper trace | 34   |

| 5       | CON  | <b>ICLUSION AND RECOMMENDATION</b>                    | 36   |

|         | 5.1  | Introduction                                          | 36   |

|         | 5.2  | Conclusion                                            | 36   |

|         | 5.3  | Recommendation                                        | 38   |

| REFERE  | NCES |                                                       | 39   |

| APPEND  | ICES |                                                       | 40   |

## LIST OF TABLES

| TABLE | TITLE                                                       | PAGE |

|-------|-------------------------------------------------------------|------|

| 2.1   | Calculated current $I$ leading to a mean temperature $T[2]$ | 6    |

### LIST OF FIGURES

| FIGURE | TITLE                                                                   | PAGE |

|--------|-------------------------------------------------------------------------|------|

| 2.1    | K-chart for PCB characteristics                                         | 4    |

| 2.2    | Mean temperature of a trace (in $20^{\circ}C$ ambient) [3]              | 6    |

| 2.3    | Identified current for external conductor sizing chart [2]              | 9    |

| 2.4    | Identified cross-sectional area for external conductor sizing chart [2] | 9    |

| 2.5    | Heat transfer in double-layer PCB [4]                                   | 10   |

| 2.6    | Heat transfer in multi-layer PCB [4]                                    | 10   |

| 2.7    | Infrared thermal picture [4]                                            | 11   |

| 3.1    | Flow chart                                                              | 15   |

| 3.2    | Bended corner PCB                                                       | 16   |

| 3.3    | Straight line PCB                                                       | 17   |

| 3.4    | Fluke multimeter                                                        | 18   |

| 3.5    | FLIR thermal imager                                                     | 18   |

| 3.6    | DC power supply                                                         | 19   |

| 4.1    | Data captured for straight line                                         | 21   |

| 4.2    | 3-D surface plot for straight line                                      | 22   |

| 4.3    | Minitab output for straight line                                        | 23   |

| 4.4    | Normal probability plot of residuals                                    | 25   |

| 4.5    | Data captured for bended corner                                         | 26   |

| 4.6    | 3-D graph for bended corner                                             | 26   |

| 4.7    | Minitab output for bended corner                                        | 27   |

| 4.8    | Normal probability plot for bended corner                               | 29   |

| 4.9    | Minitab output for bended corner                                        | 30   |

| 4.10   | Normal probability plot for bended corner                               | 32   |

| 4.11   | Estimated current                                                       | 33   |

| 4.12   | Percent relative error                                                  | 34   |

| 4.13   | Estimated current for bender corner                                     | 35   |

| 4.14   | Percent relative error                                                  | 35   |

## LIST OF APPENDICES

| APPENDIX | TITLE                           | PAGE |

|----------|---------------------------------|------|

| А        | Data captured for straight line | 40   |

| В        | Data captured for bended corner | 41   |

| С        | MINITAB software                | 44   |

|          |                                 |      |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Background

Electronic circuits manufacturing is generally manufactured through the use of PCB (Printed Circuit Board). The bare boards are made from glass reinforced plastic with copper tracks in the place of wires. Fundamentally, current carrying capacity is maximum current that can be continuously carried without causing permanent deterioration of electrical properties of a device or conductor. Damage to a PCB track may finally happen if trace is uncovered to a higher temperature than its limit. Temperature rise is basically important in making a guideline for PCB design. Current carrying capacity is the maximum quantity of electrical current a conductor or device can carry before sustaining immediate or progressive decrease. Also described as current rating or ampacity, is the root mean square (rms) electric current which a device can constantly carry while residual within its temperature rating [1].

This study is to confirm and develop an equation that can be used in predict the current carrying capacity of double layer PCB. Mathematical approach for example the linear regression analysis is one of the methods used in this study. To solve this analysis properly, the parameters that complete and appropriate are required. On the other hand, this method is not possible to resolve the problem of temperature rise on the PCB which involves a complex geometry, loading and material properties. Additionally, an infinite number of locations on the PCB are valid for this method. Hence, alternative methods are required for data analysis technique such as linear regression analysis.

1

#### **1.2 Problem statement**

Based on what has been described in previous studies, the current carrying capacity of double-layer PCB has a number of parameters that have been identified. Temperature rise on the PCB is also due to this parameter. Though, there are several parameters that do not have a significant impact of this temperature rise. Parameters can be considered as fixed values or can be ignored in this study. Consequently, to find out the critical parameters that affect the rise in temperature, the experiment is necessary.

According to the journal by L. Yun, entitled "On current carrying capacities of PCB traces," the current carrying capacity is directly comparative to square root of the trace thickness, and the roughly is directly comparative to the square root of the acceptable temperature rise [2]. When the current is higher than its rated current of PCB traces, damage may happen and operation immediately stop working. In recent years, the industries require for PCB tracks that can withstand higher power density and temperature rise has been increased. To make possible that PCB can withstand a higher power density and temperature rise, a few parameters that need to be considered such as the width, thickness, bended line, injected current or current carrying capacity, the maximum temperature of the PCB that can withstand and so on. Besides that, the temperature rise generated from power loss of copper traces. By analyzing the temperature rise on the current carrying conductor of PCB, a failure on the PCB of an electronics device can be minimized. Hence, an experiment is required to decide the parameters that influence the temperature rise on PCB.

#### 1.3 Objectives

There are three objectives that should to be achieved to complete this project:

- 1. To evaluate heat distribution and dissipation of current carrying capacity of doublelayer PCB.

- 2. To determine parameters that influences the current carrying capacity double-layer PCB.

3. To use statistical approach in analyzing data from experiment to generate model equation for double-layer PCB.

#### 1.4 Scopes

This study only focuses on double-layer PCB. The material of double-layer PCB is FR4 as its basic material. Double-layer PCB sizes according to PCB manufacturer sold in the market that is 6 inches (width) x 11 inches (length). To discover the relationship between current and temperature rise, two parameters has been identified that are the copper width and bend angle of copper trace. For trace width used is set according to the earlier studies that are 0.06 inches, 0.08 inches, and 0.10 inches. There are two types of copper trace to be studied that are straight line and bend angle.

For the bend angle trace, the angle used is 120°, 140°, and 160° with the same width (0.06, 0.08, 0.10 inches) respectively. The parameters have a fixed value such as the trace length (6 inches), room temperature (24°C) and the space between the trace (0.4 inches). Minitab is statistical software that will be used to analyze the data that had been taken during the experiment. FLIR Imager is used to capture the thermal data.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Introduction

This chapter state about the literature review for this project. For the overall view, it is about the past study by the people or who has doing the research about the Current Carrying Capacity (CCC).

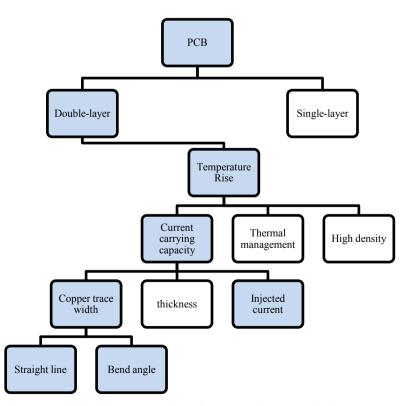

Figure 2.1 shows the K-chart for characteristics of the PCB. It consists of doublelayer and single-layer. For this study, a double-layer PCBs will be more emphasized. For double-layer PCB, affecting the temperature rise is as current carrying capacity, thermal design, and high density.

Figure 2.1: K-chart for PCB characteristics

#### 2.2 New correlations between electrical current and temperature rise in PCB traces

A correlation between electrical current and temperature rise in PCB copper traces is significant to consistently expect the current carrying capacity of a PCB according to a journal written by J. Adam [3]. This journal described about to reproduce the graphs in design rule IPC-2221 by using numerical model calculations and to evaluation it critically and to calculate current-temperature correlations. A number of parameters that influence the new correlation between electrical current and temperature rise that is:

- 1. FR-4 base material PCB

- 2. Traces on ceramics substrate

- 3. Trace thickness other than  $35\mu m$

#### 2.2.1 FR-4 base material PCB

From the paper, the base material is FR-4, the copper layers PCB thickness is 1.6 mm, and trace thickness is 35  $\mu$ m exceed over the PCB totally. Ambient temperature is 'still air' (free convection) with 20 °C. The thickness and location of added copper layers is indicated in the place in of the diagrams and is forced by typical application requirements to PCB manufacturers.

It can be seen obviously, that the board of the copper is restricted, the lower temperature is detected, or, higher acceptable time. To make the comparison more clearly, the current values of some design to the 35  $\mu$ m effects of 2 mm width and 10 mm and the temperature rise is 20 Kelvin as given in Table 2.1:

| Scenario | Current, <i>I</i> (∆ <i>T</i> =20 K) | Current, $I (\Delta T = 20 \text{ K})$ |

|----------|--------------------------------------|----------------------------------------|

| Scenario | w=2mm                                | <i>w</i> =10mm                         |

| 1        | 4.0 A                                | 12.6 A                                 |

| 2        | 5.7 A                                | 18.7 A                                 |

| 3        | 5.5 A                                | 17.0 A                                 |

| 4        | 7.4 A                                | 21.0 A                                 |

| 5        | 8.4 A                                | 23.6 A                                 |

| 6        | 7.0 A                                | 20.6 A                                 |

| 7        | 7.2 A                                | 22.6 A                                 |

Table 2.1: Calculated current *I* leading to a mean temperature *T* [3]

#### 2.2.2 Traces on ceramics substrate

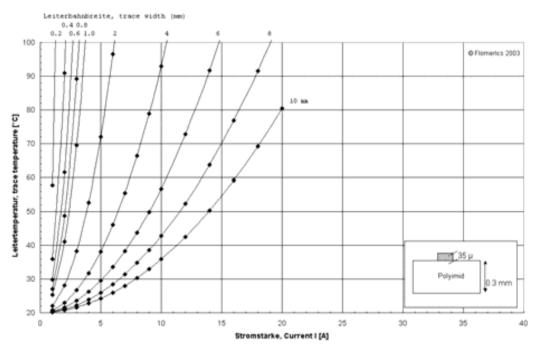

Figure 2.2, shows the results for traces on a thin (0.3mm) substrate, such as a polyimide film. While this is not an accurate representation of a flex-circuit, these calculations shown that the thinner the substrate, the lower is the current-carrying capacity.

Figure 2.2: Mean temperature of a trace (in 20°C ambient) [3]

C Universiti Teknikal Malaysia Melaka

#### 2.2.3 Trace thickness other than 35µm

The power and the track of the trace can determine the temperature for a given PCB structure. It deposits the same power and obtains the same temperature rise and provides the trace width remains the same when added double thickness and increase the current. This scaling law for trace thickness except 35  $\mu$ m can be written as:

$$\frac{1}{35\mu * w} \cdot I_{35\mu}^2 = \frac{1}{tw} I^2$$

(2.1)

where, w =trace width

t = trace thickness  $35\mu =$  constant

#### 2.3 On current carrying capacities of PCB traces

In this paper, the current carrying capacity is limited due to temperature rise. For that reason, to design PCB, a few parameters that influence of temperature rise is should be identified. There are many variables that may have a significant impact on the PCB current carrying capacity. Several of those are:

- i. Number of traces that are involved in current carrying

- ii. Trace division, or field

- iii. System cooling conditions

- iv. Presence or absence of the ground and/or power copper plane

- v. PCB size and thickness [2]

The temperature difference across the PCB thickness is usually very small. Thus, the conductor trace location beside the PCB thickness has very small impact on its current carrying capacity, and there should not be any derating factor for internal traces in their current carrying capacities. So, the location of a conductor trace along the PCB length does have impact. The trace located at the boundary of a PCB will have a (generally about 20%) lower current carrying capacity than the trace at the center [2].

#### 2.4 Thermal design guideline of PCB traces under DC and AC current

Founded on this journal, a thermal design guideline is very important to predict the current carrying capacity. There are previous guidelines that influences temperature rise on copper traces for example multi layers, corner effects and high frequency current their use.

The first standard chart is IPC-2221 but its main drawbacks are the sizing chart to determine PCB trace area. For sure temperature rise is fully depends on conductor cross sectional areas while other varied influences was ignored. Other drawbacks of IPC-2221 design guidelines are [4]:

- i. Small copper content in the test board. The measured data acquired is conservative if applied to PCB with same size but higher copper content.

- ii. Supposition that CCC of internal trace is purely 50% of an external area is oversimplified and erroneous.

- iii. Trace temperature rise is separately related to cross-section area of traces and for this reason, unreliable convection effect caused by different trace faces on CCC is ignored [4].

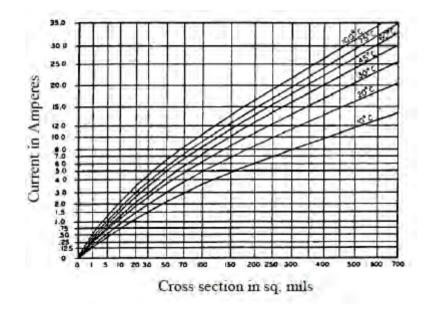

Figure 2.3 shows when the current and the desired temperature rise are identified, then the trace width can be calculated for various trace thicknesses. A 10°C rise is a general temperature rise for a design. The temperature rise must always be minimized. If the designer can manage a 1°C rise or less, then the contribution to board heating will be minimized. Increasing the size of a trace lowers the temperature rise, lowers the voltage drop, decreases component temperatures, and improves the consistency of the product [2].

Figure 2.3: Identified current for external conductor sizing chart [2]

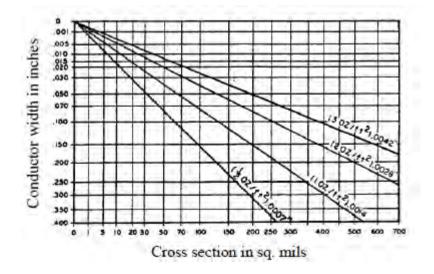

Figure 2.4 shows if a trace size is identified, the temperature rise or the current can be determined. The temperature rise can be predictable only in the range among the curves of constant temperature rise. The current can be predictable if the temperature rise is given [2].

Figure 2.4: Identified cross-sectional area for external conductor sizing chart [2]

C Universiti Teknikal Malaysia Melaka

#### 2.4.1 Improvement of PCB trace thermal design guideline

That concluded current carrying capacity results with large trace spacing, M are optimizing for the design. Improvement on current are suggested:

i. Trace spacing, M

Smaller M is a better representative for modern PCB. Corresponding results give an inherent safety margin due to presence of clearance area between traces.

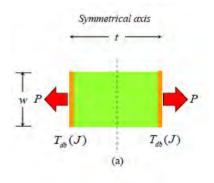

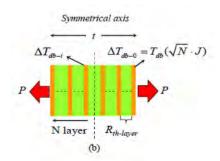

Suppose that traces with current density  $J_0$  produce a loss power P on a doublelayer PCB and loss power P dissipates into ambient totally from the trace surface as shows in Figure 2.5. If traces with the same current density J in each trace in multi-layered PCB produce together the same total of loss power P, totally flowing out of the trace surface as shows in Figure 2.6, the temperature rises of the external traces in both sides must be the same. Red arrow show that heat transfer exits [4].

Figure 2.5: Heat transfer in double-layer PCB [4]

Figure 2.6: Heat transfer in multi-layer PCB [4]

C Universiti Teknikal Malaysia Melaka