# A STUDY ON ISOLATION PERFORMANCE OF PIN DIODE WITH DEFECTED GROUND STRUCTURE (DGS) FOR RF SWITCH

CHAN SIEW YIEN

This report is submitted in partial fulfillment of the requirement for the award of Bachelor of Electronic Engineering (Wireless Communication) With Honors

Faculty of Electronic and Computer Engineering Universiti Teknikal Malaysia Melaka

MAY 2011

i

| FAKULTI K                                           | UNIVERSTI TEKNIKAL MALAYSIA MELAKA<br>EJURUTERAAN ELEKTRONIK DAN KEJURUTERAAN KOMPUTER<br>BORANG PENGESAHAN STATUS LAPORAN<br>PROJEK SARJANA MUDA II                                                |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | OY ON ISOLATION PERFORMANCE OF PIN DIODE<br>DEFECTED GROUND STRUCTURE (DGS) FOR RF<br>H                                                                                                             |

| Sesi Pengajian : 2010/20                            | 11                                                                                                                                                                                                  |

| syarat kegunaan seperti berikut:                    | CHAN SIEW YIEN<br>Projek Sarjana Muda ini disimpan di Perpustakaan dengan syarat-<br>niversiti Teknikal Malaysia Melaka.                                                                            |

| 2. Perpustakaan dibenarkan me                       | embuat salinan untuk tujuan pengajian sahaja.                                                                                                                                                       |

| 3. Perpustakaan dibenarkan me                       | embuat salinan laporan ini sebagai bahan pertukaran antara institusi                                                                                                                                |

| pengajian tinggi.                                   |                                                                                                                                                                                                     |

| 4. Sila tandakan ( $$ ):                            |                                                                                                                                                                                                     |

| SULIT*                                              | (Mengandungi maklumat yang berdarjah keselamatan atau<br>kepentingan Malaysia seperti yang termaktub di dalam AKTA<br>RAHSIA RASMI 1972)<br>(Mengandungi maklumat terhad yang telah ditentukan oleh |

| TERHAD*                                             | organisasi/badan di mana penyelidikan dijalankan)                                                                                                                                                   |

| TIÐAK TERHAD                                        |                                                                                                                                                                                                     |

|                                                     | Disahkan oleh:                                                                                                                                                                                      |

| CRAA                                                |                                                                                                                                                                                                     |

|                                                     | XI I                                                                                                                                                                                                |

| (TANDATANGAN PE                                     | JULIS) (COP DAN TANDA TANGAN PENYELIA)<br>NOOR AZWAN BIN CHAIRI                                                                                                                                     |

| Alamat Tetap:                                       | Pensyarah<br>Fakulti Kejuruteraan Elektronik Dan Kejuruteraan Kommuter                                                                                                                              |

| NO 6G, JALAN HUA TAI NO 2<br>96100 SARIKEI SARAWAK. | Universiti Teknikal Malaysia Melaka (UTeM)<br>Karung Berkunci Ne 1752<br>Pejabat Pos Durian Tunggal<br>76109 Durian Tunggal, Melaka                                                                 |

| Tarikh: 3 May 2011                                  | Tarikh: 3 May 2011                                                                                                                                                                                  |

|                                                     |                                                                                                                                                                                                     |

ii

"I hereby declare that this report is the result of my own except for quotes as cited in the references"

Signature CM

Author : CHAN SIEW YIEN

Date : 3 May 2011

iii

"I hereby declare that i have read this report and in my opinion this report is sufficient in terms of the scope and quality for the award of Bachelor of Electronic Engineering (Wireless Communication) with Honours".

Signature Supervisor Name : EN. NOOR AZWAN BIN SHAIRI

Date

: 3 May 2011

iv

Especially for

My beloved mom and dad

My family

~

My supervisor Mr Noor Azwan bin Shairi

All beloved friends

Thanks for everything ...

ν

#### ACKNOWLEDGEMENT

First of all, I would like to express my deep and sincere gratitude to my supervisor, Mr. Noor Azwan bin Shairi for the period of two semesters. His wide knowledge and his logical way of thinking have been of great help for me. While preparing for this project, Mr. Noor Azwan had given full attention throughout my project and always advising and gives me guidance and motivational moral support to get my project well prepared before I faced the seminar and presentation. Furthermore, he always helps and guides me in fulfilling and understands the task to be done. Here, I would like to express my gratitude towards the people who have helped me with my work and for their cooperation, support, and encouragement directly or indirectly during completing this project especially my colleagues and PSM laboratory technician. Thanks a ton and may God bless all of you. Thank you very much from the bottom of my heart.

# ABSTRACT

This project aims to study the performance of isolation with DGS under PIN Diode for SPST switch design. This project involves with the studies of the background of Defected Ground Structure (DGS), PIN diode and the isolation issue in RF switch. There has been an isolation issue occurs in RF switch. The PIN diode with parasitic capacitance is causing degradation of isolation performance in RF switch and DGS (Defected Ground Structure) has a potential to remove the parasitic capacitance. Nowadays, there has been an increasing interest in studying microstrip lines that prohibit wave propagation in certain frequency bands using defected ground structure (DGS). DGS is implemented by modifying guided wave where it changes the propagation characteristic. DGS is realized by etching only a few areas on the ground plane under the microstrip line. Advanced Design Software (ADS) software will be used for PIN Diode and DGS circuit and layout modeling and then will be fabricated on the FR4 board. Once the prototype has been finish, the measurement parameter will be tested which then measured the isolation performance.

#### ABSTRAK

Projek ini bertujuan untuk mempelajari persembahan sisihan dengan Defected Ground Stucture(DGS) yang diletakkan di bawah PIN diod dalam reka bentuk suis SPST. Projek ini merangkumi kajian kerja untuk latar belakang Defected Ground Structure (DGS), PIN diod dan isu sisihan dalam suis RF. PIN diod yang mengandungi kapasitan parasitik menyebabkan penurunan dalam persembahan sisihan dalam suis RF dan Defected Ground Structure(DGS) mempunyai keupayaan untuk menyingkirkan kapasitan parasitik ini. Pada masa kini, pembelajaran garis mikrostrip yang menghalang perambatan gelombang dalam lingkaran frekuensi tertentu dengan menggunakan DGS kian meningkat. DGS dilaksanakan dengan mengubahsuai panduan gelombang di mana ia mengubah ciri-ciri perambatan. DGS direalisasikan dengan mengores beberapa tempat yang tertentu di permukaan dasar rata di bawah garis mikrostrip. Advanced Design Software (ADS) akan digunakan untuk membuat simulasi litar dan susun atur PIN diod dan DGS dan kemudiannya akan direalisasikan di atas papan litar bercetak FR4. Akhir sekali, ujian akan dilakukan ke atas prototaip yang telah disiap cetak di atas papan FR4 untuk memperolehi hasil sebelum persembahan penyisihan dianalisa.

# CONTENTS

# CHAPTER TITLE

| PRO                   | JECT TITLE                | i    |

|-----------------------|---------------------------|------|

| DEC                   | LARATION OF PSM II REPORT | ii   |

| DEC                   | LARATION                  | iii  |

| SUPI                  | ERVISOR APPROVAL          | iv   |

| DED                   | ICATION                   | v    |

| ACK                   | NOWLEDGEMENT              | vi   |

| ABS                   | TRACT                     | vii  |

| ABS                   | TRAK                      | viii |

| CON                   | TENTS                     | ix   |

| LIST OF TABLES        |                           |      |

| LIST OF FIGURES       |                           |      |

| LIST OF ABBREVIATIONS |                           |      |

| LIST OF APPENDICES    |                           |      |

| INTF                  | RODUCTION                 | 1    |

| 1.1                   | Project Background        | 1    |

| 1.2                   | Problem Statement         | 2    |

| 1.3                   | Project Objective         | 2    |

| 1.4                   | Project Scope             | 2    |

|                       |                           |      |

I

PAGE

| 1.5 | The    | sis Outline                               | 3 |

|-----|--------|-------------------------------------------|---|

| LIT | ERAT   | <b>URE REVIEW</b>                         | 4 |

| 2.1 | PIN    | diode                                     | 4 |

|     | 2.1.1  | Characteristics of the PIN diode          | 5 |

|     | 2.1.2  | PIN diode application as a switches       | 6 |

| 2.2 | Defec  | cted Ground Structure                     | 8 |

| RE  | SEARG  | CH METHODOLOGY                            | ļ |

| 3.1 | Projec | et Methodology                            | I |

| 3.2 | Advar  | nced Design System(ADS)                   | 1 |

| 3.3 | Schen  | natic Design                              | 1 |

| 3.4 | DGS    | Layout Design                             | 1 |

|     | 3.41   | Unit and scale                            | 2 |

|     | 3.42   | Momentum Simulation                       | 2 |

| 3.5 | Layou  | nt Design                                 | 3 |

| 3.6 | Fabric | cation                                    | 3 |

|     | 3.61   | Ultra Violet (UV)                         | 3 |

|     | 3.62   | Etching                                   | 3 |

|     | 3.63   | Cutting                                   | 3 |

|     | 3.64   | Soldering                                 | 3 |

| 3.7 | Proto  | type of RF switch after soldering process | 3 |

| 3.8 | Meas   | urement                                   | 3 |

|     | 3.81   | Electronic Calibration                    | 3 |

H

Ш

C Universiti Teknikal Malaysia Melaka

# IV RESULTS AND DISCUSSION

40

4.1 Schematic Results

40

4.2 DGS Schematic

47

4.3 DGS Simulation Results

48

4.4 Simulation Results for biasing circuit with DGS

54

4.5 Measurement Results

59

4.6 Comparison between simulation and measurement for the sults

# V CONCLUSION AND RECOMMENDATION 62

| 5.1 | Conclusion     | 62 |

|-----|----------------|----|

| 5.2 | Recommendation | 63 |

# **REFERENCES** 64

| APPENDIX A | 66 |

|------------|----|

| APPENDIX B | 69 |

| APPENDIX C | 72 |

# LIST OF TABLES

| NO | TITLE |  |  | PAGE |

|----|-------|--|--|------|

|    |       |  |  |      |

| 3.1 | Specifications of the lumped components used for simulation  | 36 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Specifications of the lumped components used for prototyping | 37 |

C Universiti Teknikal Malaysia Melaka

| NO   | TITLE |  |

|------|-------|--|

| NU - | LILLE |  |

# PAGE

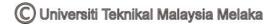

| 2.0  | PIN Diode and Corresponding Equivalent Circuit                     | 6  |

|------|--------------------------------------------------------------------|----|

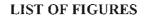

| 2.1  | Series SPST Switch                                                 | 7  |

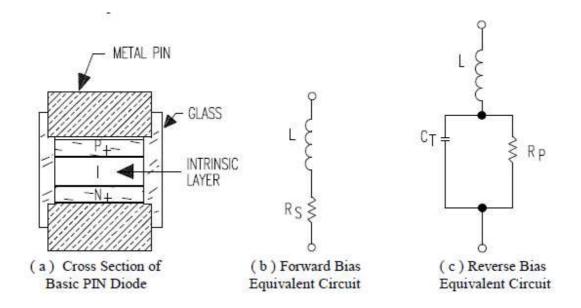

| 2.2  | Shunt SPST Switch                                                  | 8  |

| 2.3  | Three dimensional view and equivalent circuit                      | 9  |

| 2.4  | S-Parameter stop-band characteristic                               | 9  |

| 3.0  | Project flowchart                                                  | 11 |

| 3.1  | Advanced Design Software                                           | 12 |

| 3.2  | Flowchart of schematic design                                      | 14 |

| 3.3  | Select the component and Edit component parameter                  | 15 |

| 3.4  | Enable the component and fill in the min, max, and step size value | 16 |

| 3.5  | Click on the tune button                                           | 16 |

| 3.6  | The component is tuned due to the desired value                    | 17 |

| 3.7  | Choosing the layout window in the ADS software                     | 18 |

| 3.8  | Layout window                                                      | 18 |

| 3.9  | Quick button setup for ADS                                         | 19 |

| 3.10 | Layers                                                             | 20 |

| 3.11 | Layers Editor                                                      | 20 |

| 3.12 | Flow chart of Unit & Scale                                         | 21 |

| 3.13 | Layering the layout                                               | 22 |

|------|-------------------------------------------------------------------|----|

| 3.14 | Momentum simulation                                               | 23 |

| 3.15 | Flow chart of substrate set up process                            | 24 |

| 3.16 | Flow chart of port editor setup                                   | 25 |

| 3.17 | Flow chart of Momentum setup                                      | 26 |

| 3.18 | Layout look-like options                                          | 27 |

| 3.19 | Create layout component                                           | 28 |

| 3.20 | Component library                                                 | 29 |

| 3.21 | Choosing the project save in the component library to the circuit | 29 |

| 3.22 | Schematic diagram with DGS layout                                 | 30 |

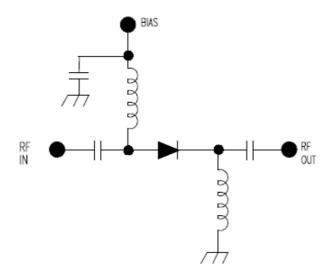

| 3.23 | Biasing circuit                                                   | 31 |

| 3.24 | Generate layout by using ADS                                      | 32 |

| 3.25 | Layout of transmission line with Dumbbell-shaped DGS              | 32 |

| 3.26 | Ultra Violet room                                                 | 33 |

| 3.27 | Ferrite chloride and PCB developer                                | 34 |

| 3.28 | PCB shear                                                         | 34 |

| 3.29 | Soldering Tools                                                   | 35 |

| 3.30 | Convert layout in CorelDraw                                       | 36 |

| 3.31 | Top view (Transmission Line)                                      | 37 |

| 3.32 | Bottom View (Defected Ground Structure)                           | 37 |

| 3.33 | Network Analyzer                                                  | 38 |

| 3.34 | Electronic calibrator                                             | 39 |

| 4.0  | Schematic diagram of DGS under PIN diode                          | 41 |

| 4.1  | Tuning inductor with DC block deactivated                         | 41 |

| 4.2  | Schematic diagram of inductor L with capacitor C activated        | 42 |

| 4.3  | Tuning inductor L with fixed capacitor C activated                | 42 |

| 4.4  | Tuning inductor L with fixed capacitor C deactivated              | 43 |

| 4.5  | Tuning capacitor C with fixed inductor L                          | 43 |

| 4.6  | Schematic diagram of series inductor with capacitor               | 44 |

|      |                                                                   |    |

| 4.8  | Schematic diagram of series inductor L with DC block activated | 45 |

|------|----------------------------------------------------------------|----|

| 4.9  | Tuning series inductor L with DC block activated               | 45 |

| 4.10 | Schematic for DGS standalone                                   | 47 |

| 4.11 | Dumbbell shaped DGS-8mm                                        | 48 |

| 4.12 | Simulation results                                             | 48 |

| 4.13 | Dumbbell shaped DGS-12mm                                       | 49 |

| 4.14 | Simulation results                                             | 49 |

| 4.15 | Dumbbell shaped DGS-14mm                                       | 50 |

| 4.16 | Simulation results                                             | 50 |

| 4.17 | Schematic diagram with dumbbell shaped DGS                     | 52 |

| 4.18 | Biasing circuit with DGS                                       | 53 |

| 4.19 | Simulation results                                             | 54 |

| 4.20 | Simulation results                                             | 54 |

| 4.21 | Simulation results                                             | 55 |

| 4.22 | Simulation results                                             | 55 |

| 4.23 | Simulation results                                             | 56 |

| 4.24 | Simulation results                                             | 56 |

| 4.25 | Measurement results for DGS standalone(14 mm without gap)      | 59 |

| 4.26 | Measurement results                                            | 60 |

| 4.27 | Measurement results                                            | 60 |

| 4.28 | Comparison of Insertion Loss between Simulation and            | 61 |

|      | Measurement results for 14 mm without Gap                      |    |

| 4.29 | Comparison of Isolation between Simulation and Measurement     | 61 |

|      | results for 14 mm without gap                                  |    |

# LIST OF ABBREVIATIONS

| Advanced Design Software  |

|---------------------------|

| Defected Ground Structure |

| Single Pole Single Throw  |

| Direct Current            |

| Field Effect Transistor   |

| Radio Frequency           |

| Printed Circuit Board     |

| SubMiniature version A    |

| Ultra- Violet             |

|                           |

C Universiti Teknikal Malaysia Melaka

# LIST OF APPENDICES

| NO | TITLE                                           | PAGE |

|----|-------------------------------------------------|------|

| A  | Application Note 5327                           | 66   |

| В  | An Introduction to Defected Ground Structure in | 69   |

|    | Microstrip Circuits                             |      |

| С  | PIN Diode Fundamentals                          | 72   |

# **CHAPTER I**

### **INTRODUCTION**

### 1.1 Project Background

There has been an increasing interest in studying microstrip lines that prohibit wave propagation in certain frequency bands using defected ground structure (DGS). DGS is implemented by modifying guided wave where it changes the propagation characteristic. DGS is realized by etching only a few areas on the ground plane under the microstrip line. This project will study the performance of isolation based with dumbbell shaped DGS under PIN Diode for SPST switch design.

### **1.2 Problem Statement**

There are has been an isolation issue occurs in RF switch. The PIN diode with a parasitic capacitance is causing degradation of isolation performance in RF Switch based with dumbbell shaped DGS (Defected Ground Structure) has a potential to remove the parasitic capacitance.

#### **1.3 Project Objective**

This project will study the isolation performance based with dumbbell shaped Defected ground structure (DGS) under PIN diode for SPST switch design.

# 1.4 Project Scope

The scope of this project:

- i. To study the background of Defected Ground Structure (DGS), PIN diode and the isolation issue in RF switch.

- ii. Get familiar with the Advanced Design System Software (ADS).

- iii. PIN diode and Defected Ground Structure (DGS) modeling.

- iv. A simulation and analysis on PIN Diode with Defected Ground Structure (DGS) will be done by using Advanced Design System Software (ADS).

#### 1.5 Thesis Outline

Chapter 1 is about project background for this paper, project statement, objectives, and scope of works. Chapter 2 defines the information and theory relates to this project and also the overview of the component involved. Chapter 3 will explain on the project implementation. It will discuss details on the tools and steps involved during performance of the projects. First and the most important to make this project flow smoothly is the project flow chart.

Chapter 4 will present all the project results regarding the experiments and test that have been done. There are three topologies that had been compared which SPST switch PIN diode that was connected with the dumbbell- shaped defected ground structure of dimensions 8mm, 12 mm, and 14mm with and without gap. This chapter also discusses which topologies is the best to design the RF switch. Chapter 5 is about to make a conclusion and recommendation for future works related to this study.

# **CHAPTER II**

#### LITERATURE REVIEW

### 2.1 PIN Diode

The most important property of the PIN diode is the fact that it can, under certain circumstances, behave as an almost pure resistance at RF frequencies, with a resistance value that can be varied over a range of approximately  $1\Omega$  to  $10 \text{ k}\Omega$  through the use of a DC or low frequency control current. When the control current is varied continuously, the PIN diode is useful for leveling and amplitude modulating an RF signal. When the control current is switched "on" and "off" or in the discrete steps, the device is useful for switching, pulse modulating, attenuating, and phase shifting of an RF signal <sup>[6]</sup>.

#### 2.1.1 Characteristics of the PIN diode

A PIN diode structure got its name from the device construction that consists of a heavily doped p-region and a heavily doped n-region separated by a thin layer of a high resistivity material that is nearly intrinsic. The nearly intrinsic layer is called  $\pi$ -type or v-type depending on whether the conductivity is p-type or n-type, respectively. The thickness of the high-resistivity layer, which is usually of v-type, is 10-200 µm. At zero bias, two separate space-charge regions are formed at the p-I and i-n junctions of a PIN diode just inside the highly doped p and n regions due to the diffusion of holes and electrons across the junction. In the case of an ideal diode, the intrinsic layer has no impurities; that is, it is totally depleted of mobile charge carriers. When a reverse bias is applied, (n electrode positive and p electrode negative) the space-charge regions in the p and n layers become wider and the diode gives rise to very high impedance in this state <sup>[6]</sup>.

When a forward bias is applied to the diode, carrier injection takes place into the intrinsic layer. Electrons are injected into the intrinsic v or  $\pi$  layer from the n-layer and holes are injected from the p-layer. If the intrinsic thickness is less than the diffusion lengths or carrier life times of the injected mobile carriers, the injected carries have uniform distribution and both electrons and holes have equal concentrations. In this conditions, the resistivity of the intrinsic layer drops as the forward bias is increased <sup>[2]</sup>.

The diffusion of carriers reduces the resistivity of the intrinsic layer and it drops further with the increasing forward bias voltage and the diode offers very low impedance in this state. Thus a PIN diode works as a switching device, open circuited in the reverse-biased state and short circuited in the forward-biased state. To achieve a low impedance state of PIN diodes, it is essential that the lifetime of mobile carriers in the intrinsic layer be greater than the time period of the operating frequency<sup>[6]</sup>.

Simplified lumped element equivalent circuits of a packaged PIN diode in reverse- and forward-bias conditions are shown in Figure.  $L_s$  and  $C_p$  represent the series inductance and shunt capacitance of the package,  $R_s$  is the ohmic contact series resistance, and  $C_i$  is the junction capacitance of the diode. Under forward bias condition

$R_f$  is the total diode resistance consisting of intrinsic layer resistance and ohmic contact resistances. Typical equivalent circuit model parameters of a package PIN diode are  $L_s \cong 0.3$  nH,  $C_p \cong 0.3$  pF,  $R_s \cong 0.2\Omega$ ,  $C_j \cong 0.02$  pF, and  $R_f = 1\Omega$ . The forward bias current is about 10 mA and reverse breakdown voltage at 10 µA is about 50V.

Figure 2.0: PIN diode and Corresponding Equivalent Circuit<sup>[6]</sup>

#### 2.1.2 PIN Diode Applications as switches

PIN diodes are commonly used as switching elements to control RF signals. In these applications, the PIN diode can be biased to either a high or low impedance device state, depending on the level of stored charge on the I region. A simple unturned single-pole single throw (SPST) switch may be design using either a single series or shunt connected PIN diode, as shown in Figure 2.1 and Figure 2.2<sup>[6]</sup>. The series connected diode switch is commonly used when minimum insertion loss is required over a broad frequency range. This design is also easier to physically realize using printed circuit techniques, since no through holes are required in the circuit board. A single shunt mounted diode will, on the other hand, produce higher isolation values across a wider

frequency range and will result in a design capable of handling more power since it is easier to heat sink the diode.

Isolation is defined as the ratio of the power delivered to the load for an ideal switch in the ON state to the power delivered to the load when the switch is in the "OFF" state <sup>[4]</sup>. This also is expressed in Decibels and is a positive quantity. There are several techniques one can improve the isolation in switches, including using low OFF state capacitance FETs, distributed with tuning inductors, and realizing band-rejection filter in the operating frequency range. Basically, in these schemes either the OFF state capacitance of the switching devices is tuned out or their effect is minimized. In all these schemes, the insertion loss of the switches more or less remains the same. Most switches circuits designed at RF and low end of the microwave frequency band generally do not use any matching or tuning elements. They work down to DC, however as the frequency increases, the insertion loss increases and the isolation decreases due to finite value of the capacitance of the switching device in the OFF state <sup>[4]</sup>.

Figure 2.1: Series SPST Switch<sup>[6]</sup>

C Universiti Teknikal Malaysia Melaka