# IMPLEMENTATION OF MEMORY BIST CONTROLLER IN FPGA USING THE IMPROVED MARCH AZ1 AS THE TEST ALGORITHM

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## IMPLEMENTATION OF MEMORY BIST CONTROLLER IN FPGA USING THE IMPROVED MARCH AZ1 AS THE TEST ALGORITHM

## **CLEMENT OOI JUN JIE**

This report is submitted in partial fulfillment of the requirements for the degree of Bachelor of Electronics Engineering Technology with Honours

Faculty of Electronics and Computer Technology and Engineering

Universiti Teknikal Malaysia Melaka

4. Sila tandakan ( ):

Alamat Tetap:

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

FAKULTI TEKNOLOGI DAN KEJURUTERAAN ELEKTRONIK DAN KOMPUTER

## BORANG PENGESAHAN STATUS LAPORAN PROJEK SARJANA MUDA II

Tajuk Projek : implementation of memory bist controller in fpga

USING THE IMPROVED MARCH AZ1 AS THE TEST ALGORITHM

Sesi Pengajian : 2024/2025

Saya <u>CLEMENT OOI JUN JIE</u> mengaku membenarkan laporan Projek Sarjana Mud ini disimpan di Perpustakaan dengan syarat-syarat kegunaan seperti berikut:

- 1. Laporan adalah hakmilik Universiti Teknikal Malaysia Melaka.

- 2. Perpustakaan dibenarkan membuat salinan untuk tujuan pengajian sahaja.

- 3. Perpustakaan dibenarkan membuat salinan laporan ini sebagai bahan pertukaran antara institusi pengajian tinggi.

| SULIT*         | (Mengandungi maklumat yang berdarjah<br>keselamatan atau kepentingan Malaysia<br>seperti yang termaktub di dalam AKTA<br>RAHSIA RASMI 1972) |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| TERHAD*        | (Mengandungi maklumat terhad yang<br>telah ditentukan oleh organisasi/badan di<br>mana penyelidikan dijalankan.                             |

| ✓ TIDAK TERHAD |                                                                                                                                             |

|                | Disahkan oleh:                                                                                                                              |

DR. AIMAN ZAKWAN BIN JIDIN

Pensyarah Kanan Fakulti Teknologi dan Kejuruteraan Elektronik dan Komputer Universiti Teknikal Malaysia Melaka

Tarikh: 12 Februari 2025 Tarikh: 14 Februari 2025

## **DECLARATION**

I declare that this project report entitled "IMPLEMENTATION OF MEMORY BIST CONTROLLER IN FPGA USING THE IMPROVED MARCH AZ1 AS THE TEST

**ALGORITHM**" is the result of my own research except as cited in the references. The project report has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature    | :            |                                   |

|--------------|--------------|-----------------------------------|

| Student Name | :<br>کر ملیب | CLEMENT OOI JUN JIE<br>31/12/2024 |

| Date         | ••• 0        | 31/12/2024                        |

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## **APPROVAL**

I hereby declare that I have checked this project report and in my opinion, this project report is adequate in terms of scope and quality for the award of the degree of Bachelor of Electronics Engineering Technology with Honours.

| Signature       | A MILE RE |             |           |       |  |

|-----------------|-----------|-------------|-----------|-------|--|

| Supervisor Name | :         | DR. AIMAN Z | AKWAN BIN | JIDIN |  |

| Date            | :         | 14 Febru    | ary 2025  |       |  |

| Signature       | کل ملیا   | تيكيت       | برسيني    | اونيو |  |

| Co-Supervisor   | TI TEKNI  |             |           |       |  |

| Name (if any)   |           |             |           |       |  |

| Date            |           |             |           |       |  |

## **DEDICATION**

To my dear family, To my loyal friends, To my supervisor and mentors, And to my dearest self,

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### **ABSTRACT**

This project aims to develop and implement a Memory Built-In Self-Test (MBIST) controller in an FPGA device using the Improved March AZ1 algorithm. MBIST is essential for testing memory components within a System-on-Chip (SoC) to ensure they are free of faults. The numbers of test operations increases and results in a higher complexity to detect more faults in the test and will increases the cost and hardware area overhead. The March AZ algorithm was selected for its efficiency in detecting various memory fault models. To overcome more faults in the test, the numbers of test operations increases and results in a higher complexity. The project is proposed to improve the March AZ algorithm's fault coverage as the March AZ1 algorithm while maintaining its complexity is equal to the complexity of 13N. The March AZ1 algorithm is improved by rearranging the test sequences of the March AZ algorithm. Extensive testing on fault-free and fault-injected memory models will be demonstrate the controller's effectiveness in detecting a wide range of memory faults, validating its reliability. The project is successfully implement an effective MBIST solution in FPGA, providing a valuable tool for ensuring memory reliability in SoCs. Future work could be focus on further optimizing the MBIST controller and adapting the algorithm for different memory technologies.

#### **ABSTRAK**

Projek ini bertujuan untuk membangunkan dan melaksanakan pengawal Ujian Kendiri Terbina Dalam Memori (MBIST) dalam peranti FPGA menggunakan algoritma AZ1 Mac yang Diperbaiki. MBIST adalah penting untuk menguji komponen memori dalam Systemon-Chip (SoC) untuk memastikan ia bebas daripada kerosakan. Bilangan operasi ujian meningkat dan menghasilkan kerumitan yang lebih tinggi untuk mengesan lebih banyak kerosakan dalam ujian dan akan meningkatkan kos dan overhed kawasan perkakasan. Algoritma AZ Mac dipilih untuk kecekapannya dalam mengesan pelbagai model kerosakan memori. Untuk mengatasi lebih banyak kesilapan dalam ujian, bilangan operasi ujian meningkat dan menghasilkan kerumitan yang lebih tinggi. Projek ini dicadangkan untuk menambah baik liputan kesalahan algoritma AZ Mac kerana algoritma AZ1 Mac sambil mengekalkan kerumitannya adalah sama dengan kerumitan 13N. Algoritma AZ1 Mac dipertingkatkan dengan menyusun semula urutan ujian algoritma AZ Mac. Pengujian meluas pada model ingatan bebas kesalahan dan disuntik kesalahan akan menunjukkan keberkesanan pengawal dalam mengesan pelbagai kesalahan memori, mengesahkan kebolehpercayaannya. Projek ini berjaya melaksanakan penyelesaian MBIST yang berkesan dalam FPGA, menyediakan alat yang berharga untuk memastikan kebolehpercayaan memori dalam SoC. Kerja masa depan boleh difokuskan untuk mengoptimumkan lagi pengawal MBIST dan menyesuaikan algoritma untuk teknologi memori yang berbeza.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my gratitude to my supervisor, Dr. Aiman Zakwan Bin Jidin for their precious guidance, words of wisdom and patient throughout this project.

I am also indebted to Universiti Teknikal Malaysia Melaka (UTeM) for the financial support through DR Aiman Zakwan Bin Jidin which enables me to accomplish the project. Not forgetting my fellow colleague, Kok Chi Zhao for the willingness of sharing his thoughts and ideas regarding the project.

My highest appreciation goes to my parents, parents in-law, and family members for their love and prayer during the period of my study. An honourable mention also goes to Shermine Ooi Wei San for all the motivation and understanding.

Finally, I would like to thank all the staffs at the FTKEK, fellow colleagues and classmates, the Faculty members, as well as other individuals who are not listed here for being co-operative and helpful.

## **TABLE OF CONTENTS**

|                                          | Page    |

|------------------------------------------|---------|

| DECLARATION                              |         |

| APPROVAL                                 |         |

| DEDICATIONS                              |         |

| ABSTRACT                                 | i       |

| ABSTRAK                                  | ii      |

| ACKNOWLEDGEMENTS                         | iii     |

| TABLE OF CONTENTS                        | iv      |

| LIST OF TABLES                           | vi      |

| LIST OF FIGURES                          | vii     |

| LIST OF ABBREVIATIONS                    | viii    |

| LIST OF APPENDICES                       | ix      |

| CHAPTER 1 INTRODUCTION                   | 1       |

| 1.1 Research Background                  | 1       |

| 1.2 Problem Statement                    | 3       |

| 1.3 Project Objective                    | 4       |

| 1.4 Scope of Project EKNIKAL MALAYSIA ME | ELAKA 4 |

| 1.5 Project Outline                      | 5       |

| CHAPTER 2 LITERATURE REVIEW              | 6       |

| 2.1 Introduction                         | 6       |

| 2.2 Semiconductor Memories               | 6       |

| 2.3 Memory fault models                  | 9       |

| 2.4 Memory Built-In Self Test (MBIST)    | 12      |

| 2.5 MBIST test algorithms                | 15      |

| 2.6 Review on exiexting test algorithms  | 17      |

| 2.7 Summary                              | 24      |

| CHAPTER 3 METHODOLOGY                    | 25      |

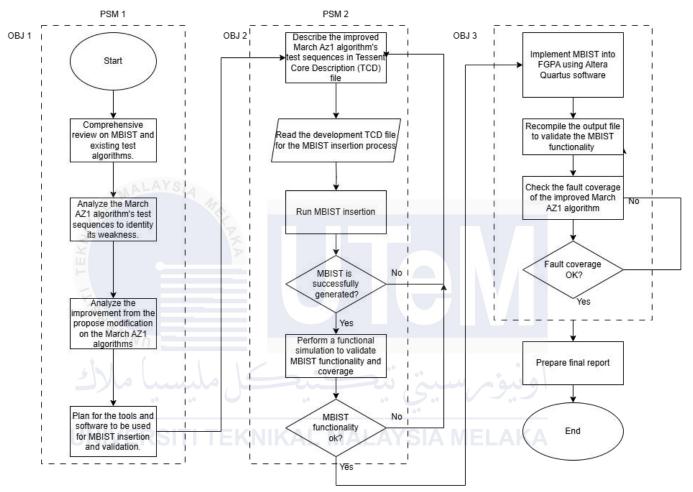

| 3.1 Introduction                         | 25      |

| 3.2 Project Design                       | 26      |

| 3.2.1 Project Execution Flow                | 26 |

|---------------------------------------------|----|

| 3.2.2 Project Planning                      | 29 |

| 3.3 The Improved March AZ1 Algorithm        | 30 |

| 3.4 Project Development                     | 38 |

| 3.5 Software and Hardware                   | 42 |

| 3.5.1 Software                              | 42 |

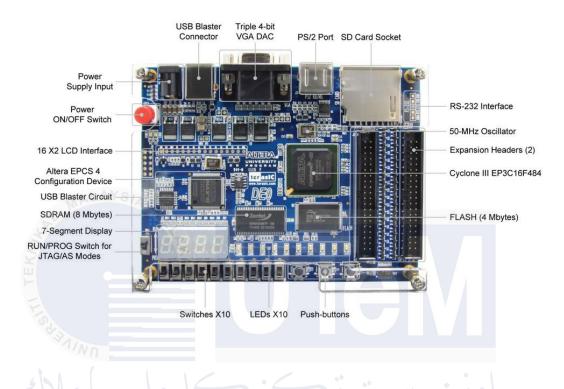

| 3.5.2 Hardware                              | 43 |

| 3.6 Summary                                 | 45 |

| CHAPTER 4 RESULTS AND DISCUSSIONS           | 47 |

| 4.1 Introduction                            | 47 |

| 4.2 Test on the fault-free memory model     | 47 |

| 4.3 Test on the fault-injected memory model | 49 |

| 4.4 Test on the Altera Quartus using FPGA   | 52 |

| 4.5 Limitation                              | 54 |

| 4.6 Summary                                 | 54 |

| CHAPTER 5 CONCLUSION                        | 55 |

| 5.1 Conclusion                              | 55 |

| 5.2 Recommendation for future work          | 57 |

| 5.3 Potential of commercialization          | 58 |

| REFERENCES                                  | 59 |

| APPENDICES                                  | 63 |

|                                             |    |

## LIST OF TABLES

| <b>TABLE</b> | TITLE                                                             | PAGE |

|--------------|-------------------------------------------------------------------|------|

| Table 2.1    | Example of several March test algorithm with their sequences      | 19   |

| Table 2.2    | Example of several March test algorithm with their fault coverage | 21   |

| Table 3.1    | The recent March AZ1 algorithm's fault detection analysis         | 30   |

| Table 3.2    | The Improved March AZ1 algorithm descriptions                     | 32   |

| Table 3.3    | The Improved March AZ1 algorithm's fault detection analysis       | 34   |

| Table 4.1    | The Test Result of the Improved March AZ1 algorithms              | 50   |

|              |                                                                   |      |

## LIST OF FIGURES

| <b>FIGURE</b> | TITLE                                                                                           | PAGE |

|---------------|-------------------------------------------------------------------------------------------------|------|

| Figure 2.1    | Types of memories                                                                               | 6    |

| Figure 2.2    | Flowchart of MBIST                                                                              | 12   |

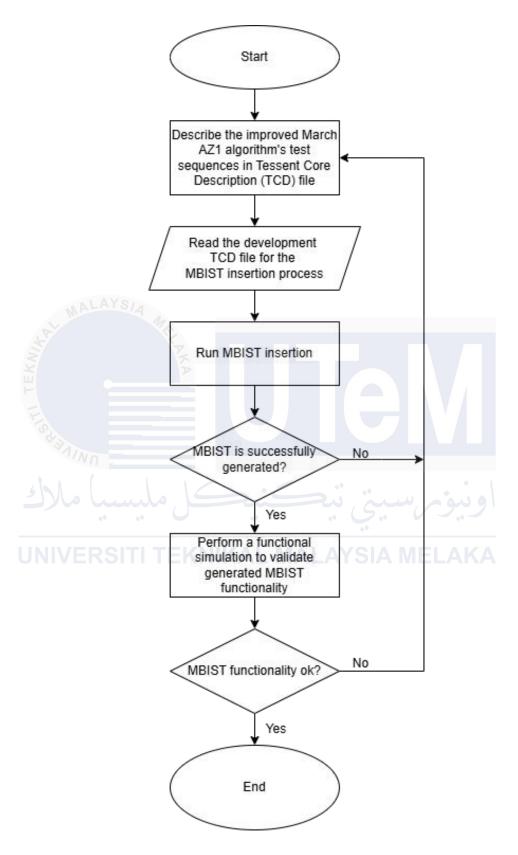

| Figure 3.1    | Project Execution Flowchart                                                                     | 26   |

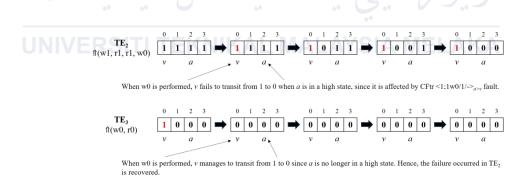

| Figure 3.2    | Illustration of the CFtr < 1; $1 \text{w} 0 / 1 / ->_{a>v}$ fault recovering at TE <sub>3</sub> | 36   |

|               | of the improved March AZ1 algorithm.                                                            |      |

| Figure 3.3    | Flowchart of Implementation of MBIST                                                            | 39   |

| Figure 3.4    | FPGAs (Field Programmable Gate Arrays)                                                          | 43   |

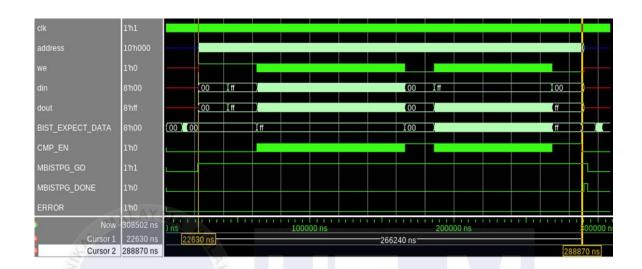

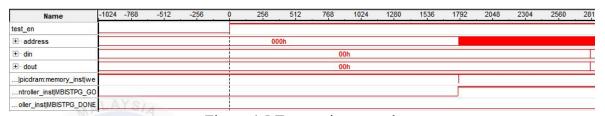

| Figure 4.1    | The simulation waveform observed in QuestaSim from the test on                                  | 48   |

|               | the fault-free memory model by Improved March AZ1 as the UDA                                    |      |

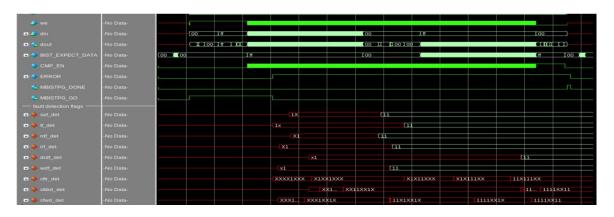

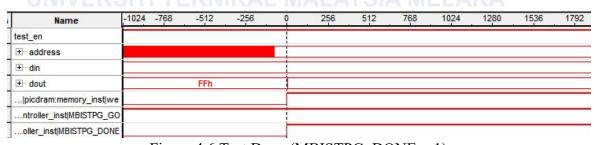

| Figure 4.2    | The waveform observed from the test on the fault-injected memory, using                         | 49   |

|               | the Improved March AZ1 as the UDA.                                                              |      |

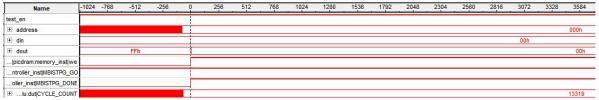

| Figure 4.5    | Test_en is asserted                                                                             | 52   |

| Figure 4.6    | Test Done (MBISTPG_DONE = 1)                                                                    | 52   |

| Figure 4.7    | Cycle count for Improved March AZ1 Algorithms                                                   | 53   |

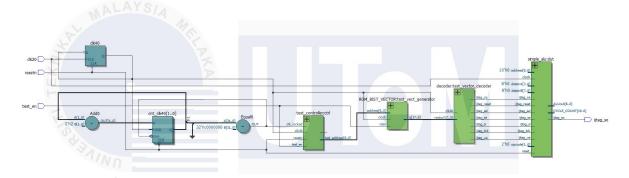

| Figure 4.8    | Schematic RTL design after implementation into FPGA                                             | 53   |

| Figure 4.9    | Complilation Flow Summary                                                                       | 54   |

## LIST OF ABBREVIATIONS

MBIST - Memory Built-In-Self-Test

SAF - Stuck-At Fault

TF - Transition Fault

RDF - Read Disturb Fault

IRF - Inversion Read Fault

DRDF - Deceptive Read Disturb Fault

WDF - Write Disturb Fault

CFtr - Transition Coupling Fault

CFdrd - Deceptive Read Destructive Fault

CFwd Write Desturctive Fault

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## LIST OF APPENDICES

| APPENDIX   | TITLE                                 | PAGE |

|------------|---------------------------------------|------|

| Appendix 1 | Gantt Chart                           | 63   |

| Appendix 2 | Project Milestone                     | 64   |

| Appendix 3 | Improved March AZ1 algorithm TCD file | 65   |

| Appendix 4 | TessentSyncRamOps TCD File            | 67   |

## **CHAPTER 1**

#### INTRODUCTION

## 1.1 Research Background

Memory built-in self-test (MBIST) is a method for testing embedded memories on chips that is quite popular since it is a short testing time at a low cost [1]. Because of its ability to self-test and self-check test replies, an expensive external tester is not necessary. Furthermore, it has the ability to run numerous tests concurrently on various memory blocks. Its fault coverage (FC) and test method complexity are the key determinants of its efficiency. The amount of test operations carried out on N memory cells is represented by the test complexity. The longer the test, the more difficult it is, consequently, the chip test's overall duration and production costs rise. MBIST is a widely used technique because it is has a short testing time at a low cost [1].

March test algorithms are a family of memory test algorithms used to detect the faults in memory cells. The name "March" comes from the way these algorithms "march" through the memory addresses, performing write and read operations in a systematic manner. They are designed to detect various fault models such as stuck-at faults, transition faults, coupling faults, and neighborhood pattern sensitive faults [2].

The March AZ2 algorithm and March AZ1 algorithms is the new test algorithms. The March AZ2 algorithm's test sequence was simplified to (w0); (w0, r0); (r0, w1, w1, r1); (r1, w0); (r0, w1, w1, r1); (r1) while the March AZ1 algorithm's test sequences was simplified to (w0); (w1); (w1, r1, r1, w0); (w0, r0); (r0, w1, w1, r1); (r1). For March AZ2 algorithm have a fault coverage (FC) of 83.3%

(detect 30 out of 36 possible fault) with 14N complexity but f or March AZ1 algorithm have a fault coverage (FC) of 80.6% (detect 29 out of 36 possible fault) with 13N complexity [1]. Therefore, this project is proposed with a motivation to improve the March AZ1 to match the March AZ2 fault coverage while maintaining its complexity lower or same to 14N [1].

#### 1.2 Problem Statement

The most use of algorithm are the March algorithms test. By using the March algorithms, the costs and chip area overhead can be reduced with a lower complexity. To detect more faults in the test, the numbers of test operations increases and results in a higher complexity. This will also increases the cost and hardware area overhead [2]. Many 10N and 14N complexity test algorithms are available to produce memory testing within low testing time but most of them have poor coverage of many faults such as Write Disturb Fault (WDF), Data retention fault (DRF) and their coupling faults. So, the March AZ1 algorithms were used to provide an excellent fault coverage while having the complexity at 13N. However, March AZ1 algorithms have a slightly lower Transition Coupling Fault (CFtr) which is 5/8 (62.5%). Therefore, this project focuses on improving the March AZ1 algorithm's fault coverage while maintain the same complexity of 13N [2].

## 1.3 Project Objective

The proposed project embarks on the following objectives:

- I. To develop an improved March AZ1 test algorithm to match the March AZ2 test algorithm fault coverage while maintaining its complexity lower than March AZ2 test algorithm.

- II. To implement a Memory BIST controller in FPGA using the improved March AZ1 as the test algorithm.

- III. To evaluate the fault coverage and complexity of the improved March AZ1 algorithm through tests and analysis.

## 1.4 Scope of Project

In order the achieve the project objectives mentioned in Section 1.3, the following works are involved.

- I. The March AZ1 was improved by rearranging the test sequences to provide the higher fault coverage as the March AZ1 algorithm which is with the same complexity of 13N.

- II. The March AZ1 algorithm and improved March AZ1 algorithm were applied as the UDA in the MBIST controller. The MBIST insertion process was done using Siemens Tessent MemoryBIST software as the tool. The MBIST insertion was targeted for a 1 kB SRAM as the memory model to be tested.

- III. The improved March AZ1 algorithm were simulate in the QuestaSim software on both fault-free and fault-injected model. The waveform was captured as the result.

- IV. The generated MBIST circuit was implemented in FPGA development board by using Altera Quartus Design software, which synthesize the design before fitting it into the FPGA configuration and generating the bitstream file to be programmed in the FPGA.

- V. The tests using the implemented MBIST in FPGA was conducted on a fault-free memory model to validate its functionality

The proposed project functionality evaluation was done by examining the outputs produced from the FPGA experimental tests that will be captured and displayed by the integrated SignalTap logic analyzer.

## 1.5 Report Outline

This report consists of 5 chapters. Chapter 2 reviews on the semiconductor memories that used in the System-on-Chip (SoC) designs, memory fault models, Memory Built-In Self Test (MBIST), MBIST test algorithms and the existing test algorithms. Chapter 3 reviews on the project design, project planning and project development for the report. Chapter 3 also reviews about the improved March AZ1 algorithm and the software and hardware used in this project. Chapter 4 reviews about the test results for the fault-free memory models and fault-injected memory models of improved March AZ1 algorithm. Chapter 4 also mention about the test on the Altera Quartus using FPGA and the limitation for this project. Chapter 5 states the summary for this project for each objective listed.

#### **CHAPTER 2**

## LITERATURE REVIEW

#### 2.1 Introduction

This chapter comprehensive reviews about the memories used in SoC, the on-chip memory testing using MBIST, and the existing test algorithms. Section 2.2 review on the semiconductor memories while Section 2.3 describe about the memory fault models. Section 2.4 describes about the Memory Built-In Self Test (MBIST) while section 2.4. Next, section 2.5 review about the MBIST test algorithm while section 2.6 reviews about the existing test algorithms.

#### 2.2 Semiconductor Memories

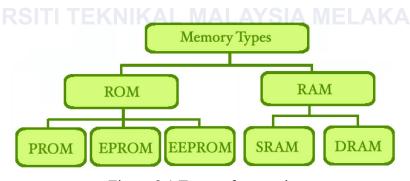

Figure 2.1 Types of memories

Embedded memories in System-on-Chip (SoC) designs refer to memory components that are integrated directly onto the same silicon die as the other components of the system. These memories serve as crucial storage elements for data and instructions within the SoC, enabling various functions and applications to operate efficiently [3].

Random Access Memory (RAM) is a volatile memory type, meaning its contents are

lost when the power is turned off. It is used to temporarily store data and program instructions that the Central Processing Unit (CPU) needs to access quickly during the execution of programs [3]. RAM is characterized by its fast read and write speeds, making it ideal for tasks that require frequent data access and manipulation. ROM is a non-volatile memory type, meaning its contents are retained even when the power is turned off. It is used to store permanent or semi- permanent data and program instructions that are not expected to change frequently during the operation of the system [3].

There were some types of Embedded Memories which is Static Random-Access Memory (SRAM), Dynamic Random-Access Memory (DRAM) and Non-Volatile Memories. SRAM is often used for cache memory within SoCs due to its fast access times and low power consumption. It provides high-speed access to frequently accessed data, enhancing the overall performance of the system. DRAM is used for main memory in SoCs, providing larger storage capacity compared to SRAM but with slightly slower access times. It serves as the primary storage for program instructions and data during the execution of applications. SoCs may also include non-volatile memory components like Flash memory or Electrically Erasable Programmable Read-Only Memory (EEPROM) for storing firmware, boot code, or configuration data that needs to persist across power cycles [4].

The embedded memories are typically integrated directly onto the SoC die using specialized manufacturing processes. This integration reduces the need for external memory chips, saving board space and reducing power consumption. Interconnect structures within the SoC connect the embedded memories to the CPU, peripherals, and other components, enabling data transfer and access [5].

Given the critical role of embedded memories in SoCs, thorough testing and

verification processes are essential to ensure their reliability and functionality [5]. Techniques like Memory Built-In Self-Test (MBIST) are commonly employed to enable memories to test themselves for faults and defects autonomously. Advanced verification methodologies, including simulation, emulation, and formal verification, are used to validate memory designs and ensure they meet performance, power, and reliability requirements [6].

In summary, embedded memories are essential components of SoCs, providing storage for data and instructions and influencing the overall performance, power consumption, and security of the system. Designing, integrating, and testing embedded memories require careful consideration of various factors to ensure the reliability, functionality, and security of SoCs in diverse applications [6].

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## 2.3 Memory fault models

Faults in digital systems are broadly categorized into static and dynamic faults, each representing different types of malfunctions that can occur in a system [7]. Static faults are those where the failure mode is constant and does not change over time [7]. Examples include stuck-at faults, where a signal line is permanently stuck at a logical high (1) or low (0) value, and open faults, where a circuit line is disconnected and thus always reads as an undefined state. These faults are relatively straightforward to detect with static test patterns that do not rely on changing conditions. Static faults typically result from physical defects in the hardware, such as manufacturing imperfections, and are often identified through direct inspection or simple test algorithms [8].

In contrast, dynamic faults occur under specific conditions or sequences of operations, making them more challenging to detect [5]. Dynamic faults are often influenced by factors like operational timing, environmental conditions, and the specific usage pattern of the device. Detecting these faults requires more sophisticated testing methodologies that involve sequences of operations, varying conditions, and timing analysis. Dynamic faults are critical to identify because they can lead to intermittent and unpredictable system failures, which are harder to diagnose, and fix compared to static fault [5].

This project focuses on the detection of static faults, which are faults that remain constant and do not change over time. These include common issues like stuck-at faults, where a signal line is permanently fixed at a logical high or low value, and open faults, where a circuit line is disconnected and consistently reads as an undefined state. By employing specific test algorithms designed to identify these static faults, the project aims to ensure the reliability and correctness of hardware systems, addressing critical defects that can result from manufacturing imperfections and other static conditions.

There are many type of static fault which are [5]:

- 1. Stuck-at Fault (SAF): A stuck-at fault occurs when a signal line or node in a digital circuit is consistently stuck at either a logic high ('1') or a logic low ('0') state. This fault remains persistent regardless of the input or operation. SAFs are typically caused by defects in the manufacturing process, such as material impurities or physical damage, and are relatively straightforward to detect using test patterns that attempt to force the line to both states and then verify its response.

- Transition Fault (TF): Transition faults manifest as failures in the transition of a digital signal from one logic state to another within the expected timeframe.

There are two types: rising transition faults (0 to 1) and falling transition faults (1 to 0). These faults can occur due to various reasons, including timing violations, signal integrity issues, or manufacturing irregularities. Detecting TFs involves applying test patterns that aim to induce transitions and verifying if they occur as expected.

- 3. Read Disturb Fault (RDF): RDFs arise in non-volatile memory devices when the act of reading data repeatedly from a memory cell disturbs the contents of nearby cells. This disturbance can result in unintended changes in adjacent memory locations. RDFs are particularly relevant in flash memory technologies and can degrade device reliability over time due to wear-out mechanisms.

- 4. Inversion Read Fault (IRF): IRF occurs when reading a memory cell results in the incorrect inversion of the stored data. For instance, reading a '1' might return a '0' and vice versa. This fault can be caused by various factors,

- including transistor leakage or cross-coupling effects, and can lead to data integrity issues in memory systems.

- 5. Deceptive Read Disturb Fault (DRDF): DRDFs occur when reading a memory cell disturbs the data in neighboring cells temporarily, leading to incorrect readouts during specific read operations. Unlike RDFs, which cause permanent changes, DRDFs only affect the read operation temporarily and may not be immediately detectable after the read operation.

- 6. Write Disturb Fault (WDF): WDFs arise when writing data to a memory cell inadvertently alters the contents of nearby cells due to electrical interference or coupling effects. These faults can occur in various memory technologies, including DRAM and flash memory, and can lead to data corruption or integrity issues if left undetected.

- 7. Transition Coupling Fault (CFtr): Occurs when a transition in one memory cell triggers an unintended transition in a neighboring cell.

- 8. Deceptive Read Destructive Fault (CFdrd): Involves a read operation that disturbs the data in a neighboring cell, leading to incorrect readouts and potentially permanent data corruption.

- 9. Write Destructive Fault (CFwd): Arises when writing data to one memory cell inadvertently alters the contents of another cell. CFs require comprehensive testing strategies to detect interactions between memory cells and mitigate their impact on system reliabily.

## 2.4 Memory Built-In Self Test (MBIST)

MBIST is a design technique used in integrated circuits (ICs) to ensure the reliability and functionality of embedded memories, such as SRAM (Static Random-Access Memory) or DRAM (Dynamic Random-Access Memory). In MBIST, the memory is equipped with circuitry that allows it to test itself for faults and defects without requiring external test equipment. This self-testing capability is crucial for detecting and diagnosing faults that may occur during the operation of the device, such as manufacturing defects, aging-related issues, or environmental factors [8].

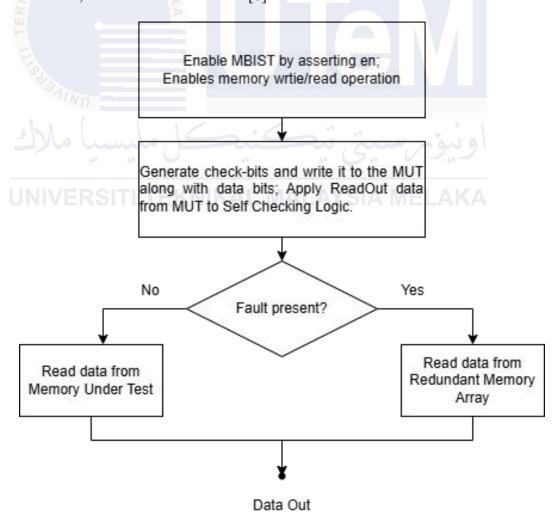

Figure 2.2 Flowchart of MBIST

MBIST typically involves generating test patterns and applying them to the memory array, then comparing the expected results with the actual results to identify any discrepancies [9]. It helps in identifying faults such as stuck-at faults(where a bit is always at a high or low logic level), transition faults (where a bit fails to switch its value), and coupling faults (where adjacent bits interfere with each other)[9]. Overall, MBIST plays a critical role in ensuring the reliability and quality of memory components in modern integrated circuits.

The principle of working of MBIST involves several key steps [10]:

- 1. Test Pattern Generation: The MBIST controller generates a set of test patterns designed to thoroughly exercise the memory array. These patterns are carefully crafted to detect various types of faults, including stuck-at faults, transition faults, and coupling faults.

- 2. Test Pattern Application: The generated test patterns are applied to the memory array by configuring the memory's address and data input/output paths accordingly. The memory controller coordinates this process to ensure that each test pattern is applied correctly.

- 3. Data Comparison: As the test patterns are applied, the memory controller compares the expected output data (based on the test patterns) with the actual output data obtained from the memory array. Any discrepancies between the expected and actual data indicate potential faults or defects within the memory.

- 4. Fault Identification: When discrepancies are detected, the MBIST controller identifies the specific locations within the memory array where faults may be present. This information is crucial for diagnosing the root causes of the faults.

- 5. Reporting: The results of the MBIST self-test are typically logged and reported to higher- level system components. This information allows system-level firmware or

software to make informed decisions about the operational status and reliability of the memory.

Siemens Tessent MemoryBIST software streamlines MBIST generation by automating the creation of tailored MBIST structures for specific memory architectures and test requirements [11]. Designers input parameters such as memory size, organization, and desired fault coverage levels, and the software utilizes sophisticated algorithms to generate the necessary MBIST logic, including test pattern generators, response analyzers, and control circuitry. This automated process ensures efficient integration of MBIST into the semiconductor design, enhancing memory testing capabilities while minimizing development time and effort, ultimately improving product quality and reliability [12].

There were some type of algorithm such as non-linear algorithm, linear algorithm and classical test algorithm. For non-linear algorithm, a non-linear algorithm is a computational process where the relationship between input size and computation time or resource usage is not proportional or directly scalable, often involving complexities higher than linear, such as quadratic, polynomial, or exponential [13]. Unlike linear algorithms, which exhibit a straight-line growth pattern as inputs increase, non-linear algorithms may involve nested loops, recursive calls, or combinatorial processes, leading to growth rates that escalate rapidly with larger inputs. These algorithms are essential for solving complex problems in fields like optimization, graph theory, and artificial intelligence, where interactions among elements do not follow a simple, direct pattern and require more sophisticated approaches to manage [13].

Next, a linear algorithm is a computational process in which the time or resources required to complete the task increase directly in proportion to the size of the input [14]. This means that if the input size doubles, the computation time or resource usage also doubles, resulting in a predictable and manageable growth pattern [14]. Linear algorithms

are characterized by their simplicity and efficiency, making them ideal for tasks such as searching, traversing a list, or performing basic arithmetic operations where each step involves a constant amount of work relative to the input size. This predictability and scalability make linear algorithms fundamental in computer science for handling straightforward problem efficiently[14].

## 2.5 MBIST test algorithms

A classical test algorithm refers to a traditional, well-established method used for assessing the functionality, performance, or reliability of a system or component, often in hardware and software testing [15]. These algorithms follow a predefined sequence of operations designed to systematically evaluate various aspects of the subject under test, such as correctness, efficiency, and fault tolerance [15]. Examples include the binary search for testing sorted arrays, the bubble sort for sorting algorithms, and the basic memory test algorithms like MATS (Modified Algorithmic Test Sequence) and the March test for memory fault detection. Classical test algorithms are foundational in ensuring the integrity and performance of systems, leveraging their simplicity and robustness to provide reliable testing results [15].

The March test algorithms are a family of memory testing algorithms commonly used to test the functionality and reliability of memory components, particularly SRAM (Static Random-Access Memory) [16]. These algorithms systematically walk through memory cells in a specific order, performing read, write, and compare operations. They are designed to detect various types of faults, including stuck-at faults, transition faults, and coupling faults. The name "March" is derived from the initials of its creator, IBM engineer R.H. "Bob" March [17].

The March algorithm is a systematic method used for testing and detecting faults in

Random Access Memory (RAM) [18]. It operates by executing a series of read and write operations on each memory cell in a specific sequence, often traversing the memory in both forward and backward directions [18]. This bidirectional approach helps identify various types of faults such as stuck-at faults, transition faults, coupling faults, and address decoder faults [18]. By meticulously marching through the memory, the algorithm ensures comprehensive fault coverage while maintaining efficiency in the number of operations performed [18].

Designed to be efficient and thorough, March algorithms balance the trade-off between testing time and fault detection capability. An example is the March C- algorithm, which uses a sequence of write, read, and compare operations in both ascending and descending address orders to uncover faults. This methodical process ensures that each cell is tested multiple times under different conditions, enhancing the likelihood of detecting any present faults. Overall, the March algorithm's structured approach and bidirectional testing make it a robust tool for ensuring memory reliability [16].

In a checkerboard pattern, the 1s and 0s are written into different memory locations within the cell array. In order to place each nearby cell in a separate group, the algorithm splits the cells into two alternating groups. The checkerboard pattern is mostly utilized to activate failures brought on by SAF, leakage, and cell-to-cell shorts [19].

## 2.6 Review on existing test algorithms

The table outlines various test algorithms used for detecting faults in integrated circuits, focusing on their complexity and fault coverage. Basic algorithms like March C- and March CL provide foundational fault detection with complexities of 10N and 12N, respectively, offering comprehensive coverage for stuck-at faults (SAF) and transition faults (TF)[12]. These algorithms use a series of read and write operations to identify faults, with March CL extending its sequences to include additional read operations for improved fault detection [20].

More advanced algorithms, such as PMOVI and March RAW1, increase the complexity to 13N, incorporating sequences that alternate between reading and writing operations [21]. These algorithms extend fault detection to include data retention faults (DRF) and coupling faults (CF), providing more robust fault coverage. March LR and March SR further enhance this approach with a complexity of 14N, focusing on detecting linear read and write errors [22]. The Modified March SR algorithm improves this by increasing coverage for write disturb faults (WDF) and coupling faults through modified read/write sequences [23].

The most comprehensive algorithms, including March AZ1, March AZ2, March-sift, March-ee, March MSS, March LV, March CS, March SS, and March RAW, feature higher complexities ranging from 14N to 26N [24]. These algorithms offer extensive sequences designed to detect a broad spectrum of faults, including subtle and complex ones like coupling faults and write disturb faults [24]. Algorithms like March MSS and March SS, with complexities of 18N and 22N, respectively, provide exhaustive read/write operations to ensure thorough fault detection across all major fault types [24]. March RAW, with the highest complexity of 26N, incorporates the most detailed sequences to achieve complete fault coverage, ensuring the highest reliability by

detecting even the most challenging faults [24].

In the domain of memory testing, achieving an optimal balance between test complexity and fault coverage (FC) is essential. Simpler algorithms like March C and March C- offer quick and efficient tests with low complexity (10N-11N), but they fall short in detecting more complex faults, providing only basic fault coverage [25]. Algorithms like March CL and March SR improve on this by including double read operations, enabling partial detection of certain faults like DRDF and CFdrds with moderate complexity (12N-14N) [22]. However, they still miss other fault types such as Write Disturb Faults (WDF) and Write Coupling Faults (CFwds). More complex algorithms such as March-sift and March-ee, despite having higher complexities (17N-18N), show limitations due to redundancy in their sequences and lack of specific operations required to detect all fault types comprehensively [26].

March AZ1 and March AZ2 are preferred because they strike a balance between fault coverage and test complexity, making them efficient and effective for practical memory testing [24]. Both algorithms offer high fault coverage comparable to more complex tests but maintain moderate complexity, avoiding excessive resource and time demands [24]. March AZ1 uses a sequence focused on efficient fault detection through repeated write and read operations, while March AZ2 adjusts the order slightly to achieve similar results. Both algorithms are designed to handle a wide range of faults effectively, making them suitable for general-purpose memory testing where comprehensive fault detection is necessary without incurring prohibitive complexity [24].

Table 2.1 shows the examples of test algorithms with their complexity and test operation sequences while Table 2.2 shows the examples of test algorithms with the complexity and fault coverage. The RDF and IRF FC are represented by SAF coverage since they have similar detection requirement [1].

Table 2.1 Example of several March test algorithm with their sequences

| Test Algorithm | <b>Test Complexity</b> | <b>Test Operation Sequences</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March C- [26]  | 10 <i>N</i>            | $(w0); \uparrow (r0, w1); \uparrow (r1, w0); \downarrow (r0, w1); \downarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | IA MA                  | (r1, w0);≎ (r0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| March CL [27]  | 12N                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PMOVI [28]     | 13 <i>N</i>            | <ul> <li>\$\psi\$ (w0); \$\phi\$ (r0, w1,r1); \$\phi\$ (r1, w0, r0); \$\psi\$ (r0, w1, r1); \$\psi\$ (r1,w0, r0);</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| March RAW1     | 13N                    | (w0);  (w0, r0);  (r0);  (w1, r1);  (r1);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [29]           | TI TEKNIKA             | (w1, r1);  (r1);  (w0, r0);  (r0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| March LR [30]  | 14 <i>N</i>            | $\updownarrow (w0); \lor (r0, w1); \uparrow (r1, w0, r0, w1); \uparrow (r1, w0, w1); \uparrow (r1, w0, r0, w1); \uparrow (r1, w0, w1); \uparrow (r1, w0, w1); \downarrow (r1, w0, w$ |

|                |                        | $w0)$ ; $\uparrow$ $(r0, w1, r1, w0)$ ; $\uparrow$ $(r0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| March SR [31]  | 14 <i>N</i>            | $(w0); \uparrow (r0, w1, r1, w0); \uparrow (r0, r0); \uparrow$ $(w1); \lor (r1, w0, r0, w1); \lor (r1, r1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Modified       | 14N                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| March SR [32]  |                        | $(w1); \psi (r1, w0, r0, w0); \psi (r0, r0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| March C+ [33]  | 14 <i>N</i>            | (w0); $$ (r0, w1, r1); $$ (r1, w0, r0); $$ (r0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |