# IMPLEMENTATION AND PERFORMANCE ANALYSIS OF DROWSINESS DETECTION USING HARDWARE ACCELERATION ON PYNQ-Z1 FPGA

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

# IMPLEMENTATION AND PERFORMANCE ANALYSIS OF DROWSINESS DETECTION USING HARDWARE ACCELERATION ON PYNQ-Z1 FPGA

### **OOI HAN YI**

This report is submitted in partial fulfilment of the requirements for the degree of Bachelor of Computer Engineering with Honours

اونيوه سيتي تيكنيكل مليسيا ملاك

Faculty of Electronics and Computer Technology and Engineering Universiti Teknikal Malaysia Melaka

2024

**UNIVERSITI TEKNIKAL MALAYSIA MELAKA** FAKULTI TEKNOLOGI DAN KEJURUTERAAN ELEKTRONIK DAN KOMPUTER

#### BORANG PENGESAHAN STATUS LAPORAN PROJEK SARJANA MUDA II

Tajuk Projek

:

:

Implementation and Performance Analysis of Drowsiness Detection using Hardware Acceleration on PYNQ-Z1 FPGA 2023/2024

Sesi Pengajian

Saya <u>OOI HAN YI</u> mengaku membenarkan laporan Projek Sarjana Muda ini disimpan di Perpustakaan dengan syarat-syarat kegunaan seperti berikut:

- 1. Laporan adalah hakmilik Universiti Teknikal Malaysia Melaka.

- 2. Perpustakaan dibenarkan membuat salinan untuk tujuan pengajian sahaja.

- 3. Perpustakaan dibenarkan membuat salinan laporan ini sebagai bahan pertukaran antara institusi pengajian tinggi.

- 4. Sila tandakan ( $\checkmark$ ):

| SULIT*                 | (Mengandungi maklumat yang berdarjah<br>keselamatan atau kepentingan Malaysia<br>seperti yang termaktub di dalam AKTA<br>RAHSIA RASMI 1972) |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| TERHAD*                | (Mengandungi maklumat terhad yang<br>telah ditentukan oleh organisasi/badan di<br>mana penyelidikan dijalankan.                             |

| <b>TIDAK TERHAD</b>    | Disahkan oleh:                                                                                                                              |

| (TANDATANGAN PENULIS)  | (COP DAN TANDATANGAN PENYELIA)<br>DR. ANIS SUHAILA BINTI MOHD ZAIN<br>Persynth Karan<br>Fairl Teinskil Dir Karputan (Fitter)                |

| <br>                   | Universiti Teknologi kildisyeko kildisiya (UTakli)                                                                                          |

| Tarikh : . 20 Jun 2024 | Tarikh : <u>26 Jun 2024</u>                                                                                                                 |

\*CATATAN: Jika laporan ini SULIT atau TERHAD, sila lampirkan surat daripada pihak berkuasa/organisasi berkenaan dengan menyatakan sekali tempoh laporan ini perlu dikelaskan sebagai SULIT atau TERHAD.

# DECLARATION

I declare that this report entitled "Implementation and Performance Analysis of Drowsiness Detection using Hardware Acceleration on PYNQ-Z1 FPGA" is the result of my own work except for quotes as cited in the references.

| Signature | : |              |

|-----------|---|--------------|

| Author    | : | Ooi Han Yi   |

| Date      | : | 20 June 2024 |

•

# APPROVAL

I hereby declare that I have read this thesis and in my opinion, this thesis is sufficient in terms of scope and quality for the award of Bachelor of Computer Engineering with Honours

| Signature       | : |                                  |

|-----------------|---|----------------------------------|

| Supervisor Name | : | Dr. Anis Suhaila Binti Mohd Zain |

| Date            | : | 26 June 2024                     |

# DEDICATION

To my beloved parents, who have been my unwavering source of inspiration, motivation, and encouragement throughout my academic journey. Without your love, sacrifices, and steadfast support, I would not be where I am today. This paper is a testament to your unfailing faith in me, and I dedicate it to you with all my heart. To my supervisor, Dr. Anis Suhaila Binti Mohd Zain, and my co-supervisor, Ts. Dr. Sani Irwan Bin Salim, whose expertise, guidance, and mentorship have shaped my research and inspired me to push my limits. Your patience, constructive feedback, and valuable insights have helped me grow as a researcher and scholar. I am grateful for the opportunities you have given me to learn, collaborate, and contribute to the academic community. To Universiti Teknikal Malaysia Melaka, which has provided me with a rich academic environment, cutting-edge resources, and a platform to pursue my educational passion. My experience at this university has transformed me, allowing me to think critically, explore new ideas, and be exposed to different perspectives. I am honoured to be a part of this academic community, and I dedicate this paper to this university that has given me so much. Thank you.

### ABSTRACT

Drowsiness detection algorithms implemented on general-purpose processors perform well but suffer from portability issues and high power consumption. This project aims to overcome these limitations by designing and developing a drowsiness detection system on the PYNQ-Z1 FPGA platform. The project transitions from a software-based model to an FPGA-optimized design using high-level synthesis (HLS) of the Xilinx FINN compiler. By leveraging the parallel processing capabilities of FPGAs, the drowsiness detection is optimized for latency, power consumption, and resource utilization. The system monitors yawning and blinking, ensuring high performance while improving computational efficiency and power consumption. The integration of convolutional neural networks with FPGA frameworks demonstrates the synergy between neural network architectures and reconfigurable hardware. The results show that switching from a 6-bit model to a 2-bit model significantly reduced memory usage by 45.24%. Additionally, the quantized model on the PYNQ-Z1 reduces power consumption by 95.52% compared to the CPU. This research not only advances FPGA-based deployment, but also lays the foundation for future innovations in hardware design, neural networks, and artificial intelligence, enhancing the visual perception capabilities of computer vision and autonomous systems.

### ABSTRAK

Algoritma pengesanan rasa mengantuk yang dilaksanakan pada pemproses tujuan umum berfungsi dengan baik, namun mempunyai masalah isu mudah alih dan penggunaan kuasa yang tinggi. Projek ini bertujuan mengatasi kekurangan tersebut dengan membangunkan sistem pengesanan mengantuk pada platform FPGA PYNQ-Z1. Projek ini beralih daripada model berasaskan perisian kepada reka bentuk FPGA yang dioptimumkan dengan menggunakan pengkompil Xilinx FINN high-level synthesis (HLS). Dengan memanfaatkan keupayaan pemprosesan selari FPGA, pengesanan rasa mengantuk dioptimumkan untuk kependaman, penggunaan kuasa dan penggunaan sumber. Sistem akan memantau aktiviti menguap dan kelipan mata untuk membolehkan prestasi tinggi dapat dicapai sambil meningkatkan kecekapan pengiraan dan mengurangkan penggunaan kuasa. Penyepaduan Rangkaian Neural Konvolusi dengan rangka kerja FPGA menunjukkan sinergi di antara seni bina rangkaian neural dan perkakasan yang boleh dikonfigurasikan semula. Keputusan menunjukkan bahawa menukar daripada model 6-bit kepada model 2-bit mengurangkan penggunaan memori dengan ketara sebanyak 45.24%. Selain itu, model terkuantisasi pada PYNQ-Z1 mengurangkan penggunaan kuasa sebanyak 95.52% berbanding dengan CPU. Penyelidikan ini bukan sahaja memajukan

penggunaan berasaskan FPGA, tetapi juga meletakkan asas untuk inovasi masa hadapan dalam reka bentuk perkakasan, rangkaian saraf, dan kecerdasan buatan, meningkatkan keupayaan persepsi visual penglihatan komputer dan sistem autonomi.

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

### ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to all those who played an important role in the completion of this thesis. First, I would like to express my sincere gratitude to my supervisor, Dr. Anis Suhaila Binti Mohd Zain, and co-supervisor, Ts. Dr. Sani Irwan Bin Salim, for their unwavering guidance, valuable insights, and continuous support throughout the research process. Their expertise and encouragement were crucial in determining the direction of this work. Their expertise has greatly enriched the content and methodology of this thesis. Not to forget, special thanks to my beloved father and my beloved mother for their external support. I would also like to thank my good friends who always stayed by my side to cheer me up. I am lucky to have such a warm and loving family and friends. I would like to thank Universiti Teknikal Malaysia Melaka, Malaysia, for providing the necessary resources and research facilities to facilitate the implementation of this project. Finally, I would like to thank all my friends and supervisors who contributed in various ways to the completion of this thesis. Your support is indeed invaluable. This thesis is a testament to the spirit of cooperation and collective efforts of the people I met in my academic journey. Thank you all for your support and encouragement.

# **TABLE OF CONTENTS**

# Declaration Approval Dedication Abstract Abstrak Acknowledgements **Table of Contents List of Figures List of Tables** xiii List of Symbols and Abbreviations **CHAPTER 1 INTRODUCTION** 1.1 Introduction Background of Project 1.2 1.3 **Problem Statement**

Objectives 1.4 3 Scope of Work 1.5 4

i

ii

iv

v

xi

xiv

1

1

1

2

| 1.6 | Thesis Layout                                                  | 4  |  |  |

|-----|----------------------------------------------------------------|----|--|--|

| СНА | PTER 2 BACKGROUND STUDY                                        | 6  |  |  |

|     |                                                                | 6  |  |  |

| 2.1 | Introduction                                                   |    |  |  |

| 2.2 | Drowsiness                                                     | 6  |  |  |

|     | 2.2.1 Physiological Based Approach                             | 7  |  |  |

|     | 2.2.2 Vehicle Based Approach                                   | 8  |  |  |

|     | 2.2.3 Behavioral Based Approach                                | 10 |  |  |

| 2.3 | Face Detection                                                 | 10 |  |  |

|     | 2.3.1 Haar Cascade Algorithm                                   | 11 |  |  |

|     | 2.3.2 Convolutional Neural Network Architecture                | 12 |  |  |

|     | 2.3.3 Skin Colour Technique                                    | 13 |  |  |

| 2.4 | Drowsiness Signs NKAL MALAYSIA MELAKA                          | 14 |  |  |

|     | 2.4.1 Eye Activities                                           | 15 |  |  |

|     | 2.4.1.1 Eye Blink                                              | 15 |  |  |

|     | 2.4.1.2 Eye Closure Duration (ECD)                             | 16 |  |  |

|     | 2.4.1.3 Percentage of Eyelid Closure (PERCLOS)                 | 16 |  |  |

|     | 2.4.2 Mouth Activities                                         | 17 |  |  |

|     | 2.4.2.1 Yawning                                                | 17 |  |  |

|     | 2.4.3 Combination of Few Parameters Drowsiness Signs Detection | 18 |  |  |

| 2.5 | Field Programmable Gate Arrays                                 | 19 |  |  |

vi

|     | 2.5.1  | High Level Synthesis                                                           | 20        |

|-----|--------|--------------------------------------------------------------------------------|-----------|

|     | 2.5.2  | PYNQ                                                                           | 21        |

| 2.6 | Litera | ture Review                                                                    | 22        |

|     | 2.6.1  | System-on-Chip Based Driver Drowsiness Detection and Warning System            | 22        |

|     | 2.6.2  | Heterogeneous FPGA-based System for Real-Time Drowsiness<br>Detection          | 23        |

|     | ALAY   | SIA                                                                            |           |

|     | 2.6.3  | Design of ADAS Fatigue Control System using Pynq z1 and Jetson<br>Xavier NX    | 24        |

|     | 2.6.4  | Instruction Set Extension of a RiscV Based SoC for Driver Drowsin<br>Detection | ess<br>25 |

|     | 2.6.5  | Real-Time Drowsiness Alert System from EEG Signal Based on FP                  | GA<br>26  |

|     | ••     |                                                                                |           |

|     | 2.6.6  | A Fast FPGA Hardware Accelerator for Remote Heart Rate Detection               | n         |

|     |        | Based on RGB Vision                                                            | 27        |

|     | 2.6.7  | Comparison of Related Literature Review                                        | 28        |

|     | 2.6.8  | Research Gap                                                                   | 29        |

| 2.7 | Sumn   | nary                                                                           | 29        |

| CHA | PTER   | 3 METHODOLOGY                                                                  | 31        |

| 3.1 | Introd | luction                                                                        | 31        |

| 3.2 | Projec | ct Planning                                                                    | 32        |

|     | 3.2.1  | Dataset Selection                                                              | 34        |

|     | 3.2.2  | FINN                                                                           | 35        |

vii

|     | 3.2.3 PYNQ-Z1 Board Implementation                   | 37 |

|-----|------------------------------------------------------|----|

| 3.3 | Model Preparation                                    | 37 |

|     | 3.3.1 Model Selection                                | 38 |

|     | 3.3.2 Model Quantization                             | 40 |

|     | 3.3.3 Model Training                                 | 42 |

|     | 3.3.4 Model Validation                               | 43 |

| 3.4 | Board Implementation                                 | 43 |

|     | 3.4.1 High-Level Synthesis Conversion                | 44 |

|     | 3.4.2 Simulation, Synthesis and Bitstream Generation | 45 |

|     | 3.4.3 Deployment and Validation                      | 45 |

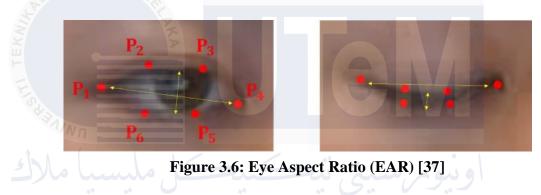

|     | 3.4.4 Eye State Determination                        | 46 |

|     | 3.4.5 Mouth State Determination                      | 47 |

| 3.5 | Performance Analysis                                 | 47 |

|     | 3.5.1 Inference Time                                 | 48 |

|     | 3.5.2 Resource Utilization                           | 48 |

|     | 3.5.3 Power Consumption                              | 49 |

|     | 3.5.4 Blink and Yawn Count                           | 49 |

|     | 3.5.5 Comparison with Traditional Platform           | 49 |

|     | 3.5.6 Trade-offs and Optimization Strategies         | 50 |

| СНА | PTER 4 RESULTS AND DISCUSSION                        | 51 |

viii

| 4.1 | Introduction                                           | 51 |  |  |

|-----|--------------------------------------------------------|----|--|--|

| 4.2 | Two-bit Quantization Model                             |    |  |  |

|     | 4.2.1 Resource Utilization                             | 52 |  |  |

|     | 4.2.2 Power                                            | 54 |  |  |

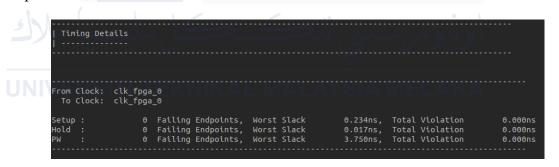

|     | 4.2.3 Clock Constraint and Frequency                   | 55 |  |  |

| 4.3 | Six-bit Quantization Model                             | 56 |  |  |

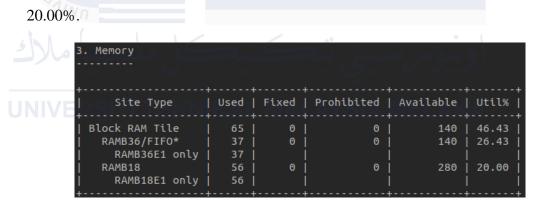

|     | 4.3.1 Resource Utilization                             | 57 |  |  |

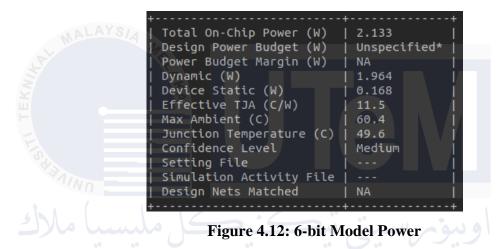

|     | 4.3.2 Power                                            | 59 |  |  |

|     | 4.3.3 Clock Constraint and Frequency                   | 60 |  |  |

| 4.4 | PYNQ-Z1 board                                          | 60 |  |  |

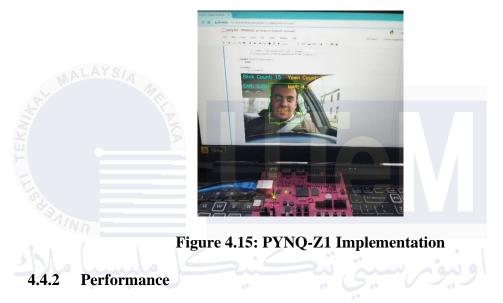

|     | 4.4.1 Validation                                       | 61 |  |  |

|     | 4.4.2 Performance IKAL MALAYSIA MELAKA                 | 61 |  |  |

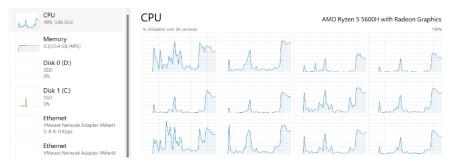

| 4.5 | Central Processing Unit                                | 62 |  |  |

|     | 4.5.1 Performance                                      | 62 |  |  |

|     | 4.5.2 Resource Utilization                             | 62 |  |  |

| 4.6 | Comparison Table                                       | 62 |  |  |

| 4.7 | Discussion                                             | 63 |  |  |

| 4.8 | Environmental and Sustainability                       | 65 |  |  |

|     | 4.8.1 Needs and Importance for Sustainable Development | 65 |  |  |

|     | 4.8.2 Impact of the Engineering Solution on Society    | 66 |  |  |

ix

| 4.9 | Summary                            | 66 |

|-----|------------------------------------|----|

| CHA | PTER 5 CONCLUSION AND FUTURE WORKS | 67 |

| 5.1 | Introduction                       | 67 |

| 5.2 | Conclusion                         | 67 |

| 5.3 | Future works                       | 68 |

| 5.2 | Conclusion                         | 6  |

# REFERENCES

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

70

# LIST OF FIGURES

| Figure 2.1: Electroencephalogram (EEG) Signals | 8  |

|------------------------------------------------|----|

| Figure 2.2: Lane Departure Warning             | 9  |

| Figure 2.3: Haar Cascade Algorithm             | 11 |

| Figure 2.4: CNN architecture                   | 13 |

| Figure 2.5: Skin Colour Detection              | 14 |

| Figure 2.6: Eye                                | 16 |

| Figure 2.7: PYNQ Framework                     | 21 |

| Figure 3.1: Flow Chart                         | 33 |

| Figure 3.2: WIDER DACE Dataset                 | 34 |

| Figure 3.3: Yawning Detection Dataset (YawDD)  | 35 |

| Figure 3.4: FINN Compiler                      | 35 |

| Figure 3.5: PYNQ-Z1 FPGA                       | 37 |

| Figure 3.6: Eye Aspect Ratio (EAR)             | 46 |

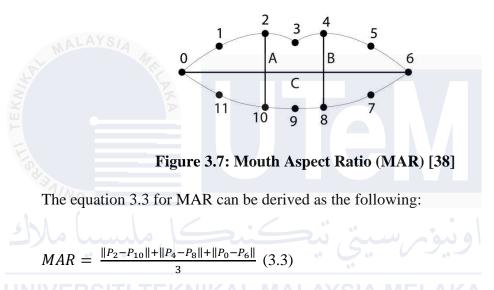

| Figure 3.7: Mouth Aspect Ratio (MAR)           | 47 |

| Figure 4.1: 2-bit Quantized Model              | 52 |

| Figure 4.2: 2-bit Model Slice Logic            | 52 |

| Figure 4.3: 2-bit Model Memory                 | 53 |

| Figure 4.4: 2-bit Model DSP                    | 54 |

| Figure 4.5: 2-bit Model Power              | 54 |

|--------------------------------------------|----|

| Figure 4.6: 2-bit Model Clock Summary      | 55 |

| Figure 4.7: 2-bit Model Timing Details     | 56 |

| Figure 4.8: 6-bit Quantized Model          | 56 |

| Figure 4.9: 6-bit Model Slice Logic        | 57 |

| Figure 4.10: 6-bit Model Memory            | 58 |

| Figure 4.11: 6-bit Model DSP               | 58 |

| Figure 4.12: 6-bit Model Power             | 59 |

| Figure 4.13: 6-bit Model Clock Summary     | 60 |

| Figure 4.14: 6-bit Model Timing Details    | 60 |

| Figure 4.15: PYNQ-Z1 Implementation        | 61 |

| Figure 4.16: Resource Utilization          | 62 |

| Figure 4.17: Parallelism                   | 64 |

| Figure 4.18: Sustainable Development Goals | 65 |

xii

# LIST OF TABLES

| Table 2.1: Literature Comparison              | 28 |

|-----------------------------------------------|----|

| Table 3.1: Yolov3-Tiny Architecture           | 39 |

| Table 3.2: Quantized Yolov3-Tiny Architecture | 41 |

| Table 4.1: Performance on PYNQ-Z1             | 61 |

| Table 4.2: Performance on CPU                 | 62 |

| Table 4.3: Result Comparison                  | 63 |

|                                               |    |

|                                               |    |

# LIST OF SYMBOLS AND ABBREVIATIONS

| FPGA    | :   | Field Programmable Gate Array |

|---------|-----|-------------------------------|

| SoC     | :   | System on Chip                |

| CNN     | :   | Convolutional Neural Network  |

| ReLU    | :   | Rectified Linear Unit         |

| ONNX    | :   | Open Neural Network Exchange  |

| HLS     | :   | High-Level Synthesis          |

| YawDD   | :   | Yawning Detection Dataset     |

| EAR     | ببا | Eye Aspect Ratio              |

| MAR     | ÷   | Mouth Aspect Ratio            |

| PERCLOS | :   | Percentage of Eyelid Closure  |

| ECD     | :   | Eye Closure Duration          |

| YOLO    | :   | You Only Look Once            |

| ECG     | :   | Electrocardiogram             |

| EEG     | :   | Electroencephalogram          |

| HRV     | :   | Heart Rate Variability        |

| LDW     | :   | Lane Departure Warning        |

| SWA     | :   | Steering Wheel Angle          |

|         |     |                               |

## **CHAPTER 1**

This chapter is divided into 5 sections. Section 1.2 will discuss the background study for the project followed by the problem statement in Section 1.3. The objectives of the project are discussed in Section 1.4 and the scope of the work is discussed in Section 1.5. The thesis layout will be introduced in Section 1.6.

#### **1.2 Background of Project**

Drowsiness is a state of being drowsy, tired, exhausted, or mentally or physically weak. A sleepy person has a low concentration level, which may make it difficult for them to maintain a certain level of focus. If this happens to a driver, a mechanic operating a heavy machine, or a railway operator, it may lead to an accident. Car accidents are one of the fatal accidents and are considered a major problem in society. In Malaysia, a study by the Malaysian Institute of Road Safety Research (MIROS) reported that fatigue is one of the biggest causes of car, truck, and bus accidents. In addition to this, another study conducted by MIROS on commuter accident victims in the Klang Valley reported that about 15% of them were involved in accidents due to drowsiness or fatigue [1].

Drowsiness detection analysis has become an interesting field, and many methods have been introduced based on different categories of invasive and non-invasive. With invasive methods, the subject needs to attach a sensory device (such as electrodes) to the body to measure signals from certain parts of the body (such as brain signals and heart signals). This can be uncomfortable for the subject, and any large movements can affect the signal. In contrast, non-invasive methods are more user-friendly, flexible, and more acceptable as they do not require any connection to the human body. But as of now, we know that deploying drowsiness detection on traditional computing platforms such as CPUs and GPUs often encounters difficulties, including excessive power consumption, high cost, and heat dissipation issues.

This project aims to implement drowsiness detection by analyzing the signs of drowsiness through eye and mouth activities using non-invasive techniques focusing on image processing methods. By the end of the project, it is expected that the developed algorithm will be able to detect blink and yawn with low latency within the limited resource constraints of the FPGA.

#### **1.3 Problem Statement**

The implementation of drowsiness detection is usually done on CPUs and GPUs because they have better speed and resources [2]. However, the energy and processing requirements of the drowsiness detection process remain high in pursuit of higher throughput. This project aims to address the power consumption issue by studying the implementation of drowsiness detection using FPGAs. This is because FPGAs have become a possible alternative for implementing drowsiness detection. After all, they consume less power and fewer resources than traditional computing platforms. FPGAs are known for their portability, reconfigurability, and power consumption levels. FPGA implementation also means the algorithm is embedded in the system while only a single board deployment is required.

The basic idea to solve the problems of traditional computing platforms is to reduce their high-power consumption and use the parallel processing and reconfigurable capabilities of FPGAs to provide a more economical and effective platform for implementing drowsiness detection. Energy efficiency is crucial to ensure drowsiness detection can operate for extended periods without draining the power source in the vehicle system. However, the challenges of doing so are also foreseeable. Due to the resource and power limitations and architecture of FPGAs, several efforts need to be made to implement drowsiness detection on FPGAs successfully [3]. Analysis is also required to validate the issues with traditional computing platforms and FPGA-based drowsiness detection solutions. The need for energy-efficient hardware acceleration of drowsiness detection on FPGAs must be emphasized [4].

#### 1.4 Objectives

- i. To design and implement drowsiness detection on FPGA.

- To explore optimization techniques for improving the drowsiness detection performance on FPGA.

- iii. To analyze FPGA-based drowsiness detection performance in terms of latency, power consumption, and resource utilization.

The primary goal of this project is to design and implement drowsiness detection on a field programmable gate array (FPGA) and verify it on a board to ensure that it works properly on the board. Due to the resource limitations of the FPGA, the drowsiness detection needs to be optimized to ensure that it can be implemented on the actual FPGA board. Finally, analyzing the performance of the FPGA-based drowsiness detection is also critical to gaining a deeper understanding of the project.

#### 1.5 Scope of Work

The scope of work for this project is to design and implement drowsiness detection on the Xilinx Zynq-7000 PYNQ-Z1 FPGA board using optimization techniques and to perform performance analysis of the drowsiness detection implemented on the board. The datasets used are the WIDER FACE dataset and the Yawning Detection Dataset (YawDD). The software and frameworks used are Docker, Brevitas, Jupyter Notebook, Vivado, and Vitis HLS.

### 1.6 / E Thesis Layout KAL MALAYSIA MELAKA

Chapter 1 provides the overall concept of the project and covers the introduction of drowsiness detection, problem statement, objectives, scope of work, and thesis layout. This will help us understand more details and the specific reasons for undertaking this project.

Chapter 2 includes a literature review based on the architecture and platform that will be used in the project. For this project, face detection, drowsiness sign methods, and the FPGA platform are the core architectures for drowsiness detection. The corresponding literature review will refine and delve into the concepts that are closely related to the project through diagrams. The chapter ends with a discussion section where all the reviewed methods are discussed based on their pros and cons. Chapter 3 presents the methodology of the implementation and analysis process of drowsiness detection architecture in the FPGA platform. This chapter will provide a flowchart of the project and describe each process in detail. In the last section, the techniques to obtain drowsiness sign analysis are described.

Chapter 4 presents the results obtained in this project and the performance analysis. The dataset will be validated on the FPGA to verify that drowsiness detection is well implemented. This chapter presents the results of accuracy, latency, power consumption, and resource utilization.

Chapter 5 is the last and will present the conclusion of this project after completing all the theories, results, and analysis. In addition, this chapter also involves suggestions for future work.

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

# **CHAPTER 2**

This chapter focuses on the background research and literature review of this project to investigate the latest progress in this field. The background research will cover drowsiness, face detection, signs of drowsiness, and field programmable gate arrays (FPGAs). In addition, a review of related projects and literature will be provided to illustrate the relevance and progress in these areas.

#### 2.2 Drowsiness

Drowsiness is a state of feeling tired due to lack of sleep, which can affect a person's level of consciousness and is particularly fatal for drivers. A drowsy person lacks a certain level of consciousness or alertness, which triggers the desire or tendency to fall asleep. Unfortunately, many fatigued drivers often experience microsleep. This is a state in which people do not realize that they are falling asleep after driving for hours due to a poor mental state. For drivers who drive for a long time, drowsiness is often caused by various medications, lack of sleep, and boredom. Drowsy drivers may lose control of their vehicles, resulting in accidents. So far, an increasing number of traffic accidents are caused by low driver alertness, which has become a serious problem in society. When drivers are drowsy, accidents tend to be more serious because they cannot react and control the vehicle to avoid crashing.

Three technologies can detect signs of drowsiness, namely physiological-based measurements, vehicle-based measurements, and behavior-based measurements. Generally, vehicle-based measurements are used in drowsiness detection research by observing driving patterns. Steering wheel movements, braking patterns, lane changes, and speed are examples of driving patterns that can be observed to indicate drowsiness. However, this approach is limited to the type of vehicle and road conditions. Instead, the presence of camera technology has enabled researchers to apply behavior-based measurement techniques that use image processing methods to detect drowsiness through the driver's behavior [5]. This approach is more user-friendly and easier to implement compared to intrusive methods. Head rotations, blinking patterns, gaze estimation, and yawning activities are behaviors that have been used as indicators to detect drowsiness stages.

#### 2.2.1 Physiological Based Approach

Physiological-based measurement is an invasive method to detect signs of drowsiness. This technique measures signs of drowsiness by acquiring signals from certain parts of the body, such as the heart rate, called electrocardiogram (ECG), or brain wave patterns, called electroencephalogram (EEG). A sensing device is required,

or multiple electrodes are used to acquire the signals. The electrodes are used to analyze drowsiness and fatigue states through EEG data. A method for predicting driver drowsiness by evaluating heart rate variability (HRV) through ECG devices is introduced [6]. Users need to place electrodes on body parts, which is uncomfortable, inefficient, and dangerous to implement in real-time.

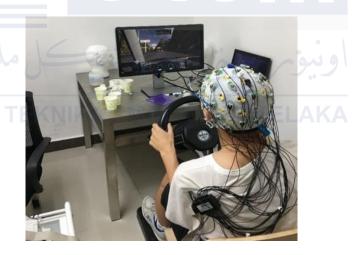

Therefore, as technology develops, researchers have found a way to develop new wireless sensing devices to record the rate of physiological signals. EEG channels are selected to record signals to detect sleepiness stages [6]. Certain mobile headphones are used to record EEG signals. Figure 2.1 shows a driver alertness monitoring system for drowsiness detection using wired wearable EEG, which is typically embedded in the driver's hat [7].

Figure 2.1: Electroencephalogram (EEG) Signals [7]

#### 2.2.2 Vehicle Based Approach

In addition to measurements based on physiological signals, another approach to detecting signs of drowsiness is to analyze the driver's driving pattern, mainly recording lane changes, steering wheel movements, and vehicle speed changes. This approach is a non-invasive method and does not require the device to be worn or attached to the user.

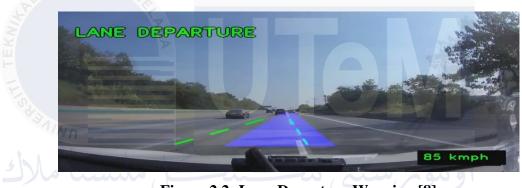

Figure 2.2 shows the Lane Departure Warning (LDW) system as one of the vehiclebased measurement categories [8]. The system completely relies on the detection of lane markings on the road, which requires the lane markings to be always visible for the system to work properly [9]. Occlusion caused by the preceding vehicle or weather conditions during heavy rain may degrade the performance of the system. Moreover, road conditions may lead to false detection of signs of drowsiness. For example, if there are potholes on the road, some drivers may suddenly change lanes. Therefore, the system is preferably implemented only on straight roads or highways.

Figure 2.2: Lane Departure Warning [8]

Steering Wheel Angle (SWA) is another approach used to detect signs of drowsiness in vehicles, where triaxial measurement of SWA is implemented. Driver drowsiness is monitored by calculating SWA data obtained from a sensor mounted on the steering column [10]. Analyzing the data is challenging because it is acquired from a real-time environment and random vibrations may cause the retrieved data to vary slightly. The main reason is that the vibration of the wheel and suspension system interferes with the frequency range of the steering signal. It turns out that SWA is not a perfect indicator of signs of drowsiness because it requires complex calculations and pre-processing operations. In addition, drowsiness detection based on steering wheel angle is not reliable to implement on FPGA because it requires the use of many sensors and is computationally complex.

#### 2.2.3 Behavioral Based Approach

The simplest way to detect whether a driver is drowsy is through his behavior because behavior shows the most obvious signs. For example, a drowsy driver tends to move his head frequently to avoid the feeling of falling asleep or a drowsy driver will show rapid blinking activities. Like vehicle-based measurements, this method is a non-invasive method and does not require the user to wear any equipment. Eye features are one of the common indicators for detecting signs of drowsiness. A system for detecting drowsy drivers is developed by combining three parameters of eye movement, namely, percentage of eye closure (PERCLOS), blinking frequency, and eye closure duration [11]. In addition to eye features, yawning is another method for measuring drowsiness based on driver behavior, which has been widely used. Moreover, the head pose is one of the obvious signs of sleepiness because sleepy drivers nod frequently. However, implementing this measure in real-time is dangerous because the sign of nodding indicates that the driver is already in the final stage of

drowsiness. TITEKNIKAL MALAYSIA MELAKA

#### **2.3** Face Detection

Face detection has received much attention and is one of the most promising applications in the field of image analysis. Face detection is an important component of biometrics, video surveillance, and human-computer interaction. Many image face detection methods have been proposed, which gave all researchers more inspiration to improve the performance, speed, and accuracy of the algorithms. For this, they have managed to obtain various algorithms for detecting faces, each with their characteristics, which will be compared in more detail in this chapter. Face detection is a critical initial step in detecting signs of drowsiness based on facial features, as successfully detecting a face will provide accurate true positive results for detecting other facial features. There are three main techniques for detecting faces and their facial features, including eyes and mouth, namely the haar cascade algorithm, the convolutional neural network architecture, and the skin colour technique.

#### 2.3.1 Haar Cascade Algorithm

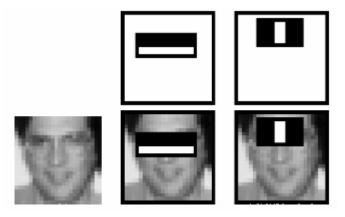

The Viola-Jones algorithm is widely used in face detection algorithms because it is the first face detection system ever [12]. The proposal of this framework can process images very quickly while achieving high detection rates. According to the research, the algorithm consists of three parts that work simultaneously to achieve fast and accurate detection. First, the image is converted into an "integral image", which allows for faster calculation of the features used by the detector. Second, the classifier used is an efficient and straightforward classifier built using the AdaBoost learning algorithm. Finally, the classifier is generated by combining weak classifiers into a "cascade", which allows for the rapid elimination of background areas of the image while spending more computation to improve face-like areas. Figure 2.3 shows more details on how the Viola-Jones algorithm works in face detection [13].

Figure 2.3: Haar Cascade Algorithm [13]

AdaBoost is a mechanism for cascading training of simple classifiers. By applying the AdaBoost learning algorithm, it can help reduce the number. The AdaBoost algorithm for feature selection and attention cascade can allocate computational resources to the image more efficiently [14]. Using symmetric AdaBoost can help produce linear combinations, which means that stability of positive and negative errors can be achieved using the AdaBoost algorithm.

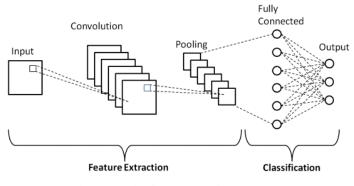

#### 2.3.2 Convolutional Neural Network Architecture

Convolutional neural networks (CNNs) have revolutionized face detection by automatically learning and extracting hierarchical features from raw images [15]. Unlike traditional approaches that rely on manually designed features and cascaded classifiers such as Viola-Jones algorithms, CNNs use multiple layers of convolutional filters to capture the spatial hierarchy in the data. This enables CNNs to recognize lowlevel features such as edges and textures in the initial layers, as well as more complex patterns such as facial structure and expression in deeper layers [15]. CNN methods typically involve training deep networks on large datasets of labeled images, enabling the network to learn complex patterns associated with faces. Recent advances, such as the development of architectures such as YOLO (You Only Look Once) and its variants, have further improved the speed and accuracy of CNN-based face detection, making it suitable for real-time applications.

CNNs are neural networks specialized for processing grid-like data such as images and videos [16]. They consist of multiple layers, including convolutional layers, pooling layers, and fully connected layers as shown in Figure 2.4. Convolutional layers apply filters to detect local patterns while pooling layers down to sample the data to reduce its size and dimensionality while retaining key information. Activation functions introduce nonlinearity to the network, enabling it to learn more complex patterns. Common activation functions are ReLU and sigmoid functions. Fully connected layers perform classification tasks based on the extracted features. CNNs are generally well-suited for tasks such as classification of image, object detection, and image segmentation.

Figure 2.4: CNN architecture [16]

Despite the many advantages of CNNs, they also face some challenges in implementation. Training and running CNNs are computationally expensive and require powerful hardware resources to ensure adequate performance. CNNs are prone to overfitting, especially when working with small datasets. In addition, due to the complex internal representation of CNNs, it is difficult to understand how they make decisions, resulting in poor feature interpretability. Overall, convolutional neural networks are an excellent tool for solving problems such as image classification because they can learn and extract relevant features from images [15]. Despite the challenges, CNNs need to be studied and analyzed on various platforms to better understand and apply them to improve human life.

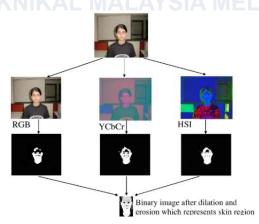

#### 2.3.3 Skin Colour Technique

For skin colour detection, the process is implemented using colour space transformation. A binary image is obtained and the pixel region around the largest connected component is considered as the search region. A robust face detection that employs hybrid skin colour under different illuminations is proposed [17]. Using the International Commission on Illumination colour space, skin-like pixels and skin contours are detected using a finite threshold and the facial region is identified based on that threshold. The application of skin colour in face detection is straightforward as it identifies the largest connected component, which includes various features such as eyes, nose, and mouth. However, a significant limitation is that false detections may occur when the algorithm encounters a skin colour background or when the user wears skin colour clothes.

To improve the accuracy of unidentified photos, three colour spaces which are RGB, YcbCr, and HSI are combined. This combination made it possible to develop a new skin colour-based detection algorithm, which improved accuracy. Figure 2.5 shows how the combination conducted the skin colour-based face detection algorithm [18]. There are several disadvantages to using skin colour as a feature for face detection. The facial colour representation obtained by the camera can be affected by factors such as ambient light and object motion. Different types of cameras can also produce significantly different colour values. In addition, colour cues affect the algorithm's sensitivity to changes in lighting colour, such as RGB to lighting intensity.

Figure 2.5: Skin Colour Detection [18]

#### 2.4 Drowsiness Signs

Detecting signs of drowsiness is a key factor in improving safety, especially in situations such as driving or operating heavy machinery. Monitoring eye activity has emerged as one of the most effective methods for detecting drowsiness. This method

involves analyzing various eye parameters that indicate a person's level of alertness. Based on the human face, many human behaviors can be measured as they contain rich information. This project focuses on detecting human behaviors related to signs of drowsiness based on the eyes and mouth as they provide key information for drowsy drivers and non-intrusive systems.

#### 2.4.1 Eye Activities

The human eye is one of the main components of the human body and contains rich information that can be used to distinguish the degree of sleepiness. A study was conducted to determine the parameters suitable for detecting sleepiness and found that eye characteristics are one of the best indicators for detecting sleepiness [19]. Based on these eye characteristics, three eye activity parameters can provide important insights into the vigilance state of a person. The key parameters include blink rate, duration of eye closure (ECD), and percentage of eyelid closure (PERCLOS).

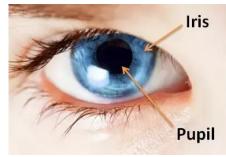

### 2.4.1.1 Eye Blink EKN KAL MALAYSIA MELAKA

Blinking is the action of opening and closing the eyelids at the same time and is one of the obvious signs of sleepiness. If a person is drowsy, he will blink more frequently than someone who is not sleepy [19]. Figure 2.6 shows the difference between the pupil colour and the white of the eye is the basis for detecting blinks [20]. The pupil is not a suitable parameter for detecting blinks due to its small size and easy occlusion. In addition, it may be occluded by light reflected from the glass. In terms of size, the iris is more suitable as a parameter for detecting blinks. Blink detection methods based on the iris area are easier to build even if they are occluded. The iris area comes from the aspect ratio of the iris bounding box. Blinks are observed according to the calculated ratio, and when the area is reduced, a blink of the eye is detected.

Figure 2.6: Eye [20]

#### 2.4.1.2 Eye Closure Duration (ECD)

Eye closure duration, commonly referred to as ECD, is another parameter that can be used to indicate drowsiness [21]. ECD can be defined as the amount of time the eyes remain closed. Typically, if a person is drowsy, their eyes will remain closed longer than usual. Eye closure duration measures the time interval during each blink cycle that the eyes remain closed. Prolonged eye closure is a clear sign of drowsiness as it reflects difficulty keeping the eyes open. Systems used to detect drowsiness will often set an ECD threshold to trigger an alarm to alert the individual or operator. ECD is determined by applying equation 2.1.

$$ECD = Total_{EveClose} \times Duration_{OneFrame}$$

(2.1)

#### 2.4.1.3 Percentage of Eyelid Closure (PERCLOS)

Blinking frequency and duration are reliable indicators of drowsiness. When people are drowsy, blinking frequency may decrease, and the duration of each blink increases. This is because drowsy people tend to have slower reaction times and reduced eye muscle control, resulting in longer blinks. Therefore, monitoring blinking patterns can provide real-time data on the onset of drowsiness. PERCLOS, or percentage of eyelid closure over the pupil over time, is the percentage of time that the eyes are closed for a specific period [22]. It is widely considered to be one of the most accurate indicators of drowsiness. High PERCLOS values are strongly associated with a higher risk of falling asleep, making it a key parameter in drowsiness detection systems. By continuously monitoring PERCLOS, these systems can issue timely warnings, helping to prevent accidents caused by drowsiness. Equation 2.2 shows how the PERCLOS is determined.

$$PERCLOS = \frac{Eye\ Close\ Time}{Total\ Time}$$

(2.2)

#### 2.4.2 Mouth Activities

In addition to eye activity, monitoring mouth activity can also provide valuable information about a person's drowsiness. Certain behaviors, such as yawning, are strongly associated with the onset of drowsiness and fatigue [21]. By referencing the mouth area, only one feature can be used to indicate a sign of sleepiness, which is yawning activity. Generally, there is a way to measure mouth opening to indicate yawning, mainly by tracking lip movement and quantifying the width of the mouth.

#### 2.4.2.1 Yawning

Yawning is an involuntary mouth-opening movement that usually occurs when a person feels tired or sleepy. Moreover, yawning can be classified as an early sign of sleepiness before a person enters a full-blown sleepy mode. Yawning is one of the prominent parameters that point out signs of sleepiness that a person exhibits [21]. Yawning is a physiological response that usually indicates tiredness and decreased alertness. The frequency and duration of yawning can serve as a reliable indicator of sleepiness. An increased number of yawns is usually associated with the need for rest and decreased concentration and alertness. When the detection identifies frequent yawning, it can signal that the individual is becoming drowsy and may need to take a break or engage in activities that increase alertness. This approach is particularly useful in environments such as driving, where maintaining high alertness is crucial for safety.

#### 2.4.3 Combination of Few Parameters Drowsiness Signs Detection

While individual parameters such as eye activity and mouth activity can provide valuable indicators of sleepiness, combining multiple parameters can improve the accuracy and reliability of drowsiness detection systems. By integrating data from a variety of sources, these systems can provide a more comprehensive assessment of an individual's alertness [23].

One effective approach is to simultaneously monitor blink rate, eye closure duration (ECD), percentage of eyelid closure (PERCLOS), and yawn frequency [23]. Each of these parameters provides unique information about the state of alertness. For example, increased eye closure duration and high PERCLOS values indicate prolonged eye closure, while frequent yawning indicates high levels of fatigue. By combining these indicators, the system can cross-validate the presence of sleepiness more strongly than relying on a single parameter.

Advanced drowsiness detection systems use machine learning algorithms to analyze the combined data in real-time. These algorithms can be trained on datasets containing a variety of sleepiness indicators, allowing them to identify complex patterns associated with sleepiness episodes. When multiple parameters reach their respective thresholds simultaneously, the system can issue a more reliable alarm, prompting the individual to take necessary actions to prevent accidents or errors. This multi-parameter approach greatly improves the effectiveness of drowsiness detection, ensuring timely and accurate responses in critical situations.

#### 2.5 Field Programmable Gate Arrays

A field programmable gate array (FPGA) is an integrated circuit that combines reconfigurability with high performance. Unlike traditional processors such as application-specific integrated circuits (ASICs), FPGAs can be reprogrammed, allowing users to customize them for specific needs and applications. This flexibility makes FPGAs well-suited for a wide range of applications, enabling researchers to reuse them in different projects [24].

FPGAs are semiconductor devices built around a matrix of configurable logic blocks (CLBs) interconnected by programmable connections. FPGAs consist of multiple logic blocks that act as building blocks and are configured to perform specific logic functions as required by the algorithm [24]. Common components in FPGAs include lookup tables (LUTs), flip-flops, multiplexers, block RAMs (BRAMs), and digital signal processing (DSP) units. LUTs are essentially tables that produce outputs based on given inputs. Flip-flops (FFs) maintain the state of the chip, storing single bits of information. Multiplexers select one input from multiple inputs. BRAMs are used as memory within FPGAs to store large amounts of data, while DSP units handle complex mathematical calculations.

FPGAs are programmed using a hardware description language (HDL) such as Verilog or VHDL [24]. These languages enable designers to specify the desired functionality of a digital circuit, detailing how logic blocks should be interconnected and how data should flow through the system. The inherent parallelism in FPGA processing gives them superior performance in certain applications, providing speed and efficiency advantages over traditional processors such as CPUs and GPUs. However, programming and optimizing FPGAs can be difficult without a full understanding of their architecture, resource utilization, and timing constraints, all of which must be carefully configured for optimal performance.

#### 2.5.1 High Level Synthesis

High-level synthesis (HLS), also known as C synthesis, is an automated process that converts abstract behavioral specifications of digital systems into register transfer level (RTL) structures that implement the specified behavior. HLS enables programmers to write algorithms in high-level programming languages such as C, C++, and Python. Through the HLS process, these high-level algorithms are converted into hardware description language (HDL) code that can then be used in FPGAs. This automation is critical because designing complex algorithms directly in HDL is a very complex task. HLS simplifies the implementation of complex models on FPGAs by automatically synthesizing high-level language descriptions into low-level HDL code.

Despite the many benefits of HLS, using HLS effectively requires considerable knowledge of the hardware architecture to be implemented. Designers must carefully manage data flow, memory usage, and performance constraints to ensure that the synthesized hardware performance is comparable to traditional computing platforms. Many FPGA vendors provide integrated HLS tools in their development environments. For example, Xilinx provides Vivado and Vitis as HLS tools for its FPGA boards.

In summary, high-level synthesis helps implement high-level language algorithms onto hardware platforms such as FPGAs that require low-level HDL coding. By automating the synthesis from high-level languages to low-level languages, HLS enables designers to implement complex algorithms on FPGAs more easily and efficiently.

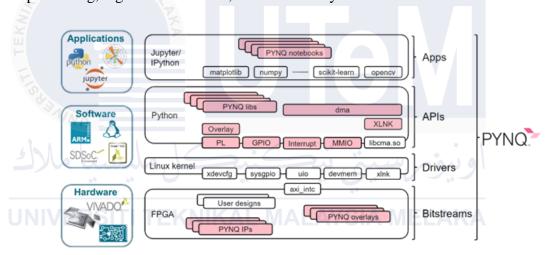

#### 2.5.2 PYNQ

PYNQ is an open-source project from AMD that aims to simplify the use of the Adaptive Compute Platform, as shown in Figure 2.7. By leveraging the Python language, Jupyter notebooks, and a broad ecosystem of Python libraries, PYNQ enables designers to harness the power of programmable logic and microprocessors to develop more advanced and innovative electronic systems [25]. PYNQ facilitates the creation of high-performance applications by enabling parallel hardware execution, high frame rate video processing, hardware-accelerated algorithms, real-time signal processing, high bandwidth I/O, and low latency control.

Figure 2.7: PYNQ Framework [25]

PYNQ is intended for a wide range of designers and developers, including software developers who want to exploit the capabilities of the Adaptive Compute Platform without resorting to traditional ASIC design tools, system architects seeking a user-friendly software interface and framework to rapidly prototype and develop Zynq, Alveo, and AWS-F1 designs, and hardware designers who want to make their designs accessible to the widest audience possible [25]. PYNQ is compatible with a wide range of AMD devices and boards, including Zynq 7000, Zynq UltraScale, Kria, Zynq RFSoC, Alveo Accelerator Board, and AWS-F1.

Jupyter Notebook is a browser-based interactive computing environment that allows users to create documents containing live code, interactive widgets, charts, explanatory text, equations, images, and videos. PYNQ-enabled boards can be programmed directly in Jupyter Notebook using Python. Developers can take advantage of hardware libraries and overlays on programmable logic that improve software performance on Zynq or Alveo boards and allow for customization of hardware platforms and interfaces [25]. By integrating these technologies, PYNQ makes it easier for developers to fully exploit the potential of adaptive computing platforms using a familiar and flexible programming environment.

#### 2.6 Literature Review

After comparing all the researcher journals that had been using the architecture of drowsiness detection in their project, there were six related projects. This part would make a comparison of the algorithm and platform they were using, which is known as the drowsiness detection algorithm and FPGA platform in their research.

# 2.6.1 System-on-Chip Based Driver Drowsiness Detection and Warning System

In the research of this article, the project aims to develop a driver drowsiness detection system that combines high accuracy and low response time, using a cost-effective method suitable for implementation on a single processor system [26]. The initial implementation of the project used PERCLOS and CNN methods, achieving over 98% accuracy using the MobileNetV2 network. However, this setup was too slow, taking over 2 seconds to detect drowsiness on a single processor. The final system uses a combination of facial landmarks, haar cascade classifiers, and eye aspect ratio (EAR) methods to achieve a balance between speed and accuracy.

The optimized system detects driver drowsiness with 92% accuracy and 0.8 seconds of latency. The system consumes as little as 2W of power and can run all day using a power bank of over 10,000 mAh [26]. The main drawback is the performance degradation at night, which can be mitigated by using a night vision camera. The audio module of the PYNQ-Z2 board is used to implement the sound warning system. The system outperformed methods using SVM, random forest, and naive Bayes, with an accuracy only 2% lower than the neural network-based application. In conclusion, the developed driver fatigue detection system has high accuracy and efficiency, making it a viable option for practical applications. The integration of different detection methods ensures strong performance even on low-cost hardware, although nighttime performance still needs to be improved.

2.6.2 Heterogeneous FPGA-based System for Real-Time Drowsiness Detection The project proposes an efficient hardware architecture to achieve real-time drowsiness detection by monitoring the driver's blinking behavior using the PERCLOS (Percentage of Eye Closure) metric [27]. The key features of the project include real-time detection, processing 250 VGA frames per second at low power consumption (1.6W) on a Xilinx Zynq XC7Z020 FPGA SoC. In terms of efficiency and performance, the proposed system is 33.3 times faster and occupies 2.6 times less area than the state-of-the-art system, enabling efficient integration into modern vehicles. In terms of hardware-software co-design, the project adopts a hybrid hardware-software approach to balance the computational load. Time-consuming tasks such as face detection and eye state monitoring are offloaded to dedicated hardware accelerators designed using high-level synthesis (HLS). In terms of preprocessing to improve accuracy, the system includes pre-processing steps such as RGB to grayscale conversion and histogram equalization to improve detection accuracy under different lighting conditions.

As for face and eye detection, the architecture uses the Viola-Jones face detection algorithm and a novel eye state analysis method based on the standard deviation of the saturation channel in the HSV colour space [27]. The system calculates PERCLOS parameters by analyzing the eye closure rate over time to help determine the driver's drowsiness. In terms of robustness and adaptability, the design can adapt to different environmental conditions, such as lighting changes, by setting appropriate eye state detection thresholds during the calibration phase. Overall, this project demonstrates significant progress in the field of Advanced Driver Assistance Systems (ADAS) by providing a robust, efficient, and real-time solution to detect driver drowsiness, thereby improving road safety.

# 2.6.3 Design of ADAS Fatigue Control System using Pynq z1 and Jetson Xavier

This project aims to develop an Advanced Driver Assistance System (ADAS) that uses computer vision techniques to detect driver fatigue and drowsiness [28]. It utilizes two main platforms, Pynq Z1 and Jetson Xavier NX, using their capabilities for efficient processing and detection. The system consists of several steps, namely training a classifier for facial feature detection using Haar techniques, acquiring and processing images, detecting faces and using facial landmark algorithms, and finally analyzing the state of the driver's eyes to determine fatigue. Eye aspect ratio (EAR) is used to detect whether the eyes are open or closed, providing a basis for determining the driver's alertness. Various video resolutions were tested to evaluate the performance of the system on different platforms. Jetson Xavier NX showed superior performance and faster processing time compared to Pynq Z1 and CPU-based implementations [28]. For example, for a video resolution of 1024x768 pixels, Jetson Xavier NX is 18.75 times faster than Pynq Z1 and 2.62 times faster than the CPU implementation. This project successfully designed and implemented a robust and low-cost driver fatigue detection system on the Jetson Xavier NX and Pynq Z1 platforms. The system was proven to be effective in real-time detection with significant speed advantages and design flexibility.

# 2.6.4 Instruction Set Extension of a RiscV Based SoC for Driver Drowsiness Detection

This paper presents a driver drowsiness detection (DDD) system implemented using a modified RiscV processor on an FPGA [29]. The system uses a trained convolutional neural network (CNN) to classify four driver expressions, which are distracted, natural, sleeping, and yawning, achieving 81.07% accuracy on validation data. The RiscV processor is enhanced with three custom instructions (custom store, conv2d(2×2), and MAC) to increase computation speed. The latency of the modified processor is improved by 1.7 times compared to the base processor. Automotive companies have invested heavily in systems that detect drowsiness and alert drivers to prevent accidents. Neural networks, especially CNNs, are known for their high accuracy in classification tasks, making them well-suited for drowsiness detection. Implementing these networks on FPGAs offers a viable solution due to the adaptability and efficiency of this hardware.

Due to limited memory on low-cost FPGAs, the CNN model is designed with a small number of weights and biases [29]. Dynamic memory allocation is employed to efficiently manage intermediate variables, and custom instructions are used to improve

performance. These optimizations ensure that the system can run on resourceconstrained hardware without significantly reducing accuracy. This paper shows that extending the instruction set of the RiscV processor with custom instructions can significantly improve the performance of a CNN-based driver drowsiness detection system implemented on an FPGA. The approach operates within the memory constraints of low-cost FPGAs while balancing the need for accuracy and computational efficiency.

#### 2.6.5 Real-Time Drowsiness Alert System from EEG Signal Based on FPGA

The project presents a comprehensive approach to detecting driver drowsiness using EEG signals processed in real-time on an FPGA platform [30]. The system uses EEG signals to monitor brain activity, capturing data indicating the driver's alertness level. FPGAs, selected for their high-speed processing capabilities and flexibility, process these signals using complex algorithms designed to accurately detect drowsiness. The primary goal is to alert the driver in a timely manner, thereby preventing accidents caused by drowsiness. The implementation involves capturing EEG signals through electrodes placed on the driver's scalp, which are then amplified and digitized for processing by the FPGA. The algorithm developed for this purpose classifies the EEG data into various states of alertness. This classification is achieved using machine learning techniques that are trained to recognize patterns in the EEG data that correspond to different levels of drowsiness.

The real-time nature of the system ensures that any signs of drowsiness are detected immediately, and an alert is issued to the driver. The project results demonstrate that the FPGA-based system is capable of high-precision real-time processing, making it a viable solution for integration into vehicles to improve safety [30]. Using FPGAs allows for a balance of speed and power efficiency, which is critical for in-vehicle applications. The study concluded that the system not only meets the performance requirements for real-time drowsiness detection but also provides a scalable and costeffective solution for automotive safety systems.

# 2.6.6 A Fast FPGA Hardware Accelerator for Remote Heart Rate Detection Based on RGB Vision

This project focuses on developing a hardware accelerator to estimate heart rate from video recorded by an RGB camera using a FPGA [31]. The technology used is remote photoplethysmography (rPPG), which detects physiological signals by analyzing subtle colour changes on the skin surface. This FPGA-based implementation aims to significantly increase computational speed compared to traditional software methods, making it suitable for real-time applications such as heart failure early warning for athletes and driver drowsiness detection. The core of the system involves capturing images using an RGB camera, processing the data to extract the blood volume pulse, and then determining the heart rate. The process begins by selecting a region of interest (ROI) on the subject's face where the underlying physiological signals are strongest. The data is then preprocessed to remove noise, center, and whiten to facilitate independent component analysis (ICA). ICA helps separate the blood volume pulse from other signals by maximizing their statistical independence.

The transformed signal is then analyzed in the frequency domain to identify peaks corresponding to the heart rate. The FPGA implementation of the algorithm offers several advantages, including reduced computation time and improved accuracy [31]. The study showed that the system can achieve heart rate detection accuracy of  $-0.76 \pm$

5.09 bpm and  $-0.70 \pm 8.71$  bpm in short recording times of 16 seconds and 8 seconds, respectively. This performance exceeds previous methods and effectively combines speed and accuracy. The ability of FPGAs to process data makes it an excellent choice for applications that require immediate physiological monitoring and response.

#### 2.6.7 Comparison of Related Literature Review

Table 2.1 compares 6 related studies, understands the differences with previous research results, and compares FPGA-based drowsiness detection.

| Board                                                  | Latency               | Power  | Method                      | <b>Pros and Cons</b>                                                                                                                             |

|--------------------------------------------------------|-----------------------|--------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA (Xilinx<br>PYNQ-Z2)<br>[26], 2022                 | 0.8ms in<br>640x480   | 2W     | - Haar Cascade<br>- EAR     | Advantages<br>Outperformed methods<br>using SVM, random forest,<br>and naive Bayes<br><u>Disadvantages</u><br>Performance degradation a<br>night |

| FPGA (Xilinx<br>ZYNQ XC7Z020)<br>[27], 2022            | 250 fps in<br>640x480 | 1.6W   | - Haar Cascade<br>- PERCLOS | Advantages<br>Low latency<br><u>Disadvantages</u><br>No Mouth Activity                                                                           |

| FPGA (Xilinx<br>PYNQ-Z1)<br>[28], 2022                 | 12s in<br>720x576     |        |                             | Disadvantages<br>High latency                                                                                                                    |

| Jetson Xavier NX<br>[28], 2022                         | 0.2s in<br>320x240    | -      | - Haar Cascade<br>- EAR     | <u>Advantages</u><br>Low latency<br><u>Disadvantages</u><br>Eye Activity Only                                                                    |

| FPGA (Xilinx<br>Nexys 4 DDR)<br>[29], 2022             | 231ms in<br>320x240   | -      | - CNN                       | <u>Advantages</u><br>1.7 frame rate improvemen<br><u>Disadvantages</u><br>High memory usage                                                      |

| FPGA (Xilinx)<br>[30], 2021                            | -                     | 1.116W | - EEG Signal                | <u>Advantages</u><br>Low Power Consumption<br><u>Disadvantages</u><br>Intrusive method                                                           |

| FPGA (Intel<br>Altera DE-10<br>Standard)<br>[31], 2024 | 16s in<br>640x480     | -      | - Heart Rate Detect         | <u>Advantages</u><br>RGB Vision<br><u>Disadvantages</u><br>High latency                                                                          |

#### Table 2.1: Literature Comparison

#### 2.6.8 Research Gap

The review "A High Performance and Robust FPGA Implementation of a Driver State Monitoring Application" by Christakos, P. et al. points out areas we can focus on to push the state of the art in drowsiness detection [32]. As mentioned in the paper, optimizing the drowsiness detection computation process is critical. This involves further extending and optimizing the rules to improve the robustness, and dynamically choosing the appropriate shape alignment ratio. In addition, access optimization requires more research on other data access methods and further improvements in hardware acceleration techniques. Proper management of scheduling and allocation issues, as detailed in the paper, can significantly improve the performance of FPGA implementations. Given the current research gaps in this area, it is worth further exploration.

### **J2.7 VE Summary EKNIKAL MALAYSIA MELAKA**

The literature review comprehensively analyzes the existing research on drowsiness detection using FPGAs. It explores the basic concepts in depth, surveys related research, and identifies gaps in current research. This background study places the research in the broader field of hardware acceleration, highlighting the rationale for choosing FPGAs. This chapter lays the foundation for the objectives of the paper, which include FPGA-based drowsiness detection design, optimization exploration, and comprehensive performance analysis.

Among the reviewed techniques, behavior-based measurements stand out as the most effective method due to their user-friendliness and cost-effectiveness. Driver drowsiness is mainly indicated by eye, mouth, and head behaviors. Advanced drowsiness signs such as nodding and turning your head indicate that the driver may be extremely drowsy or has entered a sleep mode. Therefore, eye and mouth behaviors are selected as early and obvious signs of drowsiness in this project.

Eye feature indicators include blinking, eye closure time (ECD), and percentage of eyelid closure (PERCLOS). Yawning is an indicator of mouth features. According to previous studies, these four indicators are most suitable for detecting sleepiness. A convolutional neural network feature-based method is adopted to analyze these indicators and use the parallel computing power of FPGA to accelerate the algorithm.

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## **CHAPTER 3**

To achieve the research objectives, the methodology used in this study includes the comprehensive development and implementation of a convolutional neural network based on drowsiness detection. The methodology emphasizes the fusion of machine learning and hardware acceleration and aims to optimize the deployment of trained models on FPGAs and leverage the capabilities of the PYNQ-Z1 board for drowsiness detection. The subsequent chapters will step through the processes involved in data preparation, model training, high-level synthesis (HLS), FPGA implementation, fatigue detection, verification, and performance evaluation. The methodology will describe the implementation of the project. The first step is to select the appropriate dataset. The next step is to train two convolutional neural network models with different weight quantization. Next, after validating the two models, they are exported

into model types that can be recognized by HLS. After that, HLS is used to convert the two models into HDL in preparation for the implementation of the models on the FPGA. After generating the bitstream of the models, the bit files of the two models are transferred to the FPGA, and the drowsiness detection algorithm is added for test execution verification. A thorough analysis will be performed to gain a deep understanding of the FPGA.

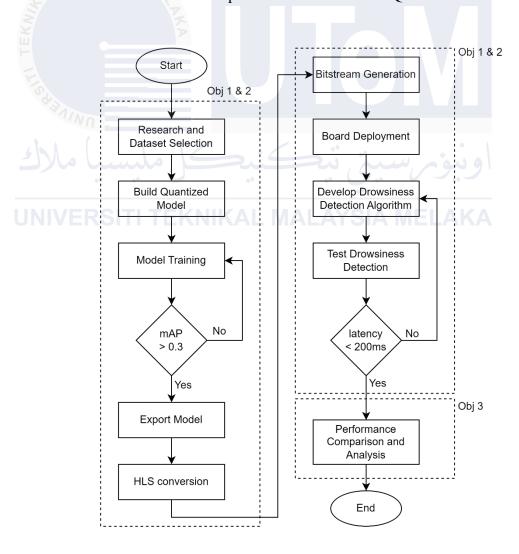

#### 3.2 **Project Planning**

The flowchart of this project is shown in Figure 3.1. The process starts with conducting background research and a comprehensive literature review. After this, a dataset is selected. Two models with different weights are trained on Google Colab using the WIDER FACE dataset. These models are then tested using the same dataset. The model configuration is adjusted until the mean average precision (mAP) for both training and testing exceeds 0.3. This threshold is chosen because the Yolov3-Tiny model also achieves a mAP of about 0.3 when quantized to 416×416 8-bit integers. Specifically, for the Yolov3-Tiny model in Xilinx Vitis, the mAP drops from 0.362 to 0.296 after quantization [33]. After achieving the desired mAP, the model is exported to the ONNX format to be compatible with the FINN library. The FINN library runs in a Docker container, which is installed on an Ubuntu system on the host. The advantage of using a Docker container is that it provides a self-contained package capable of running all necessary applications. The software can be easily installed on the host by running script commands.

After that, both the models are HLS converted using the FINN library. The HLS conversion and configuration steps optimize the hardware implementation of the models. Next, simulation and synthesis are performed to test the functionality of the

models before the actual deployment. After the synthesis process runs without any critical errors, bitstream generation is performed. The models are then deployed on the PYNQ-Z1 board by transferring the bit file, hardware configuration files, and drivers to the board and verifying them. After that, the drowsiness detection algorithm is added and verified using the yawning detection dataset, and the process continues if the latency remains at or below 200 milliseconds. If not, adjustments are made in the previous steps and retested. All the processes are logged and analyzed to get a report on the implementation and accuracy. These steps provide an in-depth understanding of the drowsiness detection implementation on the PYNQ-Z1 FPGA board.

**Figure 3.1: Flow Chart**

#### 3.2.1 Dataset Selection

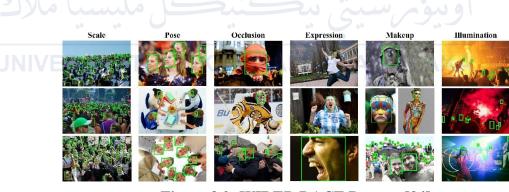

The WIDER FACE dataset is a good dataset for performing image recognition and classification tasks using convolutional neural networks [34]. The reason why the WIDER FACE dataset is suitable for the task is that it contains 60 event categories covering a wide range of real-world scenarios, which makes this dataset relevant for real-world applications, such as face detection of car drivers. The data quality of the WIDER FACE dataset is the key to its strength as it exhibits a high degree of variability in scale, pose, occlusion, expression, makeup, and lighting. The data quality that is closest to the real-world environment ensures that the model can adapt to images captured in real time. WIDER FACE is a large-scale face detection dataset that is often used as a benchmark. If a model is successfully implemented on WIDER FACE, it shows the capabilities of the model. Figure 3.2 shows the data in the WIDER FACE dataset and its labels.

Figure 3.2: WIDER DACE Dataset [34]

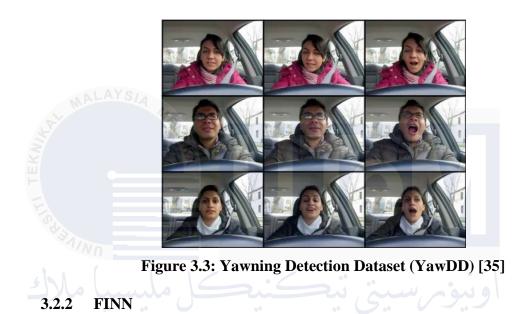

This project requires testing several scenarios to investigate the accuracy and speed of drowsiness detection implemented in FPGA. Six different video files from YawDD are used to investigate the accuracy and performance of drowsiness detection in FPGA. YawDD is a video dataset recorded by an onboard camera of drivers in real cars with various facial features, such as male and female, with and without glasses or sunglasses, different ethnicities, and in situations of talking, singing, silence, and yawning [35]. It is primarily used to develop and test algorithms and models for yawn detection but can also be used to recognize and track faces and mouths. The videos are captured under natural and varying lighting conditions as shown in Figure 3.3. The camera is mounted on the driver's dashboard. The set of videos provides different scenarios, each containing silent driving, driving while talking, and driving while yawning.

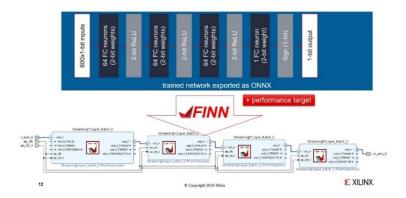

FINN is a Python package for FPGA machine learning inference [36]. The library uses a high-level synthesis language (HLS) to create firmware implementations of machine learning algorithms. It can be used to convert traditional open-source machine learning package models to HLS and can be configured for desired situations based on user needs. Figure 3.4 shows the hardware generation of the FINN compiler.

Figure 3.4: FINN Compiler [36]

With the help of open-source tools such as PyTorch and Brevitas, machine learning models can be quickly and efficiently converted to high-level synthesis (HLS) code, which can then be translated and executed on FPGAs. Subsequently, HLS projects can be used to generate IP that can be integrated into complex designs or used to develop cores for co-processing CPUs. Users are free to define many parameters of the algorithm to best meet their needs. The FINN package can quickly prototype machine learning algorithms in FPGAs, greatly reducing the time required to obtain results [36]. It also provides users with guidance on how to design the best machine learning algorithm for their application while balancing latency, resource consumption, and performance requirements. FPGAs can be specifically programmed to perform a certain task, in this case, evaluating a neural network given a set of inputs, and can therefore be highly optimized for that task through tricks such as pipelining and parallel evaluation. However, this means that dynamic remapping at runtime is effectively impossible.

#### JNIVERSITI TEKNIKAL MALAYSIA MELAKA

FPGAs also typically have a relatively low power cost compared to CPUs and GPUs. This enables FINN to build HLS code from compressed neural networks, achieving latency predictions in the microsecond range. The FINN tool saves the time investment required to convert neural networks into hardware design languages or even HLS code, allowing for rapid prototyping. In summary, FINN is a bridge between advanced machine learning model development and efficient FPGA implementation. By automating the translation process and handling FPGA-specific optimizations, FINN simplifies the deployment of machine learning models on hardware, providing a valuable tool for developers seeking to take advantage of FPGA acceleration.

#### 3.2.3 PYNQ-Z1 Board Implementation

With the new open-source framework PYNQ, embedded programmers can harness the power of the Xilinx PYNQ-Z1 development board to create programmable logic circuits. Python is used to program the PYNQ-Z1 and is used to test and develop the code. The process of importing and programming programmable logic circuits is very similar to that of software libraries, which are imported as hardware libraries and programmed through their respective APIs. The PYNQ development board uses the Zynq system-on-chip, which combines multiple functions in a single chip but still can use multiple chips on the board to perform the same desired function.

An ARM processor is also included in the Zynq SoC. This makes it possible to implement hardware acceleration of CPU, DSP, and other components on the same chip or board. The flexibility of the PYNQ board is also an advantage since it can reprogram the SoC as needed. In summary, the PYNQ-Z1 FPGA board was chosen because of its flexibility, reprogramming ability, and lower challenges compared to other FPGAs. The PYNQ image and its built-in Python interface with Jupyter Notebook in the Zynq SoC provide a huge advantage for implementing the drowsiness detection for this project on board. The physical board is shown in Figure 3.5.