# SOLAR POWERED LIGHTING SYSTEM VIA FIELD PROGRAMMABLE GATE ARRAY

## **CHAN YAN YI**

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

# SOLAR POWERED LIGHTING SYSTEM VIA FIELD PROGRAMMABLE GATE ARRAY

#### **CHAN YAN YI**

THIS REPORT IS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF ELECTRONIC ENGINEERING WITH HONOURS

**JULY 2021**

## **DECLARATION**

I declare that this report entitled "Solar Powered Lighting System via Field Programmable Gate Array" is the result of my own work except for quotes as cited in the references.

Date : 22 June 2021

## **APPROVAL**

I hereby declare that I have read this thesis and in my opinion this thesis is sufficient in terms of scope and quality for the award of Bachelor of Electronic Engineering with Honours.

## **DEDICATION**

Special thanks to my family, supervisor, and friends who supported and helped me complete the final year project.

#### **ABSTRACT**

Nowadays, electricity has become one of the essential needs to carry out people's daily routines. One of the applications of electricity is to provide electrical power to our home lighting system at night. However, most of the electricity is generated by burning fossil fuels. Fossil fuel is a non-renewable and finite resource, which causes pollution to the environment. Instead of burning fossil fuels, the renewable resource solar energy could be a great solution. The solar panel generates electrical power from solar energy stored in the lead-acid battery through the charging and discharging process. The solar-powered lighting system is controlled by the Xilinx Spartan 6 FPGA Development board. Field Programmable Gate Array is an integrated circuit containing programmable logic blocks and interconnection circuits. It is used as a system controller that is programmed by uses Verilog HDL according to different requirements. The output of this project is the lead-acid battery provides power to light on the LED when the Light Dependent Resistor detects darkness and the lead-acid battery in a fully-charged situation. Also, the lead-acid battery will change the state from discharging to the charging stage when low voltage is detected. This project involves developing a solar-powered lighting system via Field Programmable Gate Array and the analysis of the number of battery cycle life based on the different Depth of Discharge (DOD).

#### **ABSTRAK**

Pada masa kini, elektrik telah menjadi salah satu keperluan yang penting untuk menjalankan rutin harian masyarakat. Salah satu aplikasi elektrik adalah memberi tenaga elektrik ke sistem pencahayaan rumah kita pada waktu malam. Selain itu, elektrik juga memberi tenaga kepada peralatan elektrik, tetapi sebahagian besar tenaga elektrik dihasilkan dengan membakar bahan bakar fosil. Bahan bakar fosil adalah sumber yang tidak boleh diperbaharui dan terhad yang menyebabkan pencemaran kepada alam sekitar. Daripada membakar bahan bakar fosil, tenaga suria sumber yang boleh diperbaharui ialah satu penyelesaian yang baik. Panel solar menghasilkan tenaga elektrik dari tenaga suria yang tersimpan di dalam bateri asid plumbum melalui proses pengisian dan pengosongan. Sistem pencahayaan bertenaga suria dikendalikan oleh TI TEKNIKAL MALAYSIA MELAKA papan Xilinx Spartan 6 Field Programmable Gate Array. Field Programmable Gate Array adalah litar bersepadu yang mengandungi blok logik dan litar interkoneksi yang dapat diprogramkan. Ia digunakan sebagai pengawal sistem yang diprogramkan dengan menggunakan Verilog HDL mengikut keperluan yang berbeza. Hasilan dari projek ini adalah bateri asid plumbum yang memberikan kuasa untuk menyalakan LED apabila Perintang Bergantung Cahaya mengesan kegelapan dan bateri asid plumbm dalam keadaan yang diisi penuh. Juga, bateri asid plumbum akan mengubah keadaan dari tahap pelepasan bateri ke tahap pengecasan bateri apabila voltan rendah dikesan. Projek ini melibatkan pengembangan sistem pencahayaan bertenaga suria melalui Field Programmable Gate Array dan analisis jumlah hayat kitaran bateri berdasarkan peratus kedalaman perlepasan bateri yang berbeza.

#### **ACKNOWLEDGEMENTS**

At this moment, I would like to take this opportunity to thank all individuals who are directly or indirectly involved in supporting and assisting me in completing the Final Year Project (FYP), which is a compulsory course for students to complete degree studies at Universiti Technical Malaysia Melaka (UTeM).

First of all, I would like to thank Ir. Ts. Anuar Bin Jaafar, my supervisor, for continually guiding me during the completion of this project. Thank you for the experience and spiritual encouragement that will make this project a success. Also, his action of thought encourages me to always prepare before doing anything.

Next, I am very grateful to my family for their encouragement and financial UNIVERSITI TEKNIKAL MALAYSIA MELAKA support. Finally, thanks to my friends who helped to provide ideas and opinions.

# TABLE OF CONTENTS

|                           | 4 •       |

|---------------------------|-----------|

|                           | laration  |

| $\mathbf{p}_{\mathbf{c}}$ | iai auvii |

## Approval

### **Dedication**

| Abs  | tract MALAYSIA                      | i    |

|------|-------------------------------------|------|

| Abs  | trak                                | ii   |

| Ack  | nowledgements                       | iv   |

| Tab  | le of Contents                      | V    |

| List | of Figures                          | ix   |

|      | UNIVERSITI TEKNIKAL MALAYSIA MELAKA |      |

| List | of Tables                           | xii  |

| List | of Symbols and Abbreviations        | xiii |

| List | of Appendices                       | xiv  |

| CH   | APTER 1 INTRODUCTION                | 1    |

| 1.1  | Project Background                  | 1    |

| 1.2  | Problem Statement                   | 3    |

| 1.3  | Objectives                          | 4    |

| 1.4  | Scope of Work                       | 4    |

|     |                                                                  | vi |

|-----|------------------------------------------------------------------|----|

| 1.5 | Organisation Structure                                           | 5  |

| CHA | APTER 2 BACKGROUND STUDY                                         | 7  |

| 2.1 | Introduction                                                     | 7  |

| 2.2 | Solar Powered Lighting Systems                                   | 7  |

|     | 2.2.1 The System Operation of Solar Powered Lighting System      | 8  |

|     | 2.2.2 Solar Panel as a energy source                             | 8  |

|     | 2.2.3 Rechargeable Lead-Acid Battery as energy storage           | 10 |

|     | 2.2.4 Buck converter circuit for stable power generated          | 12 |

|     | 2.2.5 Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) | 15 |

|     | 2.2.6 Pulse Width Modulation as LED dimming control              | 17 |

| 2.3 | System Controller for Solar Powered Lighting System              | 19 |

|     | 2.3.1 Field Programmable Gate Array                              | 19 |

|     | 2.3.2 Arduinori TEKNIKAL MALAYSIA MELAKA                         | 21 |

|     | 2.3.3 PIC Microcontroller                                        | 21 |

| 2.4 | The Battery Lifecycle Estimation Method                          | 21 |

| 2.5 | Summary                                                          | 23 |

| CHA | APTER 3 METHODOLOGY                                              | 26 |

| 3.1 | Introduction                                                     | 26 |

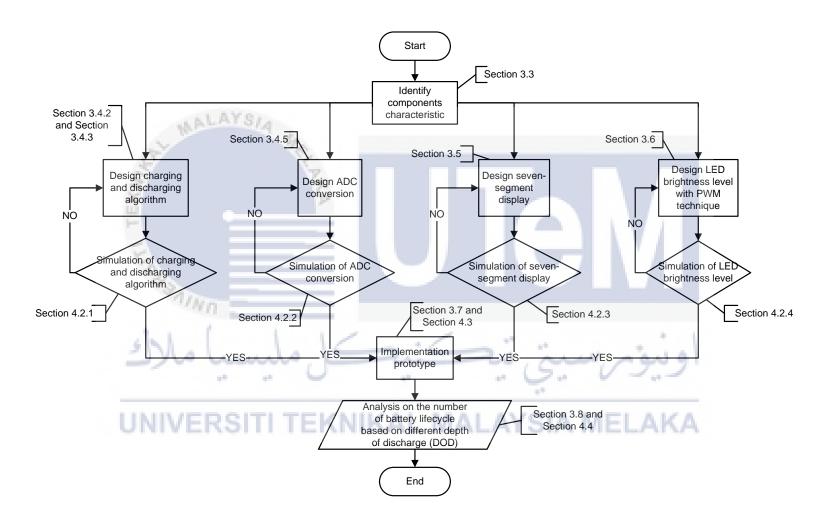

| 3.2 | Methodology Flowchart                                            | 26 |

| 3.3 | Components Characteristic                                        | 28 |

|     |                                                                           | vi  |

|-----|---------------------------------------------------------------------------|-----|

| 3.4 | Charging and Discharging Process of Solar Powered Lighting System         | 30  |

|     | 3.4.1 Clock Divider for Charging and Discharging process                  | 32  |

|     | 3.4.2 Charging Algorithm                                                  | 32  |

|     | 3.4.3 Discharging Algorithm                                               | 34  |

|     | 3.4.4 Switching Algorithm (MOSFET)                                        | 35  |

|     | 3.4.5 Analog-to-Digital Conversion                                        | 36  |

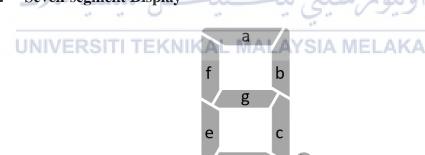

| 3.5 | Seven-Segment Display on FPGA board                                       | 37  |

|     | 3.5.1 Clock Divider for Seven-Segment                                     | 39  |

|     | 3.5.2 Seven-segment Display                                               | 39  |

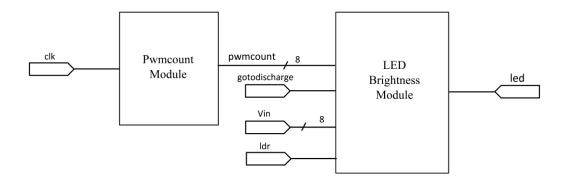

| 3.6 | LED brightness levels with PWM technique                                  | 41  |

| 3.7 | Prototype of the Solar Powered Lighting System                            | 43  |

| 3.8 | Analysis on the number of battery lifecycle based on the Depth of Dischar | rge |

|     | (DOD) UNIVERSITI TEKNIKAL MALAYSIA MELAKA                                 | 45  |

| 3.9 | Summary Summary                                                           | 46  |

| СНА | PTER 4 RESULTS AND DISCUSSION                                             | 47  |

| 4.1 | Introduction                                                              | 47  |

| 4.2 | Simulation results of Solar Powered Lighting System                       | 47  |

|     | 4.2.1 Simulation results of charging and discharging algorithm            | 47  |

|     | 4.2.2 Simulation results of analog-to-digital conversion                  | 50  |

|     | 4.2.3 Simulation results of seven-segment display                         | 50  |

|     |                                                                           |     |

4.2.4 Simulation results of LED brightness levels

51

| V | 1 | 1 | 1 |  |

|---|---|---|---|--|

| 4.3 | Prototype results of Solar Powered Lighting System                             | 52        |

|-----|--------------------------------------------------------------------------------|-----------|

| 4.4 | Analysis on the number of battery lifecycle based on the Depth of Discha (DOD) | rge<br>55 |

| 4.5 | Project Features                                                               | 57        |

| 4.6 | Summary                                                                        | 58        |

| СНА | PTER 5 CONCLUSION AND FUTURE WORKS                                             | 60        |

| 5.1 | Conclusion                                                                     | 60        |

| 5.2 | Future Work                                                                    | 61        |

| REF | ERENCES AYSIA                                                                  | 63        |

| APP | ENDICES UTEM                                                                   | 70        |

|     | اونيوسيتي تيكنيكل مليسيا ملاك                                                  |           |

|     | LINIVERSITI TEKNIKAL MALAYSIA MELAKA                                           |           |

# LIST OF FIGURES

| Figure 1.1 Scope of work                                                 | 5  |

|--------------------------------------------------------------------------|----|

| Figure 2.1 Polycrystalline vs Monocrystalline Solar Panels[20]           | 9  |

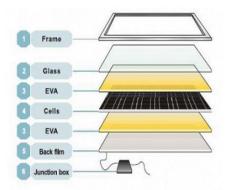

| Figure 2.2 The structure of monocrystalline solar panel[22]              | 9  |

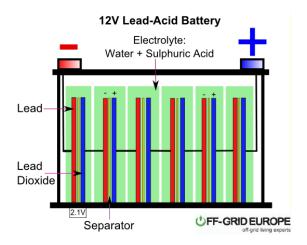

| Figure 2.3 Construction of a Lead-acid Battery[27]                       | 11 |

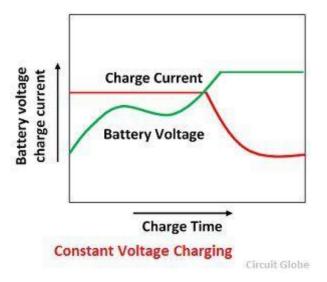

| Figure 2.4 Constant voltage charging[30]                                 | 12 |

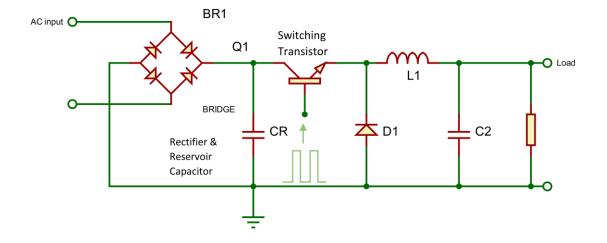

| Figure 2.5 Buck Converter Circuit with rectifier and reservoir capacitor | 13 |

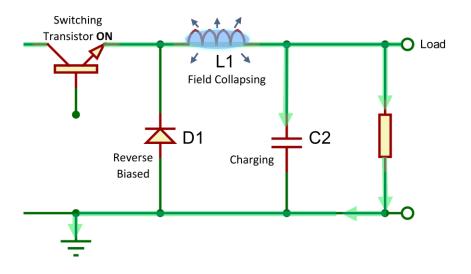

| Figure 2.6 Buck Converter when switched on                               | 13 |

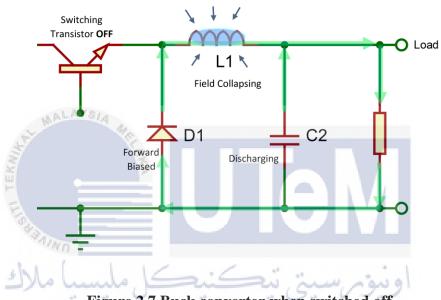

| Figure 2.7 Buck converter when switched off                              | 14 |

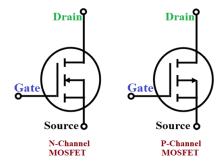

| Figure 2.8 Symbol of MOSFET[32]                                          | 15 |

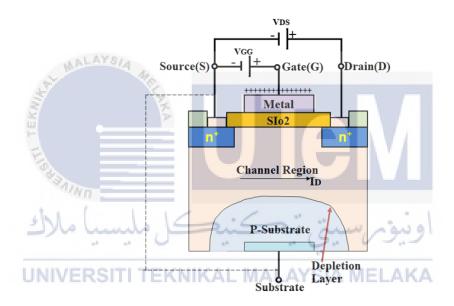

| Figure 2.9 The MOSFET block diagram [34]                                 | 16 |

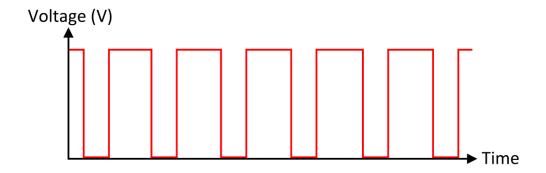

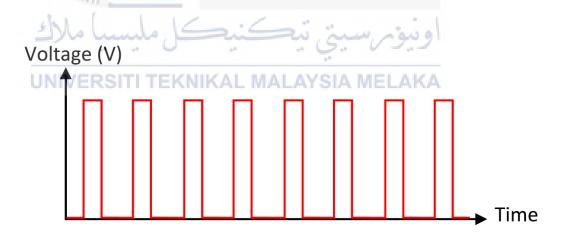

| Figure 2.10 PWM signal when LED dimming at 80% brightness                | 18 |

| Figure 2.11 PWM signal when LED dimming at 5% brightness                 | 18 |

| Figure 2.12 The internal structure of an FPGA[40]                        | 20 |

| Figure 2.13 Life cycle for GP1272 battery[47]                            | 23 |

| Figure 3.1 Methodology Flowchart                                         | 27 |

| Figure 3.2 Xilinx Spartan 6 FPGA Development Board                       | 28 |

| Figure 3.3 AD7822                                                        | 29 |

| Figure 3.4 NCE6008AS MOSFET                                              | 29 |

| Figure 3.5 Charging Process of Solar Powered Lighting System                            | 30                    |

|-----------------------------------------------------------------------------------------|-----------------------|

| Figure 3.6 Discharging Process of Solar Powered Lighting System                         | 31                    |

| Figure 3.7 RTL of a clock divider                                                       | 32                    |

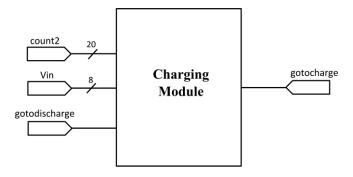

| Figure 3.8 RTL of the charging module                                                   | 32                    |

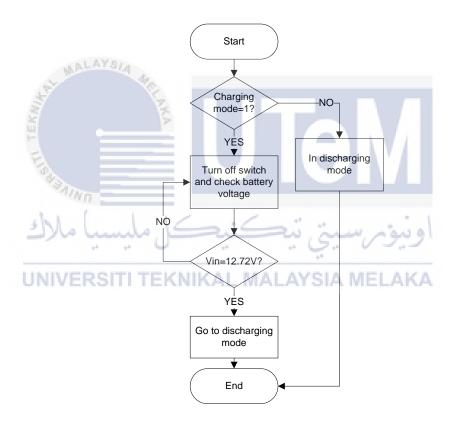

| Figure 3.9 Charging Algorithm                                                           | 33                    |

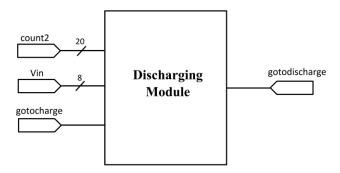

| Figure 3.10 RTL of the discharging module                                               | 34                    |

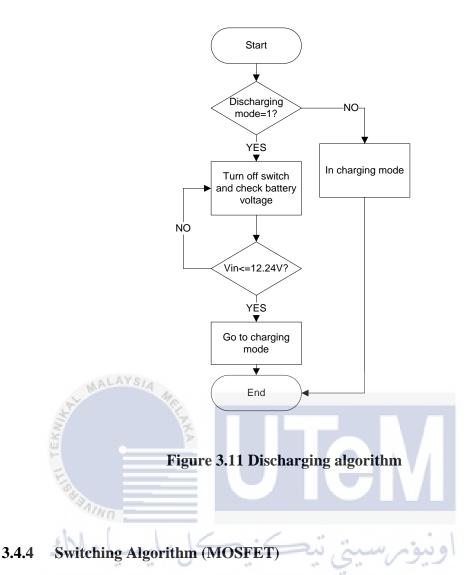

| Figure 3.11 Discharging algorithm                                                       | 35                    |

| Figure 3.12 RTL of the ADC conversion module                                            | 36                    |

| Figure 3.13 RTL of the seven-segment display module                                     | 37                    |

| Figure 3.14 The circuit of seven-segment display [50]                                   | 38                    |

| Figure 3.15 Seven-segment display using clock divider                                   | 39                    |

| Figure 3.16 The pin diagram of the seven-segment display                                | 39                    |

| Figure 3.17 RTL of the LED module                                                       | 42                    |

| Figure 3.18 Waveform for the 100% and 50% duty cycle of LED                             | 42                    |

| Figure 3.19 Voltage divider for the ADC protection SIA MELAKA                           | 43                    |

| Figure 3.20 MOSFET in charging circuit                                                  | 44                    |

| Figure 3.21 MOSFET in discharging circuit                                               | 44                    |

| Figure 4.1 Simulation result of charging mode when the FPGA detects fully charged       | the battery is 48     |

| Figure 4.2 Simulation result of charging mode when the system detects to of the battery | he low voltage<br>48  |

| Figure 4.3 Simulation result of discharging mode when the system dete is fully charged  | cts the battery<br>49 |

| Figure 4.4 Simulation result of discharging mode when the system dibattery voltage      | etects the low        |

| Y 1         |

|-------------|

|             |

| $\Lambda$ I |

|             |

| Figure 4.5 Simulation of switching mode                                             |     |

|-------------------------------------------------------------------------------------|-----|

| Figure 4.6 Simulation of <b>CONVST</b> signal in conversion process                 | 50  |

| Figure 4.7 The input voltage detected by FPGA                                       | 50  |

| Figure 4.8 The value displayed on the seven-segment                                 | 51  |

| Figure 4.9 Simulation result of 100% brightness of the LED                          | 51  |

| Figure 4.10 Simulation result of 50% brightness of the LED                          | 52  |

| Figure 4.11 Hardware circuit of the Solar Powered Lighting System                   | 52  |

| Figure 4.12 Voltage divider circuit                                                 | 53  |

| Figure 4.13 MOSFET Driver and N-type MOSFET circuit                                 | 53  |

| Figure 4.14 LED turn on with 50% brightness                                         | 54  |

| Figure 4.15 LED turn on with 100% brightness                                        | 54  |

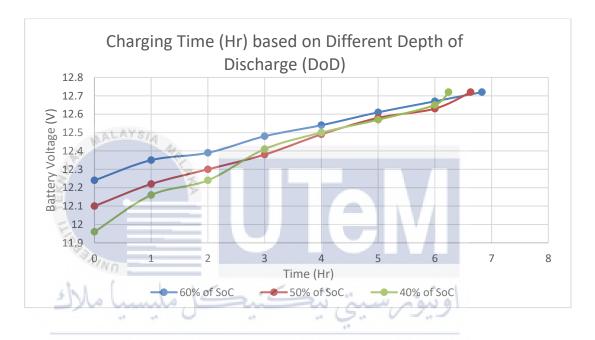

| Figure 4.16 Results graph for total charging time based on different Depth          | of  |

| Discharge (DOD)                                                                     | 55  |

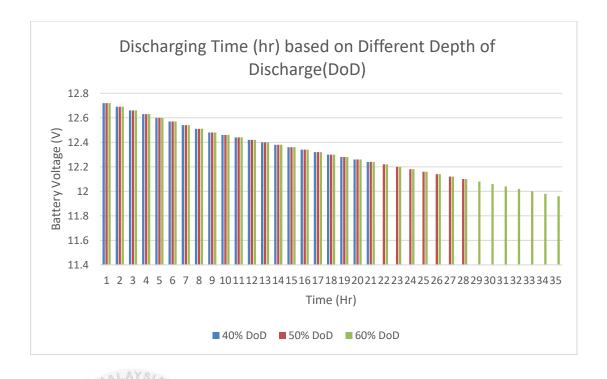

| Figure 4.17 Results graph for total discharging time based on different Depth       | of  |

| Discharge (DOD)                                                                     | 56  |

| Figure 4.18 Results graph of the number of battery life cycle based on different De | oth |

| of Discharge (DOD)                                                                  | 57  |

# LIST OF TABLES

| Table 2-1 Specification of the GP1272 Battery [48]                   | 22 |

|----------------------------------------------------------------------|----|

| Table 2-2 Project Summarize Table                                    | 25 |

| Table 3-1 State of Charge (SOC) of the 12V Lead-Acid Battery         | 30 |

| Table 3-2 The battery Voltage in binary and hex form                 | 40 |

| Table 3-3 The truth table of seven-segment with and without decimals | 41 |

| Table 3-4 LED Brightness                                             | 43 |

| Table 3-5 UCF file: I/O Port and the pin allocation                  | 45 |

| اونيوسيتي تيكنيكل مليسيا ملاك                                        |    |

| UNIVERSITI TEKNIKAL MALAYSIA MELAKA                                  |    |

#### LIST OF SYMBOLS AND ABBREVIATIONS

FPGA : Field Programmable Gate Array

DOD : Depth of Discharge

LED : Light Emitting Diode

LDR : Light Dependent Resistor

CO<sub>2</sub> : Carbon Dioxide

PWM : Pulse Width Modulation

MOSFET: Metal-Oxide-Semiconductor Field-Effect Transistor

RTL : Register Transfer Level

e.m.f : Electromotive Force

MPPT Maximum Power Point Tracking SIA MELAKA

# LIST OF APPENDICES

| Appendix A: | AD7822    | 70 |

|-------------|-----------|----|

| Appendix B: | NCE6008AS | 74 |

| Appendix C: | LM25101   | 76 |

| Appendix D: | GP1272    | 78 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Project Background

Global energy demand is increasing, the higher energy demand is also expected in the well-developed and developing countries in the coming decades. Besides that, growing populations and rising living standards would bring much more pressure on energy resources for many people in developing countries [1]. Due to the rise of energy demand, global electricity production has grown yearly since 1974, and most of the electricity production generated from combustion fuels, mostly with fossil fuels [2]. However, electricity produced by burning fossil fuels is harmful to the environment, the carbon dioxide,  $CO_2$  emissions produced by burning fossil fuels can pollute the air. The  $CO_2$  emissions and other greenhouse gases will be released when burning fossil fuel, contributing to global warming and climate change. Also, as non-renewable

resources, fossil fuels will run out or not be replenished for thousands or even millions of years [3].

Due to CO<sub>2</sub> will produce air pollution, it is important to use alternative energy resources for daily uses. Renewable energy is advisable to overcome this issue. Solar energy is a renewable energy source, and solar or photovoltaic (PV) cells are manufactured from silicon or other materials that directly convert sunlight into electricity. This technology offers a practical solution to various power application problems, and most importantly, no air pollution or greenhouse gases are generated by solar energy systems. The solar lighting system is one of the most common applications of solar energy. Since energy-saving lighting is an important factor in sustainable development and energy strategy, the combination of high-efficiency photovoltaics and light-emitting diodes (LEDs) can release solar lighting systems and provide realistic and energy-saving solutions for lighting systems.

A solar-powered lighting system provides power to the load by using sunlight as an energy resource, which means a typically battery-powered lighting system charged using a solar panel. The solar lighting system can come in all shapes and sizes based on different needs, it consisting of a solar panel, lead-acid battery, and LED lights as the output, and the energy stored in the battery is used to light the LED. More than to lights up the rooms, it is also possible to use a solar lighting system in areas that either has no effective 24-hour grid electricity or no grid electricity at all. A rechargeable lead-acid battery stores solar energy through the charging process and supplies power to the LEDs during the discharging process. Rechargeable batteries are commonly used in solar lighting systems because the solar array's electrical energy is not always consistent with the time needed for electrical power [4]. Among the types of batteries,

lead-acid batteries are popular because of their compatible price range, and they are highly affordable compared to other advanced technologies.

The use of LEDs in the lighting system will save energy, minimize CO<sub>2</sub> emissions and numerous advantages over conventional lamps: the better energy efficiency of lighting systems, longer lifecycle, less maintenance, higher flexibility and control of the light level, and lower power consumption and environment-friendly [5]. For the improved version, LEDs can have their light emission control known as dimming. Pulse Width Modulation (PWM) is used to control the luminous flux of the LED, which uses a square wave power supply for these applications, then the light flux is changed by varying the signal's duty cycle [5].

Besides the Field Programmable Gate Array (FPGA), different embedded systems were implemented before FPGA became popular for the solar-powered lighting system. The PIC family microcontroller is frequently used in the solar street light system to controls the solar street light system based on light detections, working with Light Dependent Resistor (LDR) [6][7][8]. In addition, Arduino UNO is also embedded in the solar lighting system to check the battery power and indicate that the discharge at a critical level [9]. However, the FPGA has recently become more widely used in the lighting system, mostly switching the lights by detecting movement[10] and controlling the LED dimming based on different scenarios[5].

#### 1.2 Problem Statement

Most researchers ignore developing the prototype or hardware of a solar-powered lighting system using FPGA[10][11]. However, the results might differ between the simulation and prototype due to the actual factors, such as temperature, weather, and

other factors. Hence, this is hard to determine the efficiency of the solar-powered lighting system using FPGA in real life.

There is a current paucity of evidence-based literature describing the impact of Depth of Discharge on the battery's lifespan [6][9]. Suhil *et al.* had mentioned that the conventional solar lighting system is suffering from the sudden death of light. The conventional solar lighting system always discharged until there is no more energy to light up the LED. When the battery is over-charged and over-discharged continuously, it could damage the battery and shorten its lifespan [7].

#### 1.3 Objectives

The objectives of this project are:

- 1. To develop a prototype of a solar-powered lighting system using FPGA.

- 2. To analyze the number of battery lifecycle based on the different Depth of Discharge (DOD) of a solar-powered lighting system.

(NIKAL MALAYSIA MELAKA

#### 1.4 Scope of Work

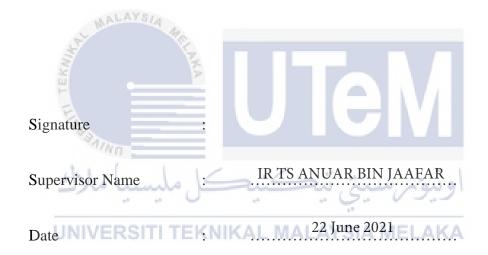

Figure 1.1 shows the block diagrams of the scope of work, including the hardware, software, and the technique applied. For the hardware, the Xilinx Spartan 6 FPGA Development board is the main component used to control the whole system, includes the charging mode and discharging mode. Next, this project will use a monocrystalline solar panel, in which the solar panel's maximum power is 30W, and the maximum power voltage and current of the solar panel are 18V and 1.67A. Additionally, this project will use a rechargeable lead-acid battery, and the model of the battery is GP1272, which a battery voltage is 12V, and the capacity is 7.2Ah. On the other hand, the buck converter is also used to step down the charging voltage. Furthermore, the

Light Dependent Resistor (LDR) will be used as an input sensor to detect light intensity. And the 8-bit analog-to-digital converter is used to convert the analog input into digital form connected to the FPGA, and the model used is AD7822. Also, two NCE6008AS MOSFETs were used as a switch in the charging circuit and discharging circuit. For the software part, Xilinx ISE software is used and based on Hardware Description Language (HDL) called Verilog to design and program the FPGA. In this project, two 4W LEDs will be the output. Furthermore, the Pulse Width Modulation technique (PWM) will be applied in the programming to control the brightness of the LED. For the analysis part, the operating temperature will be assumed at 25 °C, and the total hours to complete a whole process will be recorded when the solar lighting system in operation. Also, only analyze the battery life cycle are based on the different

Figure 1.1 Scope of work

#### 1.5 Organisation Structure

This report focuses on designing a solar-powered lighting system using Field Gate Programmable Arrays (FPGA) and the Xilinx ISE software. The report is divided into five major sections: introduction, background study, methodology, results and discussion, followed by a conclusion and future work.

Chapter 2 discusses the literature research introduction and other related studies to this project by different researchers that contain the basics of solar panel, FPGA, and other fundamental theories. Next, Chapter 3 discusses the methodology used to achieve the project objectives and scope of work. The requirement and flowcharts needed for monitoring the project flow with the study summary will be studied.

Also, all data and results from the study are provided in chapter 4. In this chapter, all the observations and findings are discussed and observed. This chapter will present the results in a suitable diagram for the analysis of battery service life. Finally, the project and the results are concluded in Chapter 5, along with future work explanations.

اونيوسيتي تيكنيكل مليسيا ملاك UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### **CHAPTER 2**

#### **BACKGROUND STUDY**

#### 2.1 Introduction

This chapter discussed all the information about the research summary from books or journals. Also, the overview of the conventional solar-powered lighting system will be addressed in this chapter. This chapter will also briefly discuss the theory of solar panel, rechargeable lead-acid battery, buck converter, dimming method, MOSFET, and the system controller.

#### 2.2 Solar Powered Lighting Systems

The term 'solar lighting system' refers to the lighting system using solar radiation energy to charge the battery during the day with the solar panel and supply the LED light equipment with energy at night [6]. Besides that, solar lighting is an energy-efficient technology that uses semiconductor materials to obtain usable energy from

sunlight [12]. The literature on solar-powered lighting has highlighted several components: solar panels, battery, DC-DC converter, system controller, and LEDs [9]. The construction of solar lighting systems can reduce energy imports and reduce dependence on oil and natural gas, thereby reducing the risk of fuel price fluctuations and providing energy for small-scale lighting applications where electricity is the most limited and expensive [12].

#### 2.2.1 The System Operation of Solar Powered Lighting System

Several studies of the operation of the solar lighting system had been reviewed. There is the most well-known operation of the proposed system, firstly the solar panels receive solar radiation during the daytime and convert it into electrical energy through charging and discharging process, which is finally stored in battery [6][13][14]. The presence of sunlight can be sensed by the light-dependent resistor (LDR). The lights are in the OFF position if LDR detects the sunlight, and the light in the ON position when the sunlight is detected [11][15].

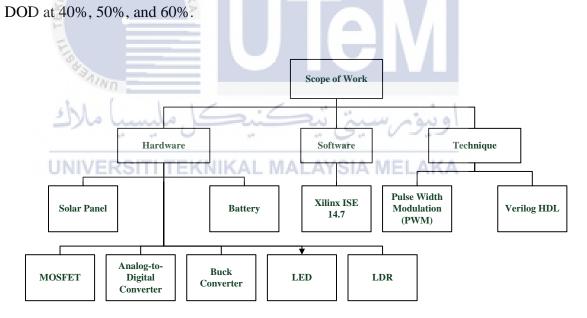

# 2.2.2 Solar Panels as an energy source ALAYSIA MELAKA

The solar or photovoltaic module is a packaged, connected photovoltaic cell known as solar cells [15]. The photovoltaic had been defined as a method of producing electrical energy using semiconductors that exhibit the photovoltaic effect to transform solar radiation into direct current [15]. According to Jordan (2015), the photovoltaic effect can be defined as the process that produces a voltage or electric current in the solar cells when they are exposed to sunlight [16]. Besides that, the photovoltaic had been described as the light enters the photovoltaic cell as pure energy. It provides enough power to release some electrons, which are negatively charged atomic particles. To generate a voltage or photovoltage, the built-in barrier in the battery acts

on these electrons that can be used to drive current through the circuit [17]. However, the photovoltaic cell comprises various semiconductor materials, mainly monocrystalline silicon and polycrystalline silicon, as shown in Figure 2.1.

A polycrystalline solar panel is made from molten silicon by casting a cube-shaped ingot [18], a faster and cheaper process. Polycrystalline solar panel are lower in price, lower efficiency, and have a shorter lifespan than the monocrystalline solar panel [19].

Figure 2.1 Polycrystalline vs Monocrystalline Solar Panels[20]

A monocrystalline solar panel composed of silicon, in which the entire solid crystal lattice is continuous, without breaking its edges, and without any grain boundaries [21]. Their advantages are high efficiency, high output power, less space, and the most extended service life. But also, it makes them more expensive than polycrystalline or thin-film solar panel [18].

Figure 2.2 The structure of monocrystalline solar panel[22]

A typical monocrystalline solar panel shown in Figure 2.2 consists of six layers [25], including frame, glass, EVA, solar cells, back film, and a junction box. Firstly, the aluminium frame functions to protect the laminate. Secondly, the tempered glass function is to protect the solar cells. The transmittance of the tempered glass typically must be high above 91%, and ultra-white tempering is required[23]. Next, the Ethylene Vinyl Acerate (EVA) film has good radiation transmittance and a low degradation rate. EVA is also a thermoplastic polymer that forms a sealing and insulating film around the solar cells by applying heat to the module. Monocrystalline silicon solar cells have the highest photoelectric conversion efficiency among various solar cells. They have 15-25 years of service life and are encapsulated in tempered glass and waterproof resin.

#### 2.2.3 Rechargeable Lead-Acid Battery as energy storage

Based on the previous journals, the rechargeable lead-acid battery had been selected to store the energy [9][12][24][25]. This is because they are low cost and have a longer service life, although the lead-acid batteries have low energy capacity, medium performance and high maintenance requirements [26]. However, there are two types of lead-acid batteries, which is deep-cycle battery and shallow-cycle battery. The shallow-cycle battery should not be used in PV systems because they are designed to discharge only about 20% of their capacity, or it will damage the battery. On the other hand, the deep-cycle battery is designed to gradually release 80% of its capacity and recharge hundreds or thousands of times depending on the battery capacity [12]. Figure 2.3 shows the construction of the lead-acid battery[27].

Figure 2.3 Construction of a Lead-acid Battery[27]

A lead-acid battery consists of the anode, cathode, electrolyte, separator, and battery casing[27]. The negative terminal is the cathode, and the positive terminal is the anode. The electrolyte connects them and drives the electrochemical reaction that generates electricity[28]. In the lead-acid battery, the positive plate is made of lead, and the negative plate is made of lead dioxide. Besides that, a separator between the positive and negative plates is made of insulating material, preventing them from contacting or short-circuiting. In addition, the electrolyte in a lead-acid battery is water with sulfuric acid.

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

There is various method to charge the lead-acid battery, the constant voltage method is the one of the most common charging method used in a lead-acid battery. This is because the charging voltage remains constant throughout the charging cycle, and the current steadily decreases as the battery charge level increases[29], as shown in Figure 2.4.

Figure 2.4 Constant voltage charging[30]

The advantage of charging at a constant voltage is that it allows charging batteries with different capacities and discharge levels. The large charging current at the beginning of charging will last for a short time and not damage the battery. Since the battery voltage is almost equal to the voltage of the power circuit, the charging current almost drops to zero at the end of charging[30].

#### 2.2.4 Buck converter circuit for stable power generated

A buck converter is a form of DC-to-DC converter that can take input directly from a DC source. The DC input can be obtained from any DC power source and obtained from AC input through a rectifier and reservoir circuit, as shown in Figure 2.5. The switching transistor between the input and output of the buck converter is continuously turned on and off at high frequencies. In order to maintain a continuous output, the circuit uses the energy stored in the inductor L to continue to provide the load during the "off" period during the "on" period of the switching transistor[31].

Figure 2.5 Buck Converter Circuit with rectifier and reservoir capacitor

As shown in Figure 2.5, the buck converter circuit consists of the switching transistor, diode D1, inductor L1, and capacitor C2. Current flows through the load through the inductor L1 while the transistor is on. The function of the inductor is to prevent the current changes and used it as energy storage. Since the inductor stores the energy taken from the increased output, the switching transistor's output does not instantly increase to its peak value. The stored energy is then released as back e.m.f into the circuit. Thus, the current flowing through the switching transistor is quickly switched off[31].

Figure 2.6 Buck Converter when switched on

When the switching transistor is turned on as shown in Figure 2.6, it will provide current to the load. The current flowing to the load is initially reduced since the energy is stored in inductor L1, so the current load and the charge on capacitor C2 gradually increase. During the entire conduction period, there will be a larger positive voltage on the cathode of diode D1 so that the diode will be reverse-biased, and it does not affect this action[31].

Figure 2.7 Buck converter when switched off

When the transistor switched off as shown in Figure 2.7, the energy stored in the inductor is released back into the circuit. During the "on" period, the back e.m.f across the inductor L1 is opposite in polarity to the voltage across the inductor L1, and there is enough stored energy in the collapsed magnetic field to keep the current flowing. Due to the back e.m.f from inductor L1, the current flows through the circuit through the load and diode D1, which is now forward biased. Furthermore, the charge stored in capacitor C2 will become the primary source of current once the inductor returns most of the stored energy to the circuit and the load voltage begins to drop, then it keeping current flowing through the load until the next "on" period begins[31].

#### 2.2.5 Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

MOSFET stands for Metal Oxide Semiconductor Field Effect Transistor and can be called an advanced from FET. In general, the MOSFET shown in Figure 2.8 is a three-terminal device with a Drain (D), Source (S), Gate (G) [32]. They should be biased to alter between cut-off and saturation state if the MOSFET is required to operate as a switch. This is because there are no current flows through the device in the cut-off region. A constant amount of current flows through the device in the saturation region, simulating the behaviour of opening and closing the switch, respectively [33]. The MOSFET function as a switch to controls the voltage and current flow between the drain and source. Refer to Figure 2.9, the MOSFET operation depends on the semiconductor surface under the oxide layer between the source and drain. The positive voltage is applied to the drain, and the negative voltage is applied to the source when a drain-source voltage  $V_{ds}$  is connected between the drain and source. Therefore, the PN junction is reversed biased at the drain, and there is forward bias at the source, and there will be no current flow between drain and source at this stage. On the other hand, suppose the positive voltage (VGG) is applied to the gate terminal. In that case, the P substrate's electrons will begin to accumulate on the gate contact that forms a conductive bridge between the two n+ regions due to electrostatic attraction.

Figure 2.8 Symbol of MOSFET[32]

The number of free electrons accumulated at the gate contact depends on the strength of the positive voltage applied. The greater the applied voltage, the greater the width of the n-channel generated by the accumulation of electrons, the greater the conductivity, and the drain current (Id) will eventually begin to flow between the source and the drain. Apart from a small amount of current due to minority charge carriers, there would be no current flow while no voltage was applied to the gate terminal. The threshold voltage is considered the minimum voltage at which the MOSFET begins conducting[34].

Figure 2.9 The MOSFET block diagram [34]

Two MOSFETs will be required to act as a switch in this project, the first MOSFET is in the charging circuit, and another is in the discharging circuit. The author uses an n-channel MOSFET to drive the LED streetlight using the PWM signals, with 49A drains current and  $17.5m\Omega$  in the driving circuit, provided with a heat sink to protect the MOSFET from being overheated [7].

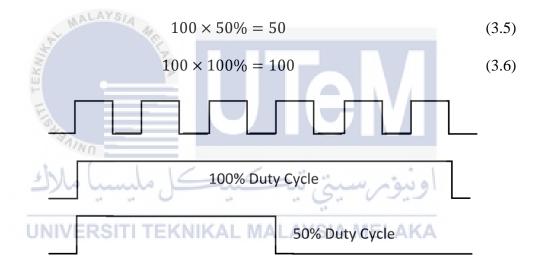

#### 2.2.6 Pulse Width Modulation as LED dimming control

Pulse Width Modulation (PWM) is used to generate the varying frequency signal and duty cycle [7], and their application includes dimming LED and controlling the motor. It can refer to a viable way to control the luminous flux of the LED, and the light emitted wavelength is affected by changing the value of the current flowing through the LED [5]. PWM is a technique for reducing the average transferable power of an applied electrical signal and controlling the average current and voltage transmitted to a load by quickly opening and closing the switch between the load and the power supply[35].

The PWM technique will be applied in this project for LED dimming use. PWM dimming takes advantage of the human eye's slow response time by rapidly turning on and off the LED at a frequency greater than 100Hz without changing the LED current flowing during the turn-on period. Since the human eye does not respond to frequencies higher than 30 Hz, the brightness seems different depending on the duty cycle of the PWM signal[36].

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

The percentage of time that the PWM signal remains high is called the duty cycle, or it can be described as the percentage of time that the digital signal is turned on in a specific time interval or period. The period is the inverse of the waveform frequency[37]. In addition, the duty cycle refers to the total time the pulse is 'on' in the entire cycle, hence at 80% brightness, the duty cycle of the LED is 80%. For example, the LED has to be turned on or off, depending on the 50% duty cycle required during the  $400\mu s$ . Therefore, a 50% duty cycle is requires the pulse to be on for  $200\mu s$  and off for  $200\mu s$ . As example, the Figure 2.10 and Figure 2.11 shows the PWM signal with 80% and 5% of duty cyle.

Figure 2.10 PWM signal when LED dimming at 80% brightness

Jasim and Kasim[5] proposed two dimming scenarios to reduce LED brightness levels according to the real-time clock time. The first scenario starts at sunset time with full brightness or 100% duty cycle, the duty cycle changed to 80% at 10 pm, and the duty cycle changed to 60% after 2 hours, and finally turned off as the sunrise time occurred. In another dimming scenario same starts at sunset time with full brightness or 100% duty cycle, the PWM signal changed to 60% at midnight.

Figure 2.11 PWM signal when LED dimming at 5% brightness

#### 2.3 System Controller for Solar Powered Lighting System

Besides the lighting system, a system controller is also an important part of all the power systems for battery charging [13]. Unchitta *et al.* stated that a discharge controller could prevent excessive discharge, which causes the shortening of the battery lifespan [24]. Several researchers have applied several controller types to control the charging and discharging process, monitor the battery levels, and control the outputs. Oke *et al.* mention that a charge controller is required for the lighting system to prevent damage to the battery and a sensor to help automatic switching [15]. The microcontroller is a computer control system on a single chip, and it has many built-in electronic circuits that can decode written instructions and convert them into electrical signals [6].

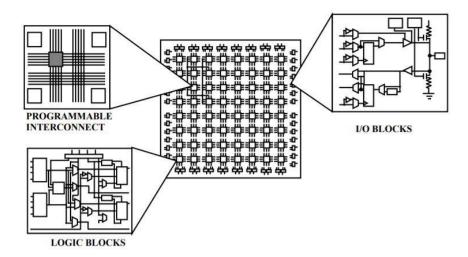

# 2.3.1 Field Programmable Gate Array

Many researchers have focused on the popular programmable hardware in recent years, which is Field Programmable Gate Array (FPGA). A Field Programmable Gate Array (FPGA) is an integrated circuit composed of internal hardware modules and user-programmable interconnects to customize operations for specific applications [38]. FPGA has high programmability and minimum design time; low power consumption, high-speed input and output, and large parallelism are important features [39]. After the FPGA is configured, the internal circuit's connection mode will create the hardware implementation of the software application. The FPGA is not like a processor, it uses dedicated hardware to process logic, and there is no operating system [40]. Figure 2.12 shows the internal structure of the FPGA, which consists of three major blocks: Configurable Logic Block (CLB), I/O Blocks, and Interconnect Wires.

Figure 2.12 The internal structure of an FPGA[40]

The configurable logic block consists of an 8-bit feature generator, two 16-bit feature generators, two flip-flop or latch registers, and a multiplexer. The CLBs are used to execute other design functions, and each of the CLBs has input on each side, allowing them to be flexible for logic mapping and partitioning. Next, the I/O block is used for external peripheral devices to access the FPGA function and using the I/O block. It can also use different peripheral devices to communicate with the FPGA to achieve various applications. Finally, the interconnect wires are used in FPGAs to connect long and short interconnect wires in a flexible combination. It also includes transistors that are used to open or close connections between various lines [41].

P. Anjali *et al.* uses the Xilinx Spartan 3 FPGA board to control the lighting system, automatically turning ON and OFF depending on sunlight and identifying movement or any object [11]. On the other hand, Jasim *et al.* simulate and implements the LED dimming on the Xilinx Spartan 3A FPGA board to control the proposed dimming scenarios [5].

#### 2.3.2 Arduino

Arduino UNO is a microcontroller board developed based on 8-bit Atmega328p [42]. The microcontroller is an essential part of all power systems used for battery charging. The reason for using Arduino UNO Atmega is its low cost, strong compatibility, compact size, and convenient interface with other types of controllers [13]. Sarkar *et al.* uses the Arduino Atmega328p microcontroller to monitor the battery level and check for replacement. The Arduino microcontroller is programmed to compare the full battery level and the present battery level to adjust the LED brightness based on the light intensity and display the brightness percentage of the LED [9]. P. Rodi *et al.* also uses the Arduino Atmega328p to control the whole circuitry lighting system. The sensor would be the microcontroller's input, the arrays of LEDs as the output, also the solar panel and battery connected to it for relay switch action [13].

#### 2.3.3 PIC Microcontroller

Recent studies have been carried out using a microcontroller PIC16F877A to control the street light system [6][7]. PIC16F877A microcontroller is easy to code and low cost, so it becomes one of the most popular microcontrollers in the industry. One of the most significant advantages of using flash technology is that it can be written and erased as much as possible [43]. Priyanka *et al.* explained that a controller also functioned to run the software to manage the system when it receives the collected information transferred from sensors [6].

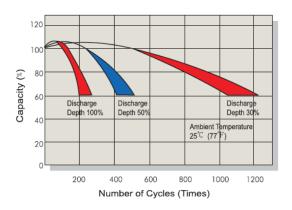

# 2.4 The Battery Lifecycle Estimation Method

The battery service life or battery lifecycle is described as a battery estimation time to support the loads before the energy is used up [44]. The battery service life is

specified in the number of cycles. However, the battery service life is most strongly depends on the interrelationship between the following parameters [45]:

- 1. The method of charging and discharging

- 2. The Depth of Discharge (DOD)

- 3. The average battery temperature

- 4. Low discharge state for a long time

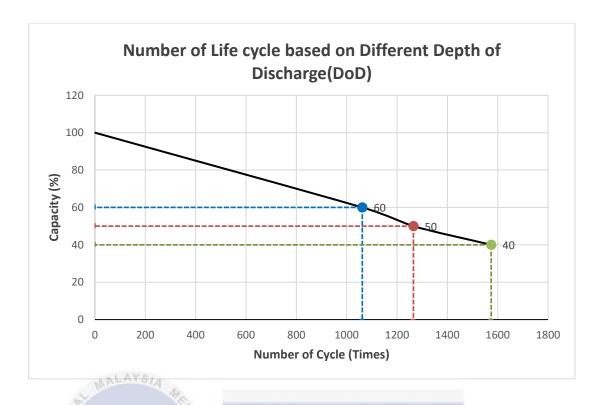

Several methods currently exist for the measurement of the battery lifecycle prediction. Layadi *et al.* proposed two types of battery lifecycle modelling: the battery ageing model depending on DOD and the modelling temperature influence on battery ageing [46]. Wibawa *et al.* introduced a battery lifecycle prediction method to predict the lead-acid battery life cycles with a simple equation (2.1), based on the obtained battery cycle in hours [44].

$$n_{cycle} = \frac{life\ expectancy\ (years)}{cycle(hours)} \times 365 \times 24 \tag{2.1}$$

According to Wibawa [44], a battery cycle comprises the discharged time and recharged time. Therefore, the datasheet provided by the manufacturer should be considered to calculate the number of battery life cycles. With reference to the datasheet of GP1272, the main parameters that need to be considered when measuring are as follows:

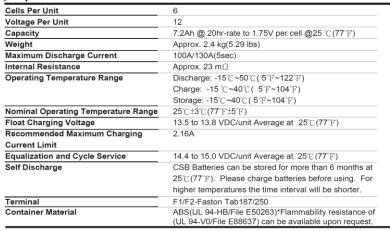

**Table 2-1 Specification of the GP1272 Battery** [47]

| Parameter            | Value      |  |  |

|----------------------|------------|--|--|

| Nominal Voltage      | 12V        |  |  |

| Nominal Capacity     | 7.2Ah      |  |  |

| Nominal Temperature  | 25 ℃ ± 3 ℃ |  |  |

| Max charge current   | 2.16A      |  |  |

| Lifecycle Expectancy | Five years |  |  |

As seen, the manufacturer's data from Table 2-1 showed that for the GP1272 battery type considered, the battery's service life was expected to be as long as five years.

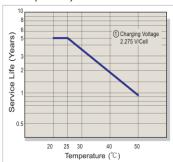

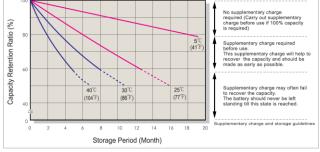

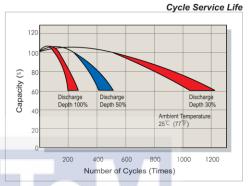

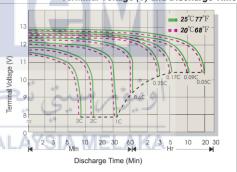

Figure 2.13 Life cycle for GP1272 battery[47]

Figure 2.13 shows the manufacturer's data provide the number of cycles depends on the different Depth of Discharge, which is 100%, 50% and 30% at the ambient temperature 25°C. However, the data from the datasheet is for the ideal situation, and it will vary by other factors in real life. Therefore, this battery lifecycle calculation method will be implemented in this solar lighting system, and the number of cycles will be obtained and analysed in this project through equation (2.1).

#### 2.5 Summary

This section discusses the advantages and disadvantages of the previous project, as listed in Table 2-2. Priyanka *et al.* (2018) used a PIC16F877A microcontroller to control the solar LED street lighting system for power saving[6]. They use the LDR sensor to indicate the light intensity and the photoelectric sensors to detect the movements. In order to develop the system, they design it by using MATLAB and MultiSim software. The system turns on and off the street light based on the two main conditions, whereas light intensity and object movement. Therefore, they save more power when the sodium vapour lamps are replaced by LED, and the LED only lights

up based on different conditions. However, this study is not focusing on the analysis of the battery service life.

Next, Shubham *et al.* (2017) use an Arduino UNO to control the solar street lighting system and design the system by using the Arduino IDE software[9]. The lighting system also uses the LDR sensor to detect the light intensity, and the LED will light up with different levels of brightness based on the changes of the light intensity detected by the LDR sensor. Besides that, they propose the intelligent battery level monitoring unit, which means the microcontroller keeps monitoring the battery level for battery replacement purposes. It also helps to avoid the battery exhausting completely. But they did not focus on the analysis of the battery service life.

Besides that, Amey *et al.* (2016) develop a smart street light system using FPGA, Xilinx ISE 9.2i tools, and ModelSim software. However, the purpose of this project is for energy-saving and reduce power consumption[10]. In the proposed system, the switch on and off of the street light depends on the light intensity detected by LDR. Besides that, they also apply the PWM technique in the dimming control of the LED. In the last project, the simulation result shows there is reducing the power consumption with the design. But the results may vary in real life due to the other component's power consumption since no hardware or prototype is developed.

For this work, a Xilinx Spartan 6 FPGA development board will be used to control the whole solar-powered lighting system and design the system by using the Xilinx ISE 14.7 software. The brightness of LED will vary depending on the LDR sensor's output, and the battery level is always monitored and displayed by the FPGA. The hardware or the prototype will be developed, and the results will be observed.

**Table 2-2 Project Summarize Table**

| <b>Project Title</b>                                             | Type of<br>Controller         | Software used   | Energy<br>Source | Advantage & Disadvantage                                                                                                                                                 | Reference                                      |

|------------------------------------------------------------------|-------------------------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Control of Solar<br>LED Street                                   | PIC16F877A<br>Microcontroller | Matlab/Simulink | Solar            | Advantage: Save more power when LED only lights on based on different situations                                                                                         | Priyanka,<br>Dr.K.Baskaran                     |

| Lighting System based on Climate Conditions and Object Movements | State M                       | ALAYSIA ARE     |                  | Disadvantage: This study did not focus on analysis on battery lifecycle                                                                                                  | (2018) [6]                                     |

| Smart Street Lighting using Green Technology                     | Arduino UNO                   | Arduino IDE     | Solar            | Advantage: Intelligent battery monitoring unit to identify battery replacement  Disadvantage: Did not study on battery lifecycle with different Depth of Discharge (DOD) | Shubham,<br>Kshitij,<br>Prajakta<br>(2017) [9] |

| Smart Street Light System using Reconfigurable FPGA Tool         | Xilinx Spartan 3              | Xilinx ISE      | Not<br>Mentioned | Advantage: Great flexibility and hardware parallelism  Disadvantage: Without a prototype                                                                                 | Asha Rani,<br>Anjali<br>(2018) [11]            |

| Solar Powered<br>Lighting System<br>via FPGA                     | Xilinx Spartan 6              | Xilinx ISE 14.7 | Solar<br>KNIKA   | Advantage: Fast-processing and great flexibility hardware                                                                                                                | This work                                      |

# **CHAPTER 3**

# **METHODOLOGY**

#### 3.1

This chapter will cover the detail of the methodology used to develop the solarpowered lighting system via FPGA. The charging and discharging algorithm, ADC conversion, seven-segment display on FPGA, LED brightness with PWM technique, prototype implementation, and the battery lifecycle estimation will be explained in this chapter.

#### 3.2 **Methodology Flowchart**

Figure 3.1 shows the methodology's flow chart, including the components identifying, design stages, simulations on the software, prototype implementation, and analysis.

**Figure 3.1 Methodology Flowchart**

Firstly, the project started with identifying the component's characteristics. Next, the charging and discharging process will be discussed, including the algorithms. Besides that, the simulation of the charging and discharging algorithm will be discussed. Then, the design and the simulation results of ADC conversion will be discussed. After this, the design and simulation results of the seven-segment display will be discussed.

Furthermore, the method and the simulation results of LED brightness levels with the PWM technique will be discussed. Also, the prototype implementation and the results will be explained. Finally, the method and results of battery life cycle analyses based on the different Depth of Discharge (DOD) will also be analyzed.

# 3.3 Components Characteristic

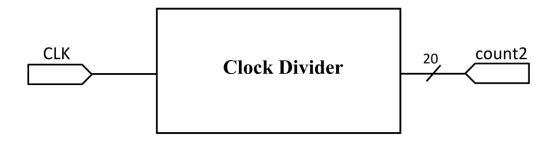

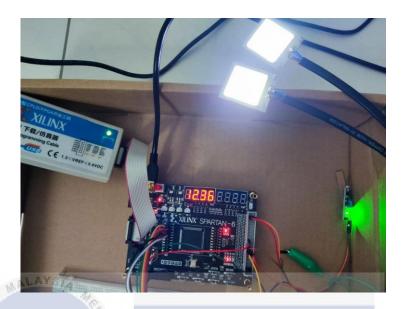

Xilinx Spartan-6 FPGA Development board, as shown in Figure 3.2, has a 50MHz crystal oscillator frequency. Therefore, by using equation (3.1) below, one clock cycle of the FPGA is 20ns.

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

one clock cycle =

$$T = \frac{1}{f} = \frac{1}{50MHz} = 20ns$$

(3.1)

Figure 3.2 Xilinx Spartan 6 FPGA Development Board

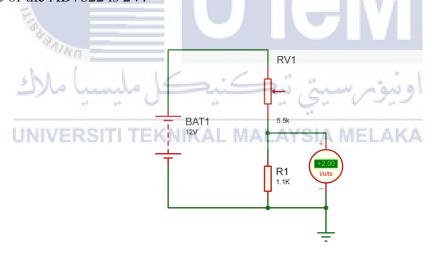

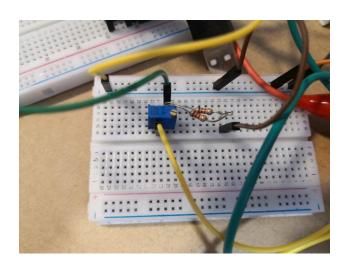

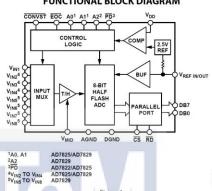

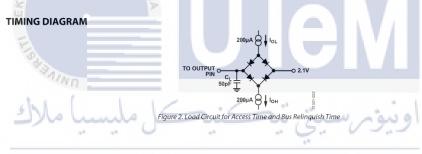

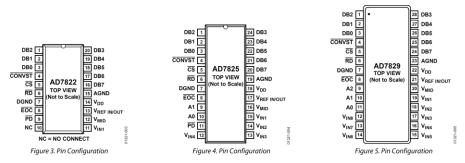

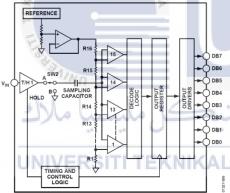

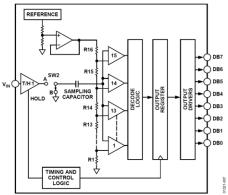

AD7822 [48], as shown in Figure 3.3, is a high-speed parallel 8-bits analog-to-digital converter with a maximum conversion time of 420ns. The input range of the AD7822 is  $3V\pm10\%$ , so a voltage divider was added between the connection of the battery and AD7822. The voltage divider consists of a variable resistor and a  $1.1k\Omega$  resistor. The voltage divider circuit becomes adjustable with a variable resistor to control the current flow through the circuit by changing the amount of resistance.

**Figure 3.3 AD7822**

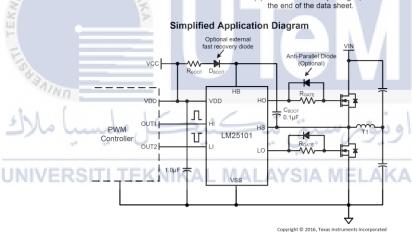

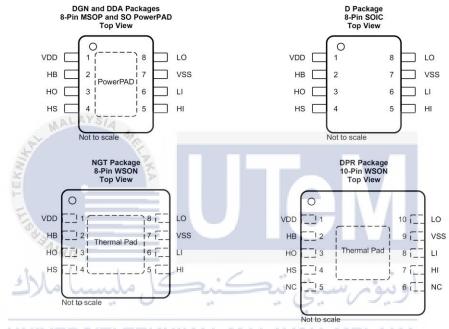

An NCE6008AS [49] MOSFET, as shown in Figure 3.4, is used as a switch to control the charging mode and the LED brightness, and the advantage of NCE6008AS is fast switching.

Figure 3.4 NCE6008AS MOSFET

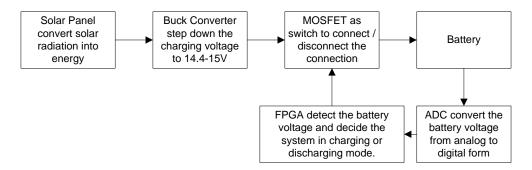

#### 3.4 Charging and Discharging Process of Solar Powered Lighting System

Figure 3.5 Charging Process of Solar Powered Lighting System

Refer to Figure 3.5, the 30W 18V solar panel will charge a 12V 7.2Ah battery through a buck converter. The buck converter will step down the voltage from the solar panel to charge the battery with a stable charging voltage of 14.7Vdc. An NCE6800AS MOSFET controlled by FPGA to connect and disconnect the charging circuit. On the other hand, the AD7822 always converts the battery level into digital form from the battery. The FPGA controls the MOSFET after detect the battery level from AD7822.

Table 3-1 State of Charge (SOC) of the 12V Lead-Acid Battery

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

| Battery Voltage | ry Voltage   Volts per cell (V)   State of Charge |       | Status   |

|-----------------|---------------------------------------------------|-------|----------|

| (V)             |                                                   | (SOC) |          |

| 12.73           | 2.12                                              | 100%  |          |

| 12.62           | 2.08                                              | 90%   |          |

| 12.50           | 2.07                                              | 80%   |          |

| 12.37           | 2.05                                              | 70%   |          |

| 12.24           | 2.03                                              | 60%   | Good     |

| 12.10           | 2.01                                              | 50%   |          |

| 11.96           | 1.98                                              | 40%   |          |

| 11.81           | 1.96                                              | 30%   | Moderate |

| 11.66           | 1.93                                              | 20%   |          |

| 11.51           | 1.89                                              | 10%   | Low      |

| 10.5            | 1.75                                              | 0%    |          |

Figure 3.6 Discharging Process of Solar Powered Lighting System

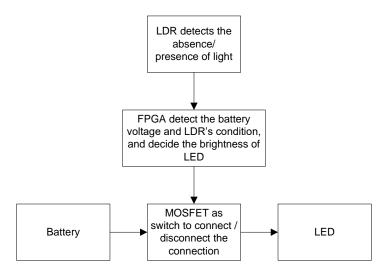

After the battery is fully charged in charging mode, the battery will stop charging, and the system will operate in the discharging mode, as shown in Figure 3.6. In the discharging process, a light-dependent resistor (LDR) module as the input sensor sends the digital signal to detect the light intensity. When the LDR detects no lights, the MOSFET will fast switching according to the duty cycle generated from FPGA. Then, the LED will light on and start to dim based on the condition of battery voltage. Else, the MOSFET will in an OFF state when the LDR detect lights. According to the discharging mode and start charging.

#### 3.4.1 Clock Divider for Charging and Discharging process

Figure 3.7 RTL of a clock divider

Since different clock frequencies drive several submodules, the clock divider is needed, as shown in Figure 3.7. The clock divider creates lower frequency clock signals from an input clock source. It counts input clock cycles and drives the output clock low and high. The clock divider counts the clock to a specific value of the submodule, and it returns to 0 and becomes a complete cycle. Five clock dividers will be used, first was the clock for hold voltage values, second used for the sequence of decimal place and the display of the seven-segment, third used for the charging, discharging and switching mode, fourth used for the duty cycle of LED brightness, and lastly is for the ADC for control the  $\overline{CONVST}$  pin for converting analog signal to digital signal.

#### 3.4.2 Charging Algorithm

Figure 3.8 RTL of the charging module

In order to avoid overcharging, a charging algorithm was developed, as shown in Figure 3.8 and Figure 3.9. The charging algorithm starts with checking whether the charging mode is equal to 1, the algorithm will go to the next stage. The switch is always toggled and checks the battery voltage when the switch is opened, and the algorithm will repeat this stage if that battery voltage detected is lower than 12.72V. Otherwise, the system will go to the discharging mode when the battery is fully charged. If the charging mode is equal to 0 initially, the system is in the discharging mode and ends the algorithm.

Figure 3.9 Charging Algorithm

#### 3.4.3 Discharging Algorithm

Figure 3.10 RTL of the discharging module

The discharging algorithm was developed to avoid over-discharging the battery, as shown in Figure 3.10 and Figure 3.11. Also, the discharging algorithm is used to determine the status of discharging after read the battery voltage. The discharging algorithm starts with checking whether the discharging mode is equal to 1, the algorithm will go to the next stage. The switch is always toggled and detects the battery voltage when the switch is opened, and the algorithm will repeat this stage if that battery voltage detected is greater than or equal to 12.24V. Otherwise, the system will go to the discharging mode when the battery is fully charged. If the charging mode is equal to 0 initially, this represents the system is in the charging mode and ends the algorithm.

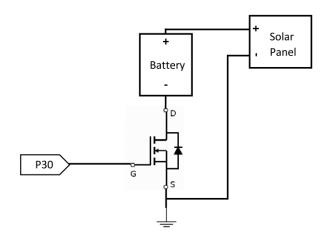

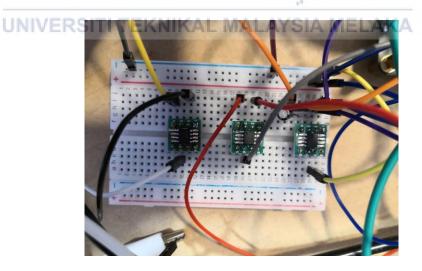

An NCE6008AS MOSFET is used as a charging switch to control the charging mode. The MOSFET gate is connected with the assigned pin 30 of FPGA, and the drain and source of MOSFET are connected between the battery and solar panel. The FPGA will send the signal to make the MOSFET in OFF state to detect the battery voltage, which is there will be no current flow during the voltage reading. This action lets the ADC read the open-circuit voltage, not the input voltage from the solar panel. The FPGA will send the signal to make the MOSFET in ON state after reading voltage, and the system decides to continue charging. Otherwise, the MOSFET will stay OFF state after the system decides to go to discharge mode.

#### 3.4.5 Analog-to-Digital Conversion

Since the FPGA development board has no in-built analog-to-digital converters, AD7822 is used as an external 8-bit ADC to convert the battery voltage from analog to digital. Besides that, AD7822 detects the voltage from the battery by connecting to the voltage divider because the input range of the AD7822 is 2V.

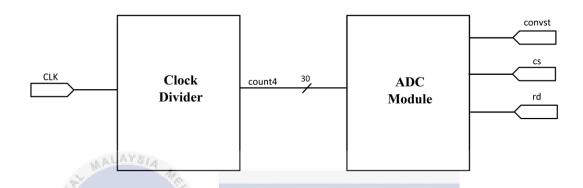

Figure 3.12 RTL of the ADC conversion module

Figure 3.12 shows the RTL circuit of the ADC module, the inputs are a clock divider module called 'clockcount', and the output is the  $\overline{\text{CONVST}}$  signal. The  $\overline{\text{CONVST}}$  signal is the logic input signal of AD7822, and the conversion start signal initiates an 8-bit analog-to-digital conversion on the falling edge of this signal. When the signal  $\overline{\text{CONVST}}$  goes to 0, ADC will start the conversion at the falling edge. After that, the signal goes to 1 before the end of conversion.  $\overline{\text{RD}}$  is a signal internally gated with the  $\overline{\text{CS}}$ , and both signals must be logic low to enable the data bus. Pin 17 of FPGA is connected to the pin  $\overline{\text{RD}}$  on ADC, and FPGA's pin 16 is connected to the pin  $\overline{\text{CS}}$ . The 8-bit converted data will send to pin 56, 57, 58, 59, 61, 62, 66, 67 of FPGA through the DB0-DB7 of ADC.

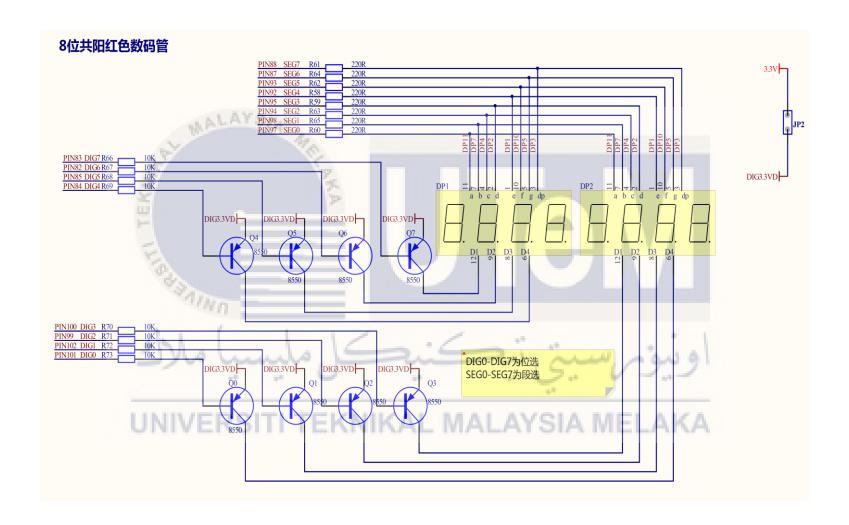

#### 3.5 Seven-Segment Display on FPGA board

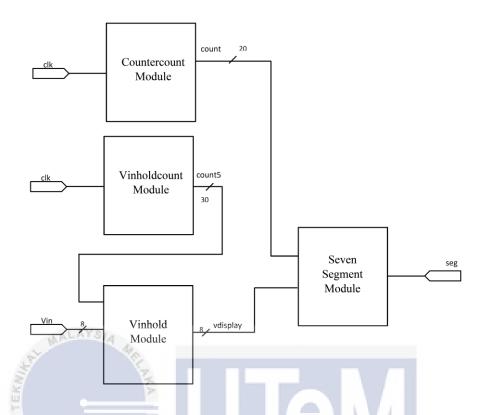

Figure 3.13 RTL of the seven-segment display module

The seven-segment on board will display the battery voltage all the time. According to Figure 3.14, seven-segment on the FPGA board's circuit structure is different from the commonly used ones. It connected these segments, so it can't assign the pin and operate separately on FPGA. Instead, the current will flow to all seven-segment onboard so that those segments will be light up simultaneously. In order to overcome this, a clock divider needed to create another clock in the design, as shown in Figure 3.13. The clock divider allows the seven-segment blinking continuously with much lower frequency but high enough, so the human eye missed out on display had flicking. The 'vinhold' module is a module to hold the input voltage value after the end of conversion at ADC and makes the 'vin' as the 'vdisplay', which will display on the seven-segment.

Figure 3.14 The circuit of seven-segment display [50]

#### 3.5.1 Clock Divider for Seven-Segment

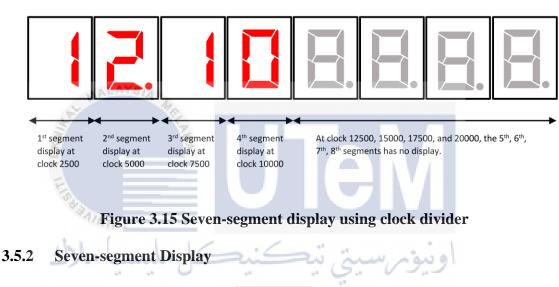

The clock divider divides the clocks at 2500, 5000, 7500, 10000, 12500, 15000, 17500, and 20000. Refer to Figure 3.15, the 1<sup>st</sup> segment will be light up according to the number assigned in the coding when the clock counted to 2500. Next, the 2<sup>nd</sup> segment will display the number assigned at the clock 5000. The 3<sup>rd</sup> segment and 4<sup>th</sup> segment will also display the number assigned at clock 7500 and 10000. However, there will be no number assigned and displayed for the following four seven-segment.

Figure 3.16 The pin diagram of the seven-segment display

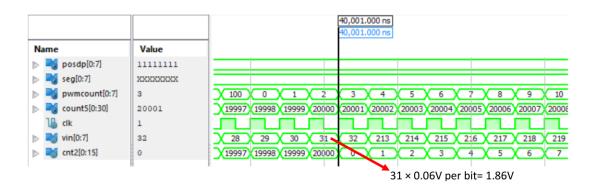

Since only four numbers will be displayed on the seven-segment, the values will be assigned only four-digit numbers. Using equation (3.2), the steps of the battery voltage level are 256, which means 256 different values of battery voltage are assigned in the module.

$$steps = 2^n = 2^8 = 256$$

(3.2)

In the seven-segment display module, 15.30V is the highest value after using equations (3.3) and (3.4).

voltage value for each step size =

$$\frac{14.70V}{256}$$

= 0.057  $\approx$  0.06V (3.3)

$$0.06V \times bit = 0.06V \times 255 = 15.30V$$

(3.4)

Refer to equations (3.3) and (3.4), the battery voltage level per bit was calculated and converted in binary and hex form for implementation in FPGA. Table 3-2 shows the sequence of the battery voltage levels from 0V to 15.30V.

Table 3-2 The battery voltage in binary and hex form

| Battery Voltage (Binary) | Battery Voltage (Hex) | Battery Voltage (V) |

|--------------------------|-----------------------|---------------------|

| 0000 0000                | 0                     | 0V                  |

| 0000 0001                |                       | 0.06V               |

| 0000 0010                | 2                     | 0.12V               |

| ل مليسياً مملاك          | بتی تیکنیک            | اونيوس              |

| :<br>U11111110           | KNIKAL MALAYSIA       | :<br>A MELA 15.24V  |

| 1111 1111                | FF                    | 15.30V              |

Refer to Figure 3.16, the pin of the display number is arranged in Table 3-3. Besides that, 256 different voltage values are programmed according to the clock distribution and the truth table of each number. Finally, the simulation result will be discussed in section 4.2.3.

Number f Decimal (dp) b d a c e g 1. 2. 3. 4. 5. 6. 7. 8. 9.

Table 3-3 The truth table of seven-segment with and without decimals

# 3.6 LED brightness levels with PWM technique AMELAKA

0.

Different brightness levels of the LED were designed with the PWM signal to extend the lighting hours. Figure 3.17 shows the LED brightness module has five inputs: 'clk', 'pwmcount', 'gotodischarge', 'vin', and 'ldr'. The 'pwmcount' module is a clock divider module that always counts the clock until 100, and it is the input of the LED brightness module.

Figure 3.17 RTL of the LED module

In order to design the LED brightness level, Equations (3.5) and (3.6) are used to calculate the total clock required to be in a high state within a count of 100.

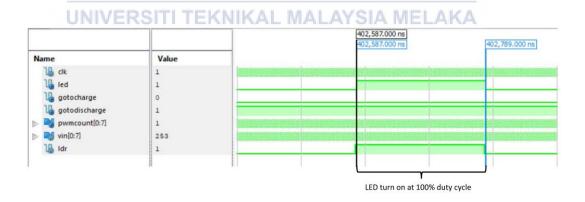

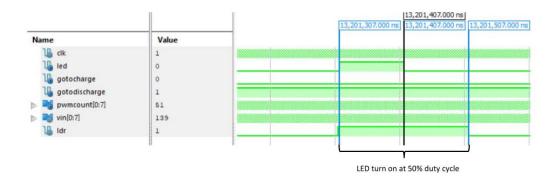

Figure 3.18 Waveform for the 100% and 50% duty cycle of LED

Refer to Table 3-4, the LED will turn on with a full duty cycle, in which the LED brightness is 100% when the LDR sensor detects no light and battery voltage is greater than or equal to 12.48V. However, when the battery voltage is lower than 12.48V, the LED will turn on half of the duty cycle, which the LED brightness is only 50% when the LDR sensor detects no light. For example, the waveform for the different brightness levels is shown in Figure 3.18.

**Table 3-4 LED Brightness**

| Battery Voltage | Brightness (%) |

|-----------------|----------------|

| >=12.48V        | 100%           |

| <12.48V         | 50%            |

### 3.7 Prototype of the Solar Powered Lighting System

The prototype consists of a 30W 18V monocrystalline solar panel, a GP1272 lead-acid battery, a buck converter, two NCE6008AS MOSFETs, a trimmer, two  $1k\Omega$  resistors, an 8-bit analog-to-digital converter AD7822, and two 4W LED. A 30W 18V monocrystalline solar panel charges the battery with a stable voltage 14.7Vdc by using a buck converter. In addition, a voltage divider, as shown in Figure 3.19, is placed between the lead-acid battery and AD7822 as the protection circuit since the input range of the AD7822 is 2V.

Figure 3.19 Voltage divider for the ADC protection

In the charging circuit, an NCE6008AS MOSFET is connected between the buck converter and the lead-acid battery. In addition, the drain and source pin of MOSFET connected between the solar panel and lead-acid battery, and the gate pin of MOSFET will be connected to pin 30 of the FPGA to control the charging mode shown in Figure 3.20.

Figure 3.20 MOSFET in charging circuit

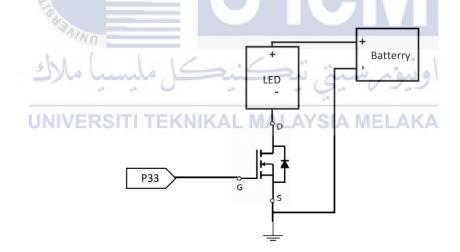

Another NCE6008AS MOSFET was used to control the PWM signal from the FPGA in the discharging circuit, as shown in Figure 3.21. The gate pin of the MOSFET will connect to pin 33 of FPGA, the drain and source pin of the MOSFET will connect to the output LED and battery.

Figure 3.21 MOSFET in discharging circuit

Implementation constraints are instructions given to FPGA implementation tools to direct the mapping, layout, timing when processing the FPGA design. However, the implementation constraints are generally placed at User Constraints File (UCF), which is defined as used to complete timing constraints, pin constraints, and area constraints.

Besides that, UCF files are ASCII code files describing logic design constraints and can be edited with a text editor and Xilinx constraint file editor. Table 3-5 shows the I/O port and its pin allocation in Xilinx Spartan 6 FPGA development board.

Table 3-5 UCF file: I/O Port and the pin allocation

| I/O    | PIN  | I/O    | PIN | I/O    | PIN | I/O    | PIN |

|--------|------|--------|-----|--------|-----|--------|-----|

| DIG[0] | P101 | SEG[0] | P97 | VIN[0] | P67 | CLK    | P22 |

| DIG[1] | P102 | SEG[1] | P98 | VIN[1] | P66 | CONVST | P81 |

| DIG[2] | P99  | SEG[2] | P94 | VIN[2] | P62 | CS     | P16 |

| DIG[3] | P100 | SEG[3] | P95 | VIN[3] | P61 | RD     | P17 |

| DIG[4] | P84  | SEG[4] | P92 | VIN[4] | P59 | EOC    | P79 |

| DIG[5] | P85  | SEG[5] | P93 | VIN[5] | P58 | LDR    | P35 |

| DIG[6] | P82  | SEG[6] | P87 | VIN[6] | P57 | LED    | P33 |

| DIG[7] | P83  | SEG[7] | P88 | VIN[7] | P56 | SWITCH | P30 |

| E.     |      |        |     |        |     | ADCLED | P29 |

# 3.8 Analysis on the number of battery lifecycle based on the Depth of Discharge (DOD)

This section will discuss the number of battery life cycles based on the Depth of Discharge (DOD). First, the total time in hours to complete one system operation cycle will be obtained, including the charging and discharging process. For analysis, the solar lighting system will operate on three days with similar weather, record the total time in hours from the battery charging to fully charged, and discharge it until the Depth of Discharge is 40%. In order to compare the number of battery life cycle on the different Depth of Discharge (DOD), the system will repeat the whole process a total of three times: first, the battery will be discharged until the Depth of Discharge 40%, second times the battery will discharge until the Depth of Discharge 50%, and the third times the battery will start to discharge until the Depth of Discharge 60%.

#### 3.9 Summary

First of all, the method of charging and discharging process had been discussed in this chapter. The clock divider was developed to produce a slower output frequency by dividing the input clock in the charging process. In order to avoid over-charging and over-discharging of the battery, the charging and discharging algorithm were developed. Also, a switching algorithm was developed to control the charging switch for open-circuit voltage detection and charging circuit connection. Next,  $\overline{CONVST}$  signal was generated to let the conversion start signal starts the 8-bit analog-to-digital conversion on the falling edge of the signal.

In addition, the seven-segment display on FPGA also had been discussed. Two clock dividers were developed to hold the display voltage value, and another is used to create a slower frequency for the seven-segment display. Besides that, the different brightness levels of the LED are also discussed. The LED stays in the HIGH state through the PWM signal within a full duty cycle or half of the duty cycle during darkness and meets the specific battery level. Lastly, the hardware circuit of the prototype and the analysis method also had been discussed. The simulation and prototype results will be discussed and analyzed in the next chapter.

# **CHAPTER 4**

# **RESULTS AND DISCUSSION**

#### 4.1 Introduction

This chapter includes all the simulation and hardware implementation results achieved by completing all the methodologies in the previous chapter. Besides that, the result will be described in each part of this chapter. Furthermore, the result of the number of battery life cycles also will be analyzed in this chapter.

# 4.2 Simulation results of Solar Powered Lighting System

This section is discussing the simulation results of the solar-powered lighting system. In order to verify the methods, simulation of the systems was run by the software Xilinx ISE 14.7.

#### 4.2.1 Simulation results of charging and discharging algorithm

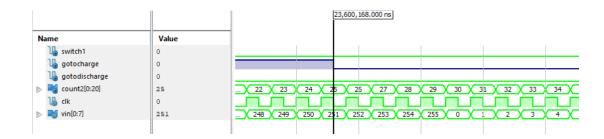

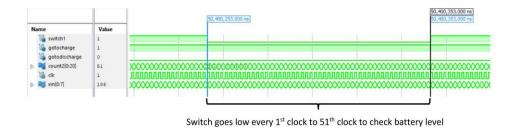

This section is discussing the simulation results of the charging and discharging algorithm. A 2.5kHz clock counter was generated to count 20000 clocks and return to 0, which uses a total  $400\mu s$  per cycle. The charging mode module will determine the

status of the charging mode at clock 25 by detects the battery voltage and the state of the charging flag, which is named 'gotocharge'. It represents a flag to determine the system will be in charging mode or discharging mode. Figure 4.1 shows that the 'gotocharge' signal goes to 0 when the battery is fully charged at clock 25, which means the system stops the charging process.

Figure 4.1 Simulation result of charging mode when the FPGA detects the battery is fully charged

Figure 4.2 shows the 'gotocharge' signal goes to 1 when the input voltage detected is lower than 12.24V at clock 25, which means the system starts the charging process.

Figure 4.2 Simulation result of charging mode when the system detects the low voltage of the battery

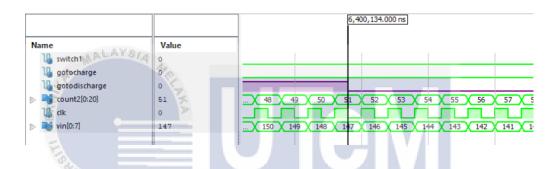

The system will determine the status of the discharging mode at clock 51 by detects the battery voltage and the state of the discharging flag, which is named 'gotodischarge'. Figure 4.3 shows that the 'gotodischarge' signal at clock 51 goes to 0 when the input voltage is lower than 12.24V, which means the system stops the discharging process.

Figure 4.3 Simulation result of discharging mode when the system detects the battery is fully charged

However, Figure 4.4 shows the 'gotodischarge' signal goes to 1 when the battery is fully charged at clock 51, which means the system starts the discharging process.

Figure 4.4 Simulation result of discharging mode when the system detects the low battery voltage

The switching mode module functions to control the charging switch, which is the **LINIVERSITI TEKNIKAL MALAYSIA MELAKA**NCE6008AS MOSFET. Figure 4.5 shows the switch goes 0 which starts from clock one during every cycle, and it is designed to let the system detects the open-circuit input voltage between this gap, and the system will decide the charging switch opened or closed at clock 51, according to the charging signal.

Figure 4.5 Simulation of switching mode

#### 4.2.2 Simulation results of analog-to-digital conversion

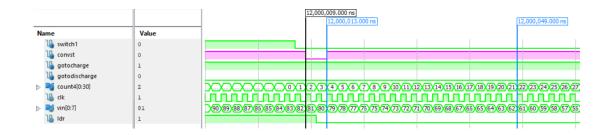

The state of ADC conversion is discussed in this section. Figure 4.6 shows the falling edge of the  $\overline{\text{CONVST}}$  initiates a conversion at clock 1 to start the conversion and the  $\overline{\text{CONVST}}$  signal goes high at clock 3, which before the end of a conversion.

Figure 4.6 Simulation of CONVST signal in conversion process

#### 4.2.3 Simulation results of seven-segment display

This section is discussing the simulation results of the seven-segment display. Figure 4.7 shows that the input voltage value of the clock 20000 is 31, or 1.86V that obtained by using equation (4.1). The voltage value is displayed in four-digit numbers, which is 01.86V.

the voltage value of

$$31 = (31 \times 0.06V) = 1.86V$$

(4.1)

Figure 4.7 The input voltage detected by FPGA

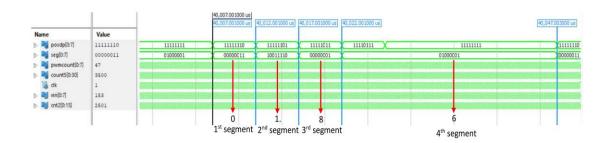

As stated in Table 3-3, Figure 4.8 shows that the number displayed on the first seven-segment is '0'. The number displayed on the next seven-segment is '1.' After this, the number displayed is '8' at the third seven-segment, and the number displayed is '6' at the fourth seven-segment.

Figure 4.8 The value displayed on the seven-segment

#### **4.2.4** Simulation results of LED brightness levels

In this simulation, the brightness of the LED will be varied by the battery voltage. Figure 4.9 shows the waveform of the LED when it 100% brightness. By using equation (4.1), the input voltage detected is greater than 12.24V. As a result, the LED turns on at 100% duty cycle during LDR in state HIGH with this voltage level.

Figure 4.9 Simulation result of 100% brightness of the LED