# CURRENT RATIO ANALYSIS ON DESIGN AND MODELLING A 22 NM BILAYER GRAPHENE AND HIGH-K/METAL GATE (TiO<sub>2</sub>/WSi<sub>x</sub>) NMOS DEVICE

#### NUR ATHIRAH SYUHADA BINTI KAMALRUL ARIFFIN

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## CURRENT RATIO ANALYSIS ON DESIGN AND MODELLING A 22 NM BILAYER GRAPHENE AND HIGH-K / METAL GATE (TiO<sub>2</sub> / WSi<sub>x</sub>) NMOS DEVICE WHICH HAS BEEN APPROVED BY FACULTY OF ELECTRONIC AND COMPUTER ENGINEERING

#### NUR ATHIRAH SYUHADA BINTI KAMALRUL ARIFFIN

This report is submitted in partial fulfilment of the requirements for the degree of Bachelor of Electronic Engineering with Honours

Faculty of Electronic and Computer Engineering UNIVERS Universiti Teknikal Malaysia Melaka

**JULY 2020**

## **DECLARATION**

I declare that this report entitled "Current Ratio Analysis on Design and Modelling a 22 nm Bilayer Graphene and High-k/Metal Gate (TiO2/WSix) NMOS Device" is the result of my own work except for quotes as cited in the references.

Signature :

Author : NUR ATHIRAH SYUHADA BINTI KAMALRUL ARIFFIN

Date : 2 JULY 2020

## **APPROVAL**

I hereby declare that I have read this thesis and in my opinion this thesis is sufficient in terms of scope and quality for the award of Bachelor of Electronic Engineering

Supervisor Name

2/7/2020

Date

## **DEDICATION**

In this section is especially dedicated to express my highest gratitude to my beloved parents and siblings for endless love and support. To my lecturers and fellow friends,

thank you for the guidance and help that were shared and discuss together till

finished this report.

اونیونرسیتی تیکنیکل ملیسیا ملاك

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### **ABSTRACT**

A 22nm of a bilayer Graphene NMOS transistor was designed and modeling based on virtual fabrication using Silvaco Software besides optimized current ratio using Taguchi L9 orthogonal array method. In this project, the materials used are high permittivity material (high-K) which is Titanium Dioxide (TiO<sub>2</sub>) and metal gate which is Tungsten Silicide (WSi<sub>x</sub>). There are four Control Factor (CF) and two Noise Factor (NF) which have been considered to get a good result for threshold voltage and leakage current. As the result of  $V_{TH}$  optimization, Halo Tilt angle is the adjustment factor while Compensation Implant was selected as dominant factor. Meanwhile, the dominant factor for  $I_{LEAK}$  optimization is Compensation Implant. From L9 Taguchi, the  $V_{TH}$  value of 0.289433V and  $I_{LEAK}$  value of 5.61104 nA/ $\mu$ m were achieved which closer to the ITRS 2012 prediction which is 0.289 V  $\pm$  12.7% for threshold voltage and lower than 100nA/ $\mu$ m for leakage current. Finally, the value of current ratio obtained is  $4.4822 \times 10^4$ .

#### **ABSTRAK**

22nm transistor graphene NMOS dibentuk dan dimodelkan berdasarkan fabrikasi maya menggunakan Perisian Silvaco selain nisbah arus yang dioptimumkan menggunakan kaedah Taguchi L9 ortogonal array. Dalam projek ini, bahan yang digunakan adalah bahan permitiviti tinggi (high-K) yang merupakan Titanium Dioksida (TiO2) dan gerbang logam yang merupakan Tungsten Silicide (WSix). Terdapat empat Faktor Kawalan (CF) dan dua Faktor Kebisingan (NF) yang berbeza-beza dalam menentukan nilai terbaik untuk voltan ambang dan arus kebocoran. Hasil pengoptimuman  $V_{TH}$ , sudut Halo Tilt adalah faktor penyesuaian manakala Implan Kompensasi dipilih sebagai faktor dominan. Sementara itu, faktor utama pengoptimuman  $I_{LEAK}$  adalah Implan Kompensasi. Pengoptimuman Taguchi juga mencapai nilai min  $V_{TH}$  0.289433V dan nilai min  $I_{LEAK}$  minimum 5.61104 nA/ $\mu$ m yang lebih dekat dengan nilai ramalan yang diberikan dalam ITRS 2012 iaitu 0.289 V  $\pm$  12.7% untuk voltan ambang dan lebih rendah daripada 100nA/ $\mu$ m untuk arus kebocoran. Akhir sekali, nilai nisbah arus yang diperoleh adalah 4.4822 x 104.

#### **ACKNOWLEDGEMENTS**

Foremost, I wish my sincere gratitude to my supervisor, Dr. Afifah Maheran binti Abdul Hamid for the continuous support of my FYP project and helped in writing of this thesis. I would like to express my appreciation to the master student, Amer who helped me to install and introduce this software to me.

Sincere thanks to all friends especially Azizul Haqeem bin Abd Gani, Nur Dini binti Razz Rozzfaisal and others for their moral support and encouragement UNIVERSITI TEKNIKAL MALAYSIA MELAKA during preparing my project and thesis.

Last but not least, my sincere gratitude goes to my beloved parents; Kamalrul Ariffin bin Mohd. Yusof and Noriah binti Hussain and also to my siblings for their support throughout my life.

#### **Table of Contents**

| Declaration                                | i    |

|--------------------------------------------|------|

| Approval                                   | i    |

| Dedication                                 | i    |

| Abstract                                   | i    |

| Abstrak                                    | ii   |

| Acknowledgements                           | iii  |

| List of Figures                            | viii |

| List of Tables                             | X    |

| List of Symbols and Abbreviations          | xi   |

| List of Appendices                         | xiii |

| CHAPTER I INTRODUCTION                     | 1    |

| 1.1 UNIVERSITI TEKNIKAL MALAYSIA MELAKA    | 1    |

| 1.2 Problem Statement                      | 3    |

| 1.3 Objectives                             | 4    |

| 1.4 Scope of Work                          | 4    |

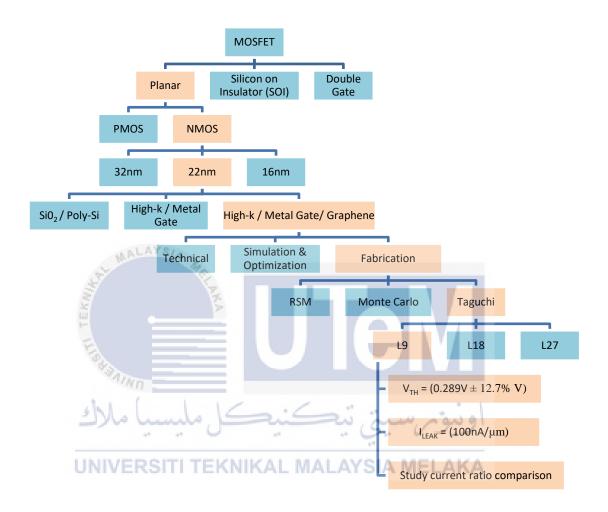

| Figure 1.1: Flowchart of the Scope of Work | 5    |

| 1.5 Report Structure                       | 6    |

| CHAPTER 2 BACKGROUND STUDY                 | 7    |

| 2.1 MOSFET Fundamental                     | 7    |

|                                                                         | V  |

|-------------------------------------------------------------------------|----|

| Figure 2.1: The diagram and symbol of MOSFET                            | 8  |

| 2.1.1 MOSFET Operation                                                  | 9  |

| 2.1.2 N-Channel MOSFET                                                  | 9  |

| 2.2 Scaling MOSFET                                                      | 9  |

| 2.2.1 Moore's Law                                                       | 10 |

| Figure 2.2: Graph of CPU transistor counts from 1971-2008 & Moore's Law | 11 |

| 2.2.2 High Permittivity (High-K) Dielectric                             | 12 |

| Figure 2.3: The graph of the ideal High-K materials.                    | 12 |

| 2.2.3 Metal Gate                                                        | 13 |

| Figure 2.4: The structure of Metal Gate in MOSFET                       | 13 |

| 2.3 Graphene                                                            | 14 |

| Figure 2.5: The structure of Graphene                                   | 14 |

| 2.3.1 V Graphene Bandgap KAL MALAYSIA MELAKA                            | 15 |

| Figure 2.6: The diagram of bandgap in Graphene.                         | 15 |

| 2.4 Summary from Previous Research                                      | 16 |

| Table 2.1: Summary from Previous Research                               | 16 |

| CHAPTER 3 METHODOLOGY                                                   | 20 |

| 3.1 Flowchart of the project                                            | 20 |

| Figure 3.1: Flowchart of the project                                    | 21 |

| 3.2 Experimental Setup                                                  | 22 |

|                                                                                  | vi |

|----------------------------------------------------------------------------------|----|

| Table 3.1 Fabrication step of NMOS device                                        | 23 |

| 3.2.1 Virtual Fabrication of 22nm Bilayer Graphene NMOS                          | 25 |

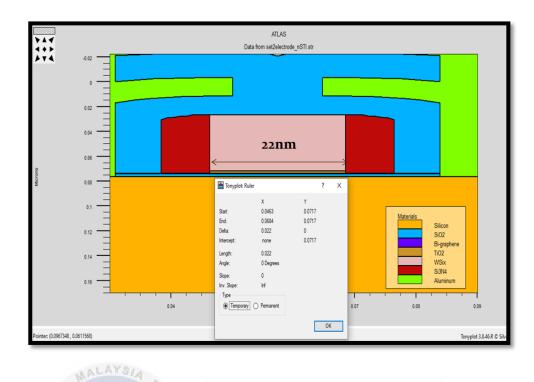

| Figure 3.2: The complete 22nm NMOS device structure                              | 26 |

| Figure 3.3: The enlarged figure of the 22 nm gate length                         | 27 |

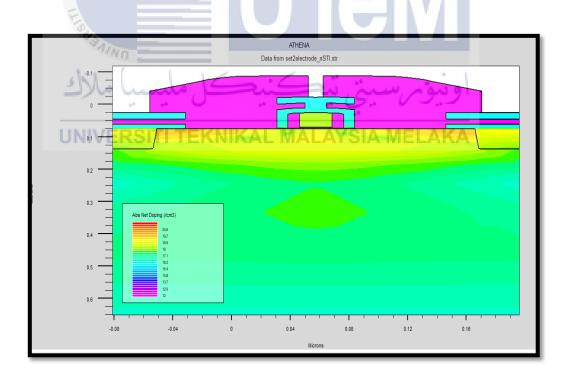

| Figure 3.4: Doping profile of 22nm NMOS transistor                               | 27 |

| 3.2.2 Semi Analytical Approach for Bilayer Graphene                              | 28 |

| 3.3 Taguchi Method to Parameter Design                                           | 29 |

| Table 3.2: Process parameters and their levels                                   | 29 |

| Table 3.3: Noise factors and their levels                                        | 30 |

| Table 3.4: Orthogonal Array L9 Taguchi                                           | 30 |

| CHAPTER 4 RESULTS AND DISCUSSION                                                 | 31 |

| 4.1 Virtual Fabrication for 22nm NMOS Device                                     | 31 |

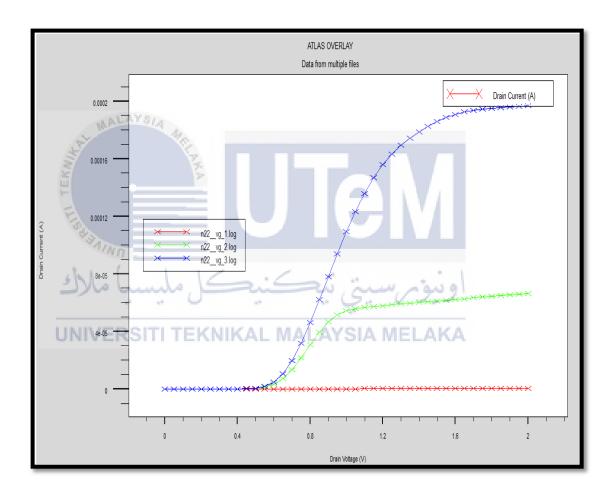

| Figure 4.1: Graph of $I_D$ - $V_D$ for 22nm NMOS device SIA MELAKA               | 32 |

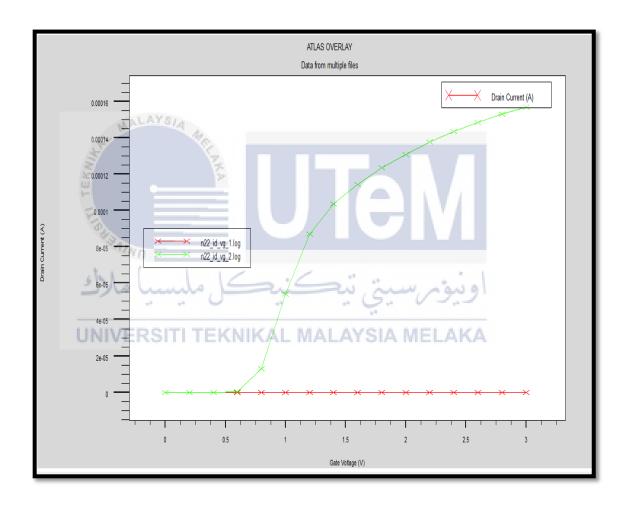

| Figure 4.2: Graph of I <sub>D</sub> -V <sub>G</sub> for 22nm NMOS device         | 33 |

| 4.2 Optimization analysis of L9 Taguchi Array method                             | 34 |

| Table 4.1: The completed response for $V_{\text{TH}}$ and $I_{\text{LEAK}}$ data | 34 |

| Table 4.2: S/N Ratio for Nominal-the-Best                                        | 36 |

| Table 4.3: S/N Response for V <sub>TH</sub>                                      | 37 |

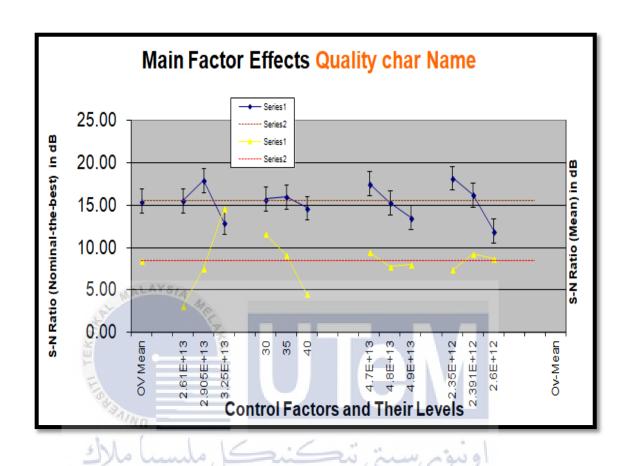

| Figure 4.3: Factor effect graph for the S/N Ratio for $V_{TH}$                   | 38 |

| Table 4.4: S/N Ratio for Smaller-the-Better                                      | 39 |

|                                                                            | vii      |

|----------------------------------------------------------------------------|----------|

| Table 4.5: S/N Response for I <sub>LEAK</sub>                              | 40       |

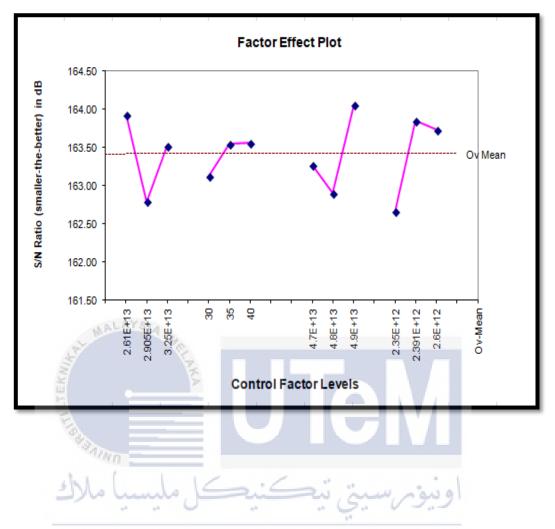

| Figure 4.4: Factor effect graph for the S/N Ratio for $I_{LEAK}$           | 41       |

| 4.3 Analysis of Variance (ANOVA) for V <sub>TH</sub> and I <sub>LEAK</sub> | 42       |

| Table 4.6: Results of ANOVA for V <sub>TH</sub>                            | 42       |

| Table 4.7: Results of ANOVA for I <sub>LEAK</sub>                          | 43       |

| 4.4 Confirmation of Optimum Run                                            | 44       |

| Table 4.8: Best Setting Parameter for $V_{TH}$ and $I_{LEAK}$              | 45       |

| Table 4.9: Results of Confirmation Experiment                              | 45       |

| Table 5.0: ITRS Prediction vs. Optimization Results                        | 46       |

| CHAPTER 5 CONCLUSION AND FUTURE WORKS REFERENCES                           | 47<br>49 |

| اونيوسيتي تيكنيكل مليسيا ملاك                                              |          |

| UNIVERSITI TEKNIKAL MALAYSIA MELAKA                                        |          |

## LIST OF FIGURES

| No.        | Topic                                                        |    |

|------------|--------------------------------------------------------------|----|

| Figure 1.1 | Flowchart of the scope of work                               | 5  |

| Figure 2.1 | The diagram and symbol of MOSFET's                           | 8  |

| Figure 2.2 | Graph of CPU transistor counts from 1971-2008 & Moore's  Law | 11 |

| Figure 2.3 | The graph of the ideal High-K materials                      | 12 |

| Figure 2.4 | The structure of Metal Gate in MOSFET                        | 13 |

| Figure 2.5 | The structure of Graphene                                    | 14 |

| Figure 2.6 | The diagram of bandgap in Graphene                           | 15 |

| Figure 3.1 | Flowchart of the project                                     | 21 |

| Figure 3.2 | The complete 22nm NMOS device structure                      | 26 |

| Figure 3.3 | The enlarged figure of the 22 nm gate length                 | 27 |

| Figure 3.4 | Doping profile of 22nm NMOS transistor                       |    |

| Figure 4.1 | Graph of I <sub>D</sub> -V <sub>D</sub> for 22nm NMOS device | 32 |

| Figure 4.2 | Graph of I <sub>D</sub> -V <sub>G</sub> for 22nm NMOS device | 33 |

| Figure 4.3 | Factor effect graph for the S/N Ratio for V <sub>TH</sub>               | 38 |

|------------|-------------------------------------------------------------------------|----|

| Figure 4.4 | Factor effect graph for the S/N Ratio for $I_{\mbox{\scriptsize LEAK}}$ | 41 |

## LIST OF TABLES

| No.                                                       | Topic                                                   |    |  |

|-----------------------------------------------------------|---------------------------------------------------------|----|--|

| Table 2.1                                                 | Summary from previous Research                          | 16 |  |

| Table 3.1                                                 | Fabrication step of NMOS device                         | 23 |  |

| Table 3.2                                                 | Process parameters and their levels                     | 29 |  |

| Table 3.3                                                 | Noise factors and their levels                          | 30 |  |

| Table 3.4                                                 | Orthogonal Array L9 Taguchi                             | 30 |  |

| Table 4.1                                                 | The completed response for $V_{TH}$ and $I_{LEAK}$ data | 34 |  |

| Table 4.2 VERSITI S/N Ratio for Nominal-the-Best MELAK/36 |                                                         |    |  |

| Table 4.3                                                 | $S/N$ Response for $V_{TH}$                             | 37 |  |

| Table 4.4                                                 | S/N Ratio for Smaller-the-Better 39                     |    |  |

| Table 4.5                                                 | S/N Response for $I_{LEAK}$ 40                          |    |  |

| Table 4.6                                                 | Results of ANOVA for $V_{TH}$ 42                        |    |  |

| Table 4.7                                                 | Results of ANOVA for I <sub>LEAK</sub> 43               |    |  |

| Table 4.8                                                 | Best Setting Parameter for $V_{TH}$ and $I_{LEAK}$ 45   |    |  |

| Table 4.9                                                 | Results of Confirmation Experiment 4.                   |    |  |

| Table 5.0                                                 | ITRS Prediction vs. Optimization Results                | 46 |  |

#### LIST OF SYMBOLS AND ABBREVIATIONS

SCE : Short Channel Effect

MOSFET: Metal Oxide Semiconductor Field Effect Transistor

ITRS : International Technology Roadmap for Semiconductor

Poly-Si : Poly-Silicon

SiO<sub>2</sub> : Silicon Dioxide

$TiO_2$  : Titanium Dioxide

WSi<sub>x</sub> : Tungsten Silicide

HfO<sub>2</sub> : Hafnium Dioxide

FET : Field-Effect Transistor

High-K : High Permittivity

EOT : Equivalent Oxide Thickness

$V_{TH}$ : Threshold Voltage

$V_{GS}$ : Gate Voltage

V<sub>DS</sub> : Drain-Source Voltage

TSMC : Taiwan Semiconductor Manufacturing Company

UHD : Ultra High Definition

LPP : Low Power Plus

PPA : Power Performance Area

STI : Shallow Trench Insulator

LPCVD : Low Pressure Chemical Vapour Deposition

BPSG : Borophosphosilicate Glass

STB : Smaller-the-Better

NTB : Nominal-the-Best

ANOVA : Analysis of Variance

ITRS : International Technology Roadmap for Semiconductors

## LIST OF APPENDICES

## **CHAPTER 1**

## **INTRODUCTION**

The activity of scaling down of gate length had been increases by years to create devices much thin so as to fabricate high density chips. As MOSFET is downscaled it gives more difficulties and worsens when it comes to the nanometer dimensions for example, SCE [11].

Sustaining Moore's Law while satisfying the needs for low power high performance in electronic systems have prompted an innovation of a device structures and implementation the materials. This creation has been exhorted by the ITRS for the efficient scaling of the devices in the following 15 years. As far as a planar geometry, MOSFET device has transformed from a traditional SiO<sub>2</sub> / Polysilicon (Poly-Si) MOSFET to a high-K / metal gate. Due to its excellent properties, single layer and bilayer graphene have been applied as the channel material for transistor device. Next, bilayer graphene was implemented along by pairing High-K / metal gate and replaced with SiO<sub>2</sub> / Poly-Si as the top gate so that it will create the band gap, regulates the current in drain region, I<sub>D</sub> and will restrict the carrier mobility into the channel. Thus, the 22nm bilayer graphene will be virtual fabricates in Silvaco Software to analyze the performance and next, will be optimized using the Taguchi method analysis [13]. For this project, the virtual fabrication was simulated and electrical characteristics in Silvaco Software for designing and optimization of the semiconductor device parameter. The L9 Taguchi Array was utilized as a part of the optimization process to evaluate variance and mean effect. [20]. TiO<sub>2</sub> and WSi<sub>x</sub> were selected as high-K and metal gate in this project. The electrical characteristics of this NMOS device prediction made by the ITRS 2012 was used as a useful approach for next research in exploring and enhances the efficiency of the devices.

#### 1.2 Problem Statement

From theory Moore's law, many researchers applied this law as the guidance in semiconductor technology to enhance the performance of the materials. However, this trend will make the manufacturing cost per device increases. Thereby, the production will must to downscale the geometry of the MOSFET [26].

Scaling down of the device will reduce the gate length, resulting in a closer gap between the drain and the source thus SCE occur [10]. When SCE happened, the devices will have some problems to produce and fabricate. For many years, SiO<sub>2</sub> layer was chosen as the high-K in devices but more disadvantages than the benefits. The silicon dioxide layer will crack and make current leakage rise up. Thus, excessive dissipation of power in the device and make the production cost become higher. When the high-K was introduced together with Poly-Si, they cannot be unite as the both materials give a reaction and this shows that the metal gate and high-K must be in sync.

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

Thus, the solution of the previous researcher for these issues of gate leakage current are being resolved by applying a new method which is combining a high-K dielectrics and metal gate for replacing the traditional SiO<sub>2</sub> and Poly-Si.

#### 1.3 Objectives

There are two objectives in this project. The objectives are:

- i. To design a 22 nm NMOS device with Graphene, Titanium Dioxide  $(TiO_2)$  and Tungsten Silicide  $(WSi_x)$  using Silvaco TCAD Software.

- ii. To analyze electrical characteristics and optimize current ratio using TaguchiL9 orthogonal array method.

## 1.4 Scope of Work

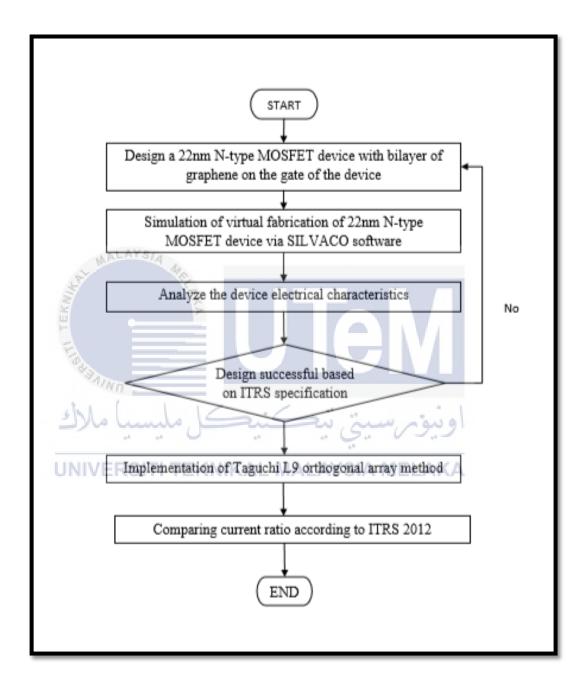

Figure 1.1 indicates the flowchart of this scope of the project. The existing device structures are the high-k is Titanium Dioxide (TiO<sub>2</sub>) and Tungsten Silicide (WSi<sub>x</sub>) which is a metal gate. The Silvaco software will be apply to virtually fabricate the UNIVERSITITE KNIKAL MALAYSIA MELAKA device. The ATHENA in Silvaco software will be used to simulate the virtual fabrication of the N-type device while for the ATLAS is for the electrical characteristic's properties. Next, the L9 Taguchi array was used to analyze the electrical characteristics from the current ratio and to optimize the best combination to produce a device with better performance. This method also to analyze the V<sub>TH</sub>, I<sub>ON</sub>, I<sub>OFF</sub> and current ratio refer ITRS 2012 and compare with previous researcher.

Figure 1.1: Flowchart of the Scope of Work

#### 1.5 Report Structure

This report aims on a current ratio analysis on 22 nm NMOS device with graphene / high-K and metal gate using Silvaco Software. This report is classified into five major chapters which are introduction, background study, methodology, results and discussion, and also conclusion and future works. For Chapter 1 will review about the background of the project, problem statement, objectives of the project, scope of work and the report structure. Chapter 2 discuss on the literature review which contain the introduction, and other studies that relates to this project from different researcher which are MOSFET fundamental, Moore's Law, High-K / Metal Gate, graphene properties and summary from previous study. Next, Chapter 3 reviews about the methodology used in this project. The introduction, flowchart of the project and experimental setup will be analyzed. Chapter 4 reviews about the results obtained and discussions of the device. In this chapter, fabrication using Silvaco software, virtual transistor in Silvaco ATHENA, transistor electrical characteristic in Silvaco ATLAS and Taguchi Orthogonal L9 Array method are reviewed. Chapter 5 reviews about the conclusion which can conclude the whole project from the results to the future works.

#### **CHAPTER 2**

#### **BACKGROUND STUDY**

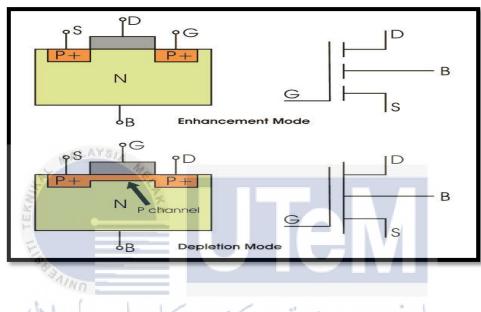

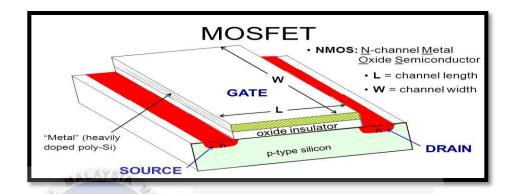

Lilienfeld and Heil was the first researchers in conceived the insulated gate field effect transistor (FET) in 1926 [15]. These insulated-gate FET have been used widely in semiconductor industry and now named as MOSFET. The MOSFET is a semiconductor device which the function are for switching and amplifying electronic signals thus beneficial for the device functionality. Due to its size which is smaller, it is suitable to design and fabricates in this semiconductor devices such as switch [16].

MOSFET can be divided into two which are Depletion Type and Enhancement Type. For Depletion type, the drain current,  $I_D$  can flow at zero gate bias while for Enhancement type, zero  $I_D$  can flow at zero gate bias and has no conducting channel region. In that both types, there are four terminal devices in MOSFET which are Source, Gate, Drain and Body terminals [10].

Figure 2.1: The diagram and symbol of MOSFET

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### 2.1.1 MOSFET Operation

MOSFET works as a capacitor. Firstly, the gate length whether used positive or negative voltages are applied thus it can be set up into N-type in depletion region . When the holes present with a repulsive force which populated by negative charges and associated with acceptor atoms is known as positive gate voltage. While, the negative voltage is applied when the holes present and filled by positive charges and allied with donor atom [16]. Thus the current can freely flow and the gate voltage  $V_G$ , will control the electrons in the channel.

This type of MOSFET is located between source and drain which is heavily doped N+ region which the highest number of electrons as current carriers [16]. The UNIVERSITY TEKNIKAL MALAYSIA MELAKA negatively charged electrons will caused the current to flow in this type of MOSFET.

#### 2.2 Scaling MOSFET

MOSFET scaling is the reduction in parameters with technological advancement. The semiconductor industry has benefited enormously from the MOSFET miniaturization over the last decades. Reducing transistors to dimensions below 100 nm will allow a lot of transistors to be implemented on a high density chip. The benefits of downscaling of the devices such as increased

functionality, reduces power dissipation and reduces cost of manufacturing a wide range of integrated circuits and systems to the users and especially for semiconductor technology in creating a smaller devices with a greater performances [14]. When the MOSFET transistors in size are reduced, the chip area will lessen. So that, more single chips per wafer can be designed and produced. Besides, the downsides of scaling the devices are causes noise problem. This is because when there are problem in noise when the scaling process takes step thus the efficacy of the devices will low [17].

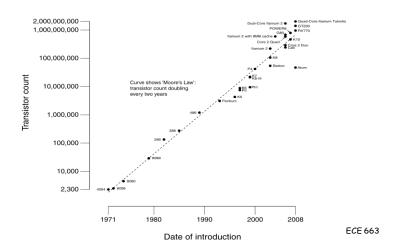

#### 2.2.1 Moore's Law

In 1965, Gordon Moore has an insight in the semiconductor industry which is a revelation which revolutionized the technology industry and devote in semiconductor technology. With applying Moore's Law, many companies can have preparation for the future in down-scaling the devices and upgrade the production to achieve the advancement of technology [18].

#### MOSFET SCALING

CPU Transistor Counts 1971-2008 & Moore's Law

Figure 2.2: Graph of CPU transistor counts from 1971-2008 & Moore's Law

Currently, Taiwan Semiconductor Manufacturing Company (TSMC) produced the smallest process node is 7nm. And besides, Samsung built the transistor into 3nm and TSMC is approved to begin the production at the end of 2022 or the beginning of 2023 [17].

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

Moore's law will possibly continued by Samsung. The Samsung will make their evolution by focusing on device performance or active diff lines or cell comparison. Along with the downscale, it will have better power performance area (PPA) per cell [18]. Besides, the Intel® 14 nm technology offer better the dimensions scaling of transistors from 22 nm. The transistor fins build to enhance their density and lower the capacitance of the devices [31]. Next, the 14 nm process and the main system-on-a-chip (SoC) product are eligible and manufactured in volume, with fabs throughout Oregon (2014), Arizona (2014), and Ireland (2015).

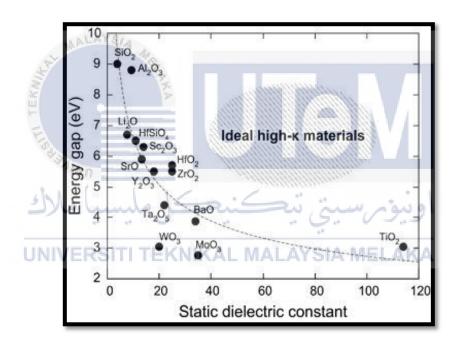

#### 2.2.2 High Permittivity (High-K) Dielectric

In this semiconductor technology, High-K is one of the focus in extensive studies recently [19]. Silicon Dioxide, SiO<sub>2</sub> gate widely used in fabricating process were replaced with High-K dielectric because of their weaknesses which is SiO<sub>2</sub> have larger high-K thus can produce a short channel effect [19]. High-K materials were introduced to produce a higher permittivity and band gap. Not just that, these materials also can improve the capacitance and obtain the minimum current leakage.

Figure 2.3: The graph of the ideal High-K materials.

#### 2.2.3 Metal Gate

A metal gate is located at the upper part of the high-K and silicon substrate in MOSFET transistor and operates for controlling the resistance in the regions.

Figure 2.4: The structure of Metal Gate in MOSFET

There are a few reasons that poly-Si was the preferred material for the past decade are metal gates were used when operating voltages were 3V to 5V. As operating voltages lowered, manufacturers transitioned to using poly-silicon as the gate material. Recently, after 45nm (for Intel) and 28nm (for TSMC), gates are again made with metal in conjunction with high-k insulators [12]. Poly-Si gates were favored because the material could be easily matched to the SiO<sub>2</sub> lattice constant, creating a no-strain, reliable structure. This structure has fallen into disfavour because it is slow and can toggle unexpectedly, as in time it alter the shape of the SiO<sub>2</sub> layer by itself.. Because high-k means high dielectric constant thus make a choice for a thinner gate size and put the contact on top [11].

#### 2.3 Graphene

Graphene is a purely two-dimensional (2D) material and graphene's atom are tightly bound in a hexagonal honeycomb lattice [19]. The characteristics of graphene are they high electron mobility at room temperature which enables the electrons in the layer to flow faster. Besides, this material are cheap to produce compared to other material in marketplace thus many devices used their materials in fabrication process. Besides, they can conduct electricity and heat which is more behavior like a metal. Then, the carbon atoms within the layers are tightly bounded and remarks as stiff material.

Figure 2.5: The structure of Graphene

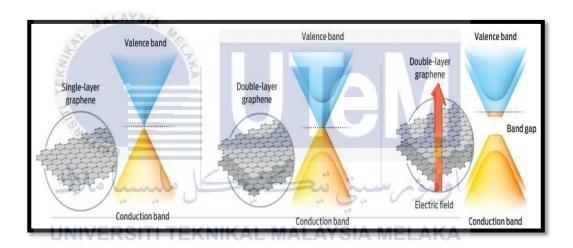

#### 2.3.1 Graphene Bandgap

To ensure the currents switched on and off, therefore the movement of electrons into conduction bands are required. Since they have a zero-bandgap regarding their characteristics that is mass-less electrons, thus the current flows within the bands cannot be stop [20]. This zero-bandgap makes the graphene to conduct like a metal which is cannot control and stop the electrons of this material.

Figure 2.6: The diagram of bandgap in Graphene.

## 2.4 Summary from Previous Research

**Table 2.1: Summary from Previous Research**

| No  | Author/Journal/Year                                        | Summary                                                                         |

|-----|------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1   | N.F. Z.A, I. Ahmad, P.J. Ker, Siti Munirah Y, Mohd Firdaus | This paper presents the modeling     and optimization of 14nm gate              |

|     | R, S.K. Mah and P.S. Menon.                                | length CMOS transistor which is                                                 |

|     | (2016). Process Parameters                                 | downscaled from previous 32nm                                                   |

|     | Optimization of 14 nm p-Type                               | gate length.                                                                    |

|     | MOSFET using 2-D Analytical                                | • Hafnium Dioxide (HfO <sub>2</sub> ) and                                       |

|     | Modeling, vol. 8, No.4, Page                               | Tungsten Silicide (WSi <sub>2</sub> )                                           |

| i i | 97-100.                                                    | • V <sub>TH</sub> and I <sub>OFF</sub> are 0.248635±12.7% V and 5.26x10-12 A/um |

| 2   | كنيكل ملسباً ملاك                                          | • (ITRS 2013)                                                                   |

| Z U | Noor Faizah Zainul Abidin, Ibrahim Ahmad, Pin Jern Ker &   | A planar Graphene Field-Effect  ALAYSIA MELAKA  Transistor GFET performance     |

|     | P. Susthitha Menon. (2017).                                | Gate length of 60 nano-meter                                                    |

|     | Performance Characterization                               | was evaluated in exploring new                                                  |

|     | of Schottky Tunneling                                      | material to meet the relentless                                                 |

|     | Graphene Field Effect                                      | demand for increasing the                                                       |

|     | Transistor at 60 nm Gate                                   | performance- power saving                                                       |

|     | Length.                                                    | features.                                                                       |

| 3 | Z. A. Noor Faizah, I. Ahmad, P.  | • A 32nm top-gated bilayer                    |

|---|----------------------------------|-----------------------------------------------|

|   | J. Ker, P. Susthitha Menon N V   | Graphene PMOS transistor                      |

|   | Visvanathan, A. H. Afifah        | • Titanium Dioxide (Ti0 <sub>2</sub> ) and    |

|   | Maheran. (2017). VTH and         | Tungsten Silicide (WSi <sub>X</sub> )         |

|   | ILEAK Optimization using         | • $V_{TH} = -0.10299V$ and $I_{LEAK} =$       |

|   | Taguchi method at 32nm           | 0.05545673nA/um                               |

|   | bilayer graphene PMOS.           | • (ITRS 2011)                                 |

|   | Afifah Maheran, A. H.a,          | • In this article, Taguchi                    |

|   | Menon, P. S.a , I. Ahmadb, S.    | orthogonal array method was                   |

|   | Shaaria. (2014). Optimisation of | used to optimize the process                  |

| 4 | Process Parameters for Lower     | parameters during the design of a             |

|   | Leakage Current in 22 nm n-      | 22nm n-type Metal Oxide                       |

|   | type MOSFET Device using         | Semiconductor Field Effect                    |

|   | Taguchi Method                   | Transistor (MOSFET) in order to               |

|   | كتيكل مليسيا ملاك                | decrease the leakage current                  |

| U | NIVERSITI TEKNIKAL M             | ALAY(I <sub>LEAK</sub> ) of the device.       |

| 5 | K.E. Kaharudin, F. Salehuddin,   | • This paper presents a study in              |

|   | A.S.M. Zain, 4m.N.I.A.           | which Taguchi method has been                 |

|   | Aziz.(2016). Taguchi Modeling    | utilized to increase the drive                |

|   | With The Interaction Test For    | current ( $I_{ON}$ ) in the $WSi_x$ / $TiO_2$ |

|   | Higher Drive Current In          | Vertical Double Gate NMOS                     |

|   | Wsix/Tio2 Channel Vertical       | Device                                        |

|   | Double Gate Nmos Device.         |                                               |

| 6        | F.Salehuddin, Ameer F.Roslan,               | • This paper investigates and                  |

|----------|---------------------------------------------|------------------------------------------------|

|          | A.E.Zailan, K.E.Kaharudin,                  | analyzes the impact of process                 |

|          | A.S.M.Zain, Afifah Maheran                  | parameter variance on the drive                |

|          | A.H., A.R.Hanim, H.Hazura,                  | current (I <sub>ON</sub> ) and leakage current |

|          | S.K.Idris, Wira Hidayat Mohd                | $(I_{OFF})$ for 19 nm $WSi_2/TiO_2$            |

|          | Saad.(2018). Analyze of                     | NMOS device using 2k-factorial                 |

|          | Process Parameter Variance In               | design                                         |

|          | 19nm Wsi2/Tio2 NMOS                         |                                                |

|          | Device Using 2k-Factorial                   |                                                |

|          | Design.                                     |                                                |

| 7        | M. Zabeli, N. Caka, M. Limani,              | • The objective of this research is            |

| Li<br>Li | Q. Kabashi. (2016). Impact of               | to analyze the impact of the main              |

|          | MOSFET's Structure                          | electrical and physical                        |

|          | Parameters on its Overall                   | parameters in characterized the                |

|          | Performance Depending to the                | MOSFET.                                        |

| Ū        | Mode Operation. EKNIKAL N                   | ALAYSIA MELAKA                                 |

| 8.       | Eliya Firhat. (2019). Minimum               | • This paper is to design and                  |

|          | Leakage current optimization                | simulate a bilayer graphene on                 |

|          | on 22nm Hafnium Dioxide                     | hafnium dioxide (Hf0 <sub>2</sub> ) /          |

|          | (Hf0 <sub>2</sub> )/ Tungsten Silicide      | Tungsten silicide (WSI <sub>x</sub> ) with     |

|          | (WSI <sub>x</sub> ) / Graphene with Silicon | SOI on 22nm NMOS device                        |

|          | on Insulator (SOI) using                    | using Silvaco Software.                        |

|          | Taguchi Method.                             |                                                |

|          |                                             |                                                |

|          |                                             |                                                |

|          |                                             | <u> </u>                                       |

| 9  | Savita Maurya. (2016).                              | This paper deals with challenges                     |

|----|-----------------------------------------------------|------------------------------------------------------|

|    | Challenges Beyond 100 nm                            | and limits of beyond 100nm                           |

|    | MOS Devices.                                        | technology.                                          |

|    |                                                     | Possible limiting factors for the                    |

|    |                                                     | scaling of devices have also been                    |

|    |                                                     | elaborated.                                          |

| 10 | S. K. Mah, I. Ahmad, P. J. Ker,                     | • In this paper, a 14nm silicon                      |

|    | Noor. (2016). Faizah Z. A.                          | based n-type MOSFET was                              |

|    | Modelling of 14NM Gate                              | virtually fabricated using                           |

|    | Length La <sub>2</sub> O <sub>3</sub> -based n-Type | Lanthanum Oxide (La <sub>2</sub> O <sub>3</sub> ) on |

|    | MOSFET.                                             | Titanium Silicide (TiSi <sub>2</sub> ).              |

|    |                                                     |                                                      |

|    |                                                     |                                                      |

## **CHAPTER 3**

# **METHODOLOGY**

Figure 3.1 indicates the flowchart of the project which is firstly, design and modeling a 22nm NMOS device with a bilayer of Graphene. The result was simulated via ATHENA and ATLAS in Silvaco Software and analyzed by referring ITRS 2012. The ATHENA in Silvaco software will be used to simulate the virtual fabrication of the NMOS devices in the software while for the ATLAS is for the electrical characteristic's properties. If the electrical characteristics are fulfilled, it is considered successful. Then, the Taguchi method are applied for analyzing the electrical characteristics of current ratio and to optimize the best combination to produce a device with better performance. The results obtained will compare with

the previous researcher and literature to determine whether the downscaling the device can reduces the leakage current,  $I_{LEAK}$  and achieve an optimum threshold voltage,  $V_{TH}$ .

Figure 3.1: Flowchart of the project

## 3.2 Experimental Setup

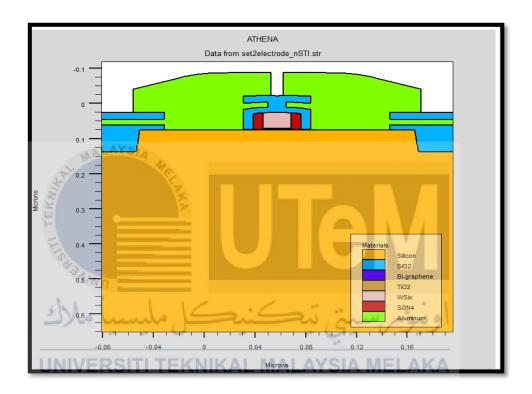

A current ratio analysis on design and modeling a 22nm Graphene / High-K and metal gate was simulated to fabricate using ATHENA and optimize electrical characteristic using ATLAS module in Silvaco software. The fabrication step takes after the same regular top-down transistor well-matched process flow with a variety of a few process parameters which exists in doping density and annealing temperature to get the outcome as the standard by ITRS specification. The substrate is prepared for similarly in this procedure. The MOSFET device process simulation entails a sequence of processing steps known as the process flow. The process started with wafer preparation, followed by well formation, isolation, transistor and interconnection as shown in the Table 3.1.

اونيونر سيتي تيكنيكل مليسياً ملاك UNIVERSITI TEKNIKAL MALAYSIA MELAKA

**Table 3.1 Fabrication step of NMOS device**

| Process Step                | n-type MOSFET parameters                                      |

|-----------------------------|---------------------------------------------------------------|

| Substrate                   | • Silicon                                                     |

|                             | • <100> orientation                                           |

|                             |                                                               |

| Retrogade well implantation | • 200 Å oxide screen by 870°C, 20                             |

|                             | min of dry oxygen                                             |

|                             | • 1x10 <sup>16</sup> ions/cm <sup>2</sup> phosphorus          |

|                             | • 30 min, 900°C diffused in nitrogen                          |

| AVA                         | • 36 min, dry oxygen                                          |

| WALATSIA 4                  |                                                               |

| STI isolation               | • 130 Å stress buffer by 900°C, 20                            |

| <u> </u>                    | min of dry oxygen                                             |

|                             | 1 1 <del>- 1</del> 1 1                                        |

| AINO                        | • 1500 Å Si <sub>3</sub> N <sub>4</sub> applying LPCVD        |

| كنيكا ملسيا ملاك            | • 1.0 μm photoresist deposition                               |

|                             | • 15 min annealing at 900°C                                   |

| UNIVERSITI TEKNIKAL MA      | LAYSIA MELAKA                                                 |

| Gate oxide                  | • Diffused dry oxygen for 0.001 min,                          |

|                             | 805°C                                                         |

|                             |                                                               |

| Vt adjust implant           | • 9.15x10 <sup>11</sup> ions/cm <sup>3</sup> Boron difluoride |

|                             | • 5.5KeV implant energy, 7° tilt                              |

|                             | • 20 min annealing at 800°C                                   |

| Graphene layer              | • 0.00068 μm graphene                                         |

|                             |                                                               |

| High-K/ Metal Gate deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | • 0.002 μm High-K dielectric                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • 0.0464 μm WSi <sub>x</sub>                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • 3.5 min, 850°C annealing                                                                            |

| Halo implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • 1.825x10 <sup>13</sup> ions/cm <sup>3</sup> indium                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • 35° tilt                                                                                            |

| Sidewall spacer deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • 0.0404 μm Si <sub>3</sub> N <sub>4</sub>                                                            |

| S/D implantation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • 9.78x10 <sup>14</sup> ions/cm <sup>3</sup> arsenic                                                  |

| AL AVe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • 8 KeV implant energy                                                                                |

| AND THE PARTY OF T | • 5° tilt                                                                                             |

| PMD deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>0.015 μm BPSG</li> <li>20 min, 855°C annealing</li> </ul>                                    |

| كنيكل مليسيا ملاك                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>1.435x10<sup>14</sup> ions/cm<sup>3</sup> phosphor</li> <li>160KeV implant energy</li> </ul> |

| UNIVERSITI TEKNIKAL MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LAYSIA MELAKA  • 7° tilt                                                                              |

| Metal 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • 0.015 μm aluminum                                                                                   |

| IMD deposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • 0.05 μm BPSG                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • 15 min, 950°C annealing                                                                             |

| Metal 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • 0.12 μm aluminum                                                                                    |