# WIRELESS POWER TRANSFER BASED ON CAPACITIVE APPROACH FOR LOW POWER APPLICATION

#### MOHAMED NORLUTFI BIN MOHAMED AS'HARI

**UNIVERSITI TEKNIKAL MALAYSIA MELAKA**

#### WIRELESS POWER TRANSFER BASED ON CAPACITIVE APPROACH FOR LOW POWER APPLICATION

#### MOHAMED NORLUTFI BIN MOHAMED AS'HARI

This report is submitted in partial fulfilment of the requirements for the degree of Bachelor of Electronic Engineering with Honours

اونيوترسيتي تيكنيكل مليسيا ملاك UNIVERSITI TEKNIKAL MALAYSIA MELAKA

Faculty of Electronic and Computer Engineering Universiti Teknikal Malaysia Melaka

**JUNE 2020**

#### **DECLARATION**

I declare that this report entitled "WIRELESS POWER TRANSFER BASED ON

**CAPACITIVE APPROACH FOR LOW POWER APPLICATION**" is the result

of my own work except for quotes as cited in the references.

Signature:

Author: MOHAMED NORLUTFI BIN MOHAMED AS'HARI

Date: 26 JUNE 2020

## **APPROVAL**

I hereby declare that I have read this thesis and in my opinion this thesis is sufficient in terms of scope and quality for the award of Bachelor of Electronic Engineering with

Supervisor Name : DR YUSMARNITA BINTI YUSOP

Date : 26 JUNE 2020

## **DEDICATION**

This project is enthusiastically dedicated toward to my dearest family, friends and

supervisor which had been help and support

#### **ABSTRACT**

A CPT system is one of the near-field technologies of WPT system where it capable to transmit signal within short range and high efficiency. The CPT system was chosen due to the benefits such as simple topology, fewer components that could assist with better performance and robustness to EMI around metallic materials, and easy to build. A Class D inverter has been analysed towards ZVS condition, input power and output power based from two difference impedance approaches that are capable to perform the conversion from DC to AC efficiently. Next, by developing the simulation of this CPT system using MATLAB software, ranges of load and distance variation are used to analyse the performance of efficiency by observing the ZVS condition and power output based from obtained waveform. This project is expected to deliver a 10Watt output power with the frequency operating of 1MHz that suits with any electronic devices with low power rate consumption and efficiency rate 85% above. Eventually, the CLL impedance seems to be the compatible impedance network for Class D inverter while maintaining a better efficiency rate compared to LCCL impedance. In future, it is much recommended to study and develop the Class D inverter with various of impedance network to analyse the performances.

#### **ABSTRAK**

Sistem CPT adalah salah satu teknologi jarak dekat sistem WPT di mana ia mampu menghantar isyarat dalam jarak pendek dan kecekapan tinggi. Sistem CPT dipilih kerana kelebihan seperti topologi sederhana, sedikit komponen yang dapat membantu dengan prestasi dan ketahanan yang lebih baik kepada EMI di sekitar bahan logam, dan mudah dibina. Penyongsang Kelas D telah dianalisis terhadap keadaan ZVS, daya input dan kuasa output berdasarkan dua pendekatan impedans perbezaan yang mampu melakukan penukaran dari DC ke AC dengan cekap. Selanjutnya, dengan mengembangkan simulasi sistem CPT ini menggunakan perisian MATLAB, rentang beban dan variasi jarak digunakan untuk menganalisis prestasi kecekapan dengan memerhatikan keadaan ZVS dan output daya berdasarkan bentuk gelombang yang diperoleh. Projek ini diharapkan dapat memberikan kuasa output 10Watt dengan frekuensi operasi 1MHz yang sesuai dengan mana-mana peranti elektronik dengan penggunaan kadar kuasa rendah dan kadar kecekapan 85% ke atas. Akhirnya, impedans CLL merupakan impedans yang serasi untuk penyongsang Kelas D sambil mengekalkan kadar kecekapan yang lebih baik berbanding dengan impedans LCCL. Di masa depan, sangat disarankan untuk mengkaji dan mencipta penyongsang Kelas D dengan impedans yang lain untuk menyelidik prestasi yang lebih baik.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to say Alhamdulillah praise to Allah, with his guidance and helps. I had completed my final year project for the given title "Wireless Power Transfer Based on Capacitive Approach for Low Power Application" successfully.

Besides, I would also like to express my sincere gratitude to my supervisor, Dr Yusmarnita Binti Yusop, who has a genius attitude and substance; she frequently and convincingly showed a spirit of adventure in terms of research and teaching enthusiasm. This thesis would not have been possible without her encouragement and constant support.

Last but not least, I do extend sincere appreciation to my friend and family who gave me support by sharing their studies and motivation experiences. Once again, thank you for all the persons involved. I may not be able to accomplish my final year project without them.

## **TABLE OF CONTENTS**

|   | 1   |     |   | ۰٠ |   |   |

|---|-----|-----|---|----|---|---|

|   | ecl | or  | o | tı | n | n |

| v |     | ıaı | а | u  | v | w |

## Approval

## **Dedication**

| Abst        | tract MALAYSIA                                 | i    |

|-------------|------------------------------------------------|------|

| Abst        | trak                                           | ii   |

| Ack         | nowledgements                                  | iii  |

| Tab         | le of Contents                                 | iv   |

| List        | of Figures UNIVERSITI TEKNIKAL MALAYSIA MELAKA | viii |

| List        | UNIVERSITI TEKNIKAL MALAYSIA MELAKA of Tables  | xi   |

| List        | of Symbols and Abbreviations                   | xii  |

| List        | of Appendices                                  | xiii |

| <b>CH</b> A | APTER 1 INTRODUCTION                           | 1    |

| 1.1         | Project Background                             | 1    |

| 1.2         | Project Objective                              | 2    |

| 1.3         | Problem Statement                              | 3    |

| 1.4         | Scope of Project                               | 3    |

|     |                                           | v  |

|-----|-------------------------------------------|----|

| 1.5 | Thesis Organization                       | 4  |

| СНА | APTER 2 BACKGROUND STUDY                  | 6  |

| 2.1 | Introduction                              | 6  |

| 2.2 | Wireless Power Transfer Technology        | 7  |

| 2.3 | Capacitive Power Transfer Topology        | 9  |

|     | 2.3.1 Class D Inverter Topology           | 10 |

|     | 2.3.2 CLL Impedance Matching              | 12 |

|     | 2.3.2.1 Zero Voltage Switching (ZVS)      | 14 |

|     | 2.3.3 Capacitance of Coupling Plate       | 17 |

|     | 2.3.4 Rectifier circuit                   | 19 |

| 2.4 | Summary                                   | 25 |

| CHA | PTER 3 METHODOLOGY                        | 26 |

| 3.1 | IntroductionSITI TEKNIKAL MALAYSIA MELAKA | 26 |

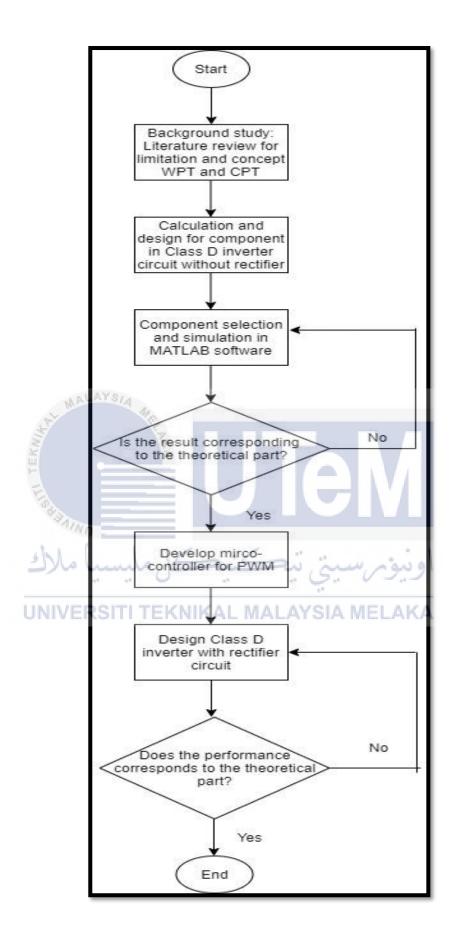

| 3.2 | Flowchart Methodology                     | 27 |

| 3.3 | CPT System Circuit Configuration          | 30 |

|     | 3.3.1 Coding for controlling the PWM      | 30 |

|     | 3.3.2 Class D inverter configuration      | 32 |

|     | 3.3.3 Impedance Matching Configuration    | 33 |

|     | 3.3.4 Rectifier Configuration             | 35 |

37

3.4

Implementation

|   |   | • |  |

|---|---|---|--|

| * | 7 | 1 |  |

|   |   |   |  |

| СНА  | APTER 4 RESULTS AND DISCUSSION                                                                                                                                                                                                                                                                                                                                                                                                           | 38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                             | 38 |

| 4.2  | Simulation Result                                                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

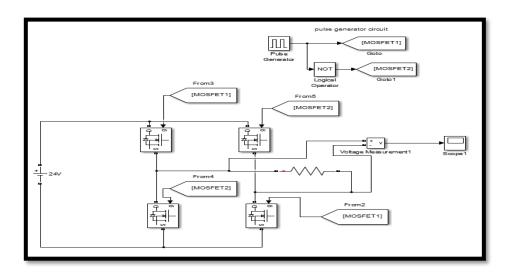

|      | 4.2.1 PWM Controls Signal Using Arduino                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

|      | 4.2.3 PWM Control Signal Using MATLAB                                                                                                                                                                                                                                                                                                                                                                                                    | 44 |

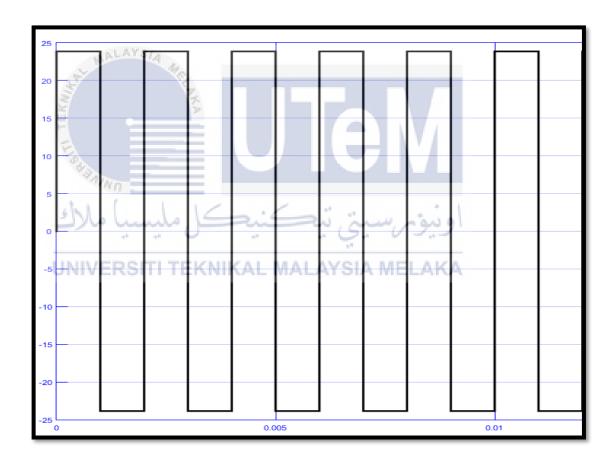

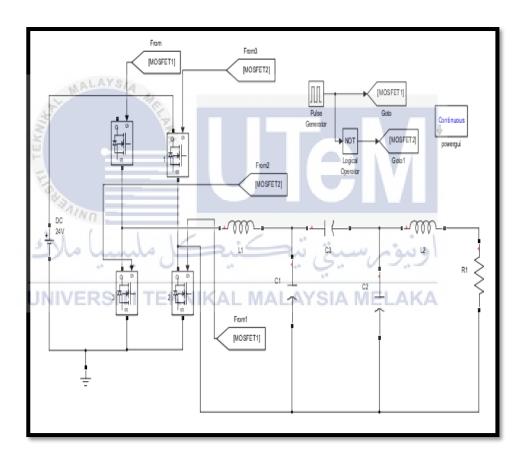

|      | 4.2.2 Class D Inverter                                                                                                                                                                                                                                                                                                                                                                                                                   | 45 |

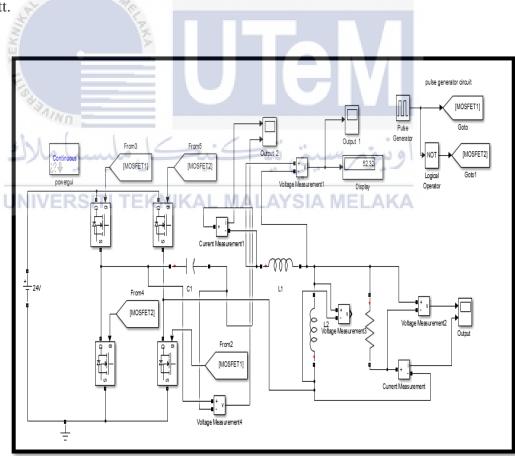

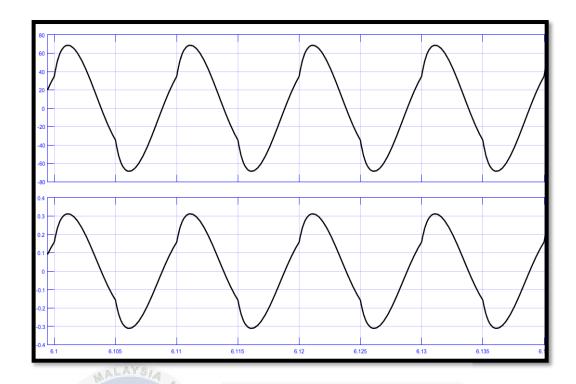

|      | 4.2.3 CLL Impedance Matching                                                                                                                                                                                                                                                                                                                                                                                                             | 47 |

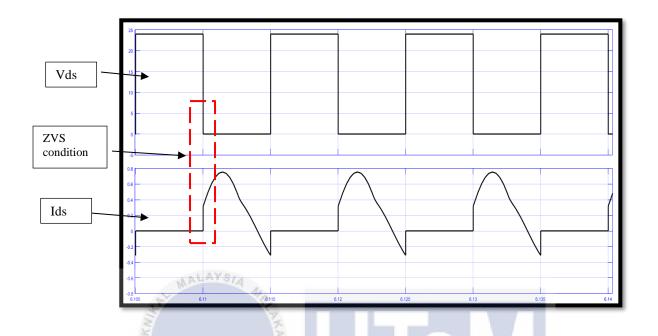

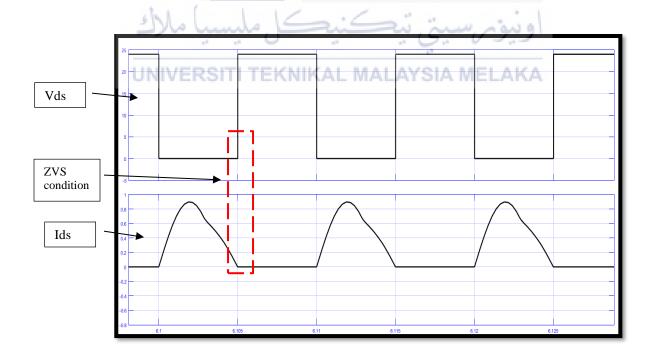

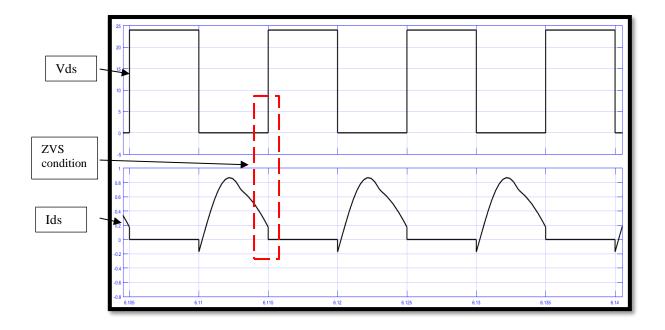

|      | <ul> <li>4.2.3.1 Analysis of ZVS by using comparison between CLL and LCCL impedance matching network (load variation) (Objective 2) (Objective 3)</li> <li>4.2.3.2 Analysis ZVS condition comparison between efficiency and load variation (CLL and LCCL impedance)</li> <li>4.2.3.3 Analysis comparison between efficiency and distance variation (CLL and LCCL impedance)</li> <li>4.2.4 CPT System Schematic (Objective 1)</li> </ul> | 51 |

| 4.3  | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                               | 65 |

| СНА  | APTER 5 CONCLUSION AND FUTURE WORKS                                                                                                                                                                                                                                                                                                                                                                                                      | 67 |

| 5.1  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

| 5.2  | Completed Work                                                                                                                                                                                                                                                                                                                                                                                                                           | 68 |

| 5.3  | Future Works                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

| Refe | rences                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

| LIST | T OF PUBLICATIONS AND PAPERS PRESENTED                                                                                                                                                                                                                                                                                                                                                                                                   | 73 |

APPENDICES 74

## LIST OF FIGURES

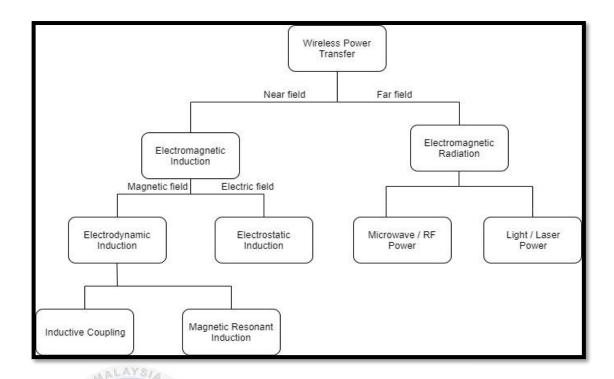

| Figure 2.1 Wireless power transfer – Overview                                              | 8             |

|--------------------------------------------------------------------------------------------|---------------|

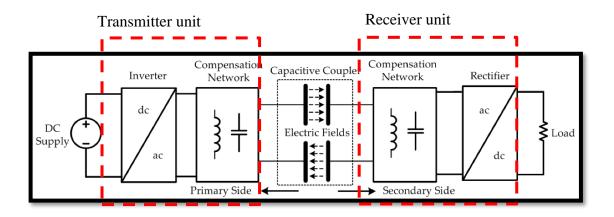

| Figure 2.2: Block diagram of proposed CPT system [15]                                      | 10            |

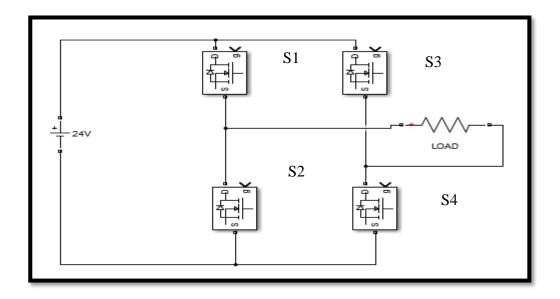

| Figure 2.3: Schematic Class D inverter with R load                                         | 11            |

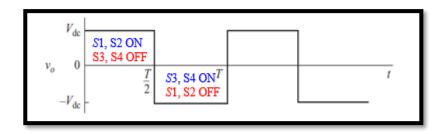

| Figure 2.4: Square wave output voltage                                                     | 12            |

| Figure 2.5: CLL Impedance matching schematic                                               | 14            |

| Figure 2.6: Series equivalent inductance                                                   | 14            |

| Figure 2.7: Voltage regulator losses occur during voltage/current ove MOSFET switches [23] | rlap when the |

| Figure 2.8: Soft-switching MOSFET current and voltage waveform [23                         | 3] 16         |

| Figure 2.9: Two-plate capacitive coupler structure SIA MELAKA                              | 18            |

| Figure 2.10: Four-plate capacitive coupler structure [25]                                  | 19            |

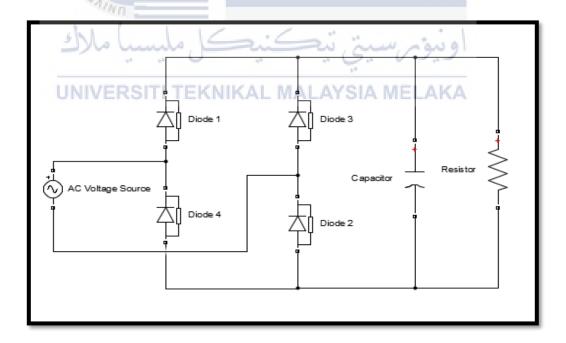

| Figure 2.11: Single phase Full-wave Rectifiers – R load                                    | 20            |

| Figure 2.12: Voltage and currents waveform                                                 | 22            |

| Figure 2.13: Full-wave rectifier with capacitance filter                                   | 23            |

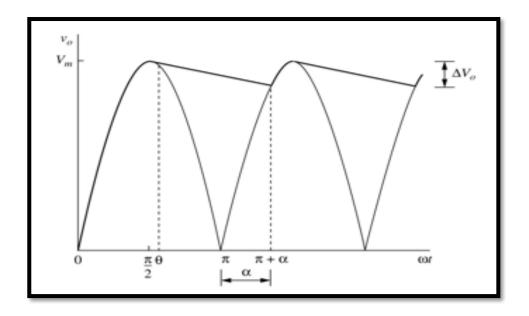

| Figure 2.14: Output voltage                                                                | 24            |

| Figure 3.1: Flowchart for methodology                                                      | 29            |

| Figure 3.2: Arduino UNO software                                                           | 30            |

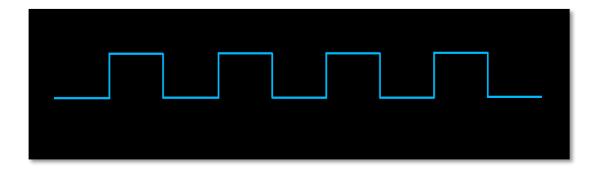

| Figure 3.3: A PWM signal (square wave) with a 50% duty cycle                               | 31            |

| Figure 3.4: PWM signal (square wave) with a 0% duty cycle                                  | 31            |

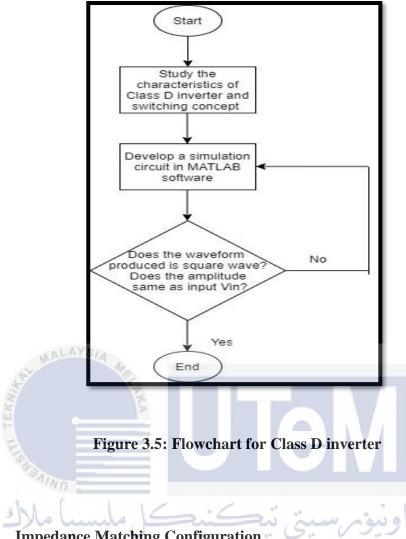

| Figure 3.5: Flowchart for Class D inverter                              | 33 |

|-------------------------------------------------------------------------|----|

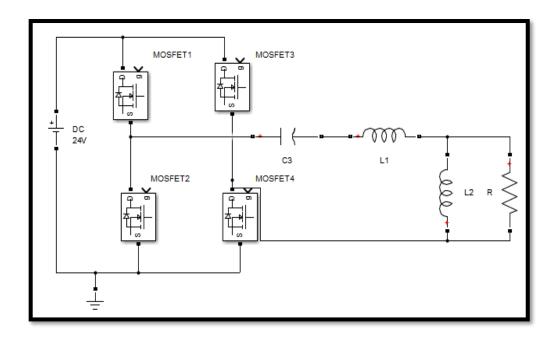

| Figure 3.6: Class D inverter with CLL impedance matching schematic      | 34 |

| Figure 3.7: Flowchart of rectifier                                      | 36 |

| Figure 3.8: Picture of CPT system for purposes of low power application | 37 |

| Figure 4.1: Simulation PWM connection (Proteus Software)                | 42 |

| Figure 4.2: PWM waveform (inverted signal)                              | 43 |

| Figure 4.3: Connection of pulse generator in MATLAB (Simulink)          | 44 |

| Figure 4.4: Setting of duty cycle and frequency                         | 45 |

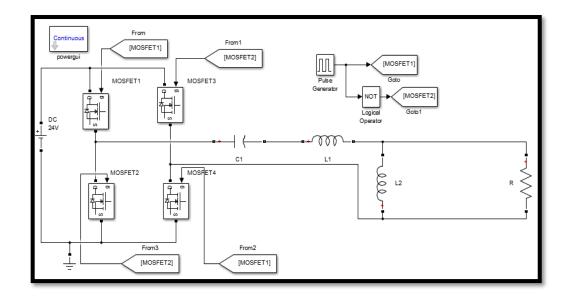

| Figure 4.5: Class D inverter with R load schematic                      | 45 |

| Figure 4.6: Class D inverter output waveform                            | 46 |

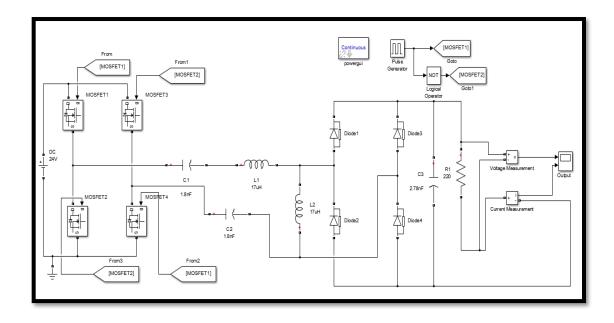

| Figure 4.7: CLL impedance matching schematic                            | 47 |

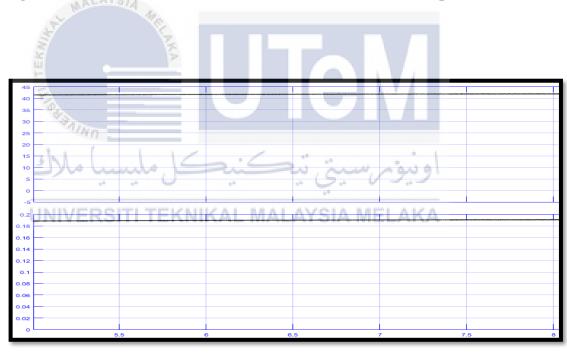

| Figure 4.8: Voltage and current output waveform for CLL impedance       | 49 |

| Figure 4.9: Class D inverter with LCCL impedance matching               | 50 |

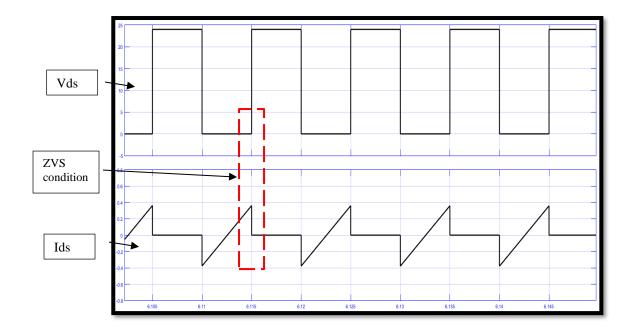

| Figure 4.10: ZVS condition CLL impedance (100 $\Omega$ )                | 52 |

| Figure 4.11: ZVS condition CLL impedance (220Ω) A MELAKA                | 52 |

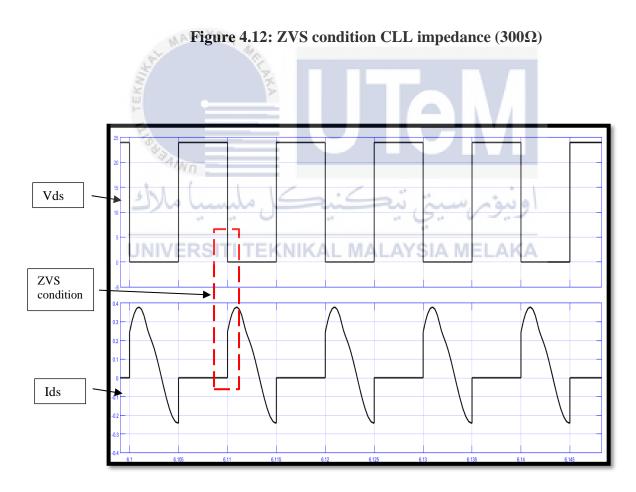

| Figure 4.12: ZVS condition CLL impedance (300 $\Omega$ )                | 53 |

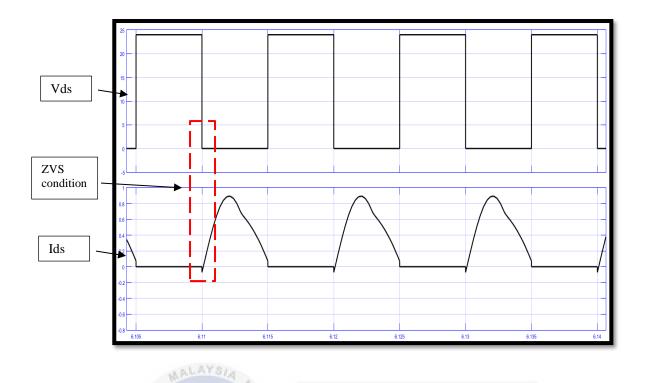

| Figure 4.13: ZVS condition LCCL impedance (100 $\Omega$ )               | 53 |

| Figure 4.14: ZVS condition LCCL impedance (220 $\Omega$ )               | 54 |

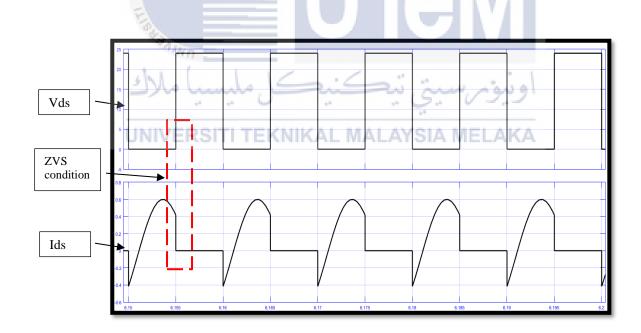

| Figure 4.15: ZVS condition LCCL impedance (300 $\Omega$ )               | 54 |

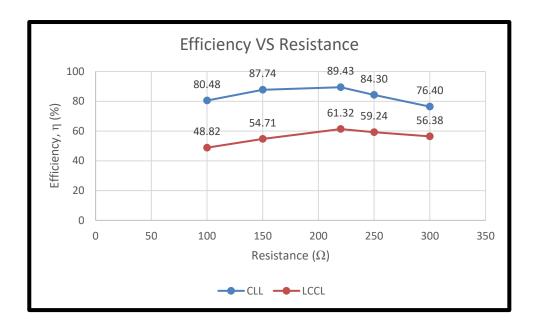

| Figure 4.16: Efficiency VS Resistance graph                             | 56 |

| Figure 4.17: ZVS condition CLL impedance (1mm)                          | 57 |

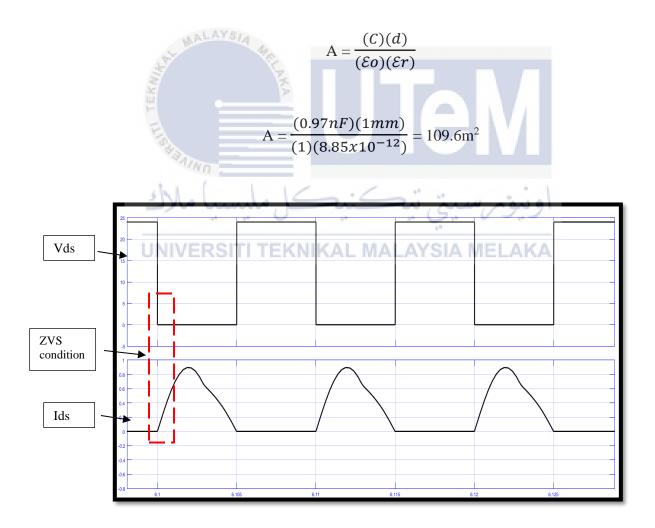

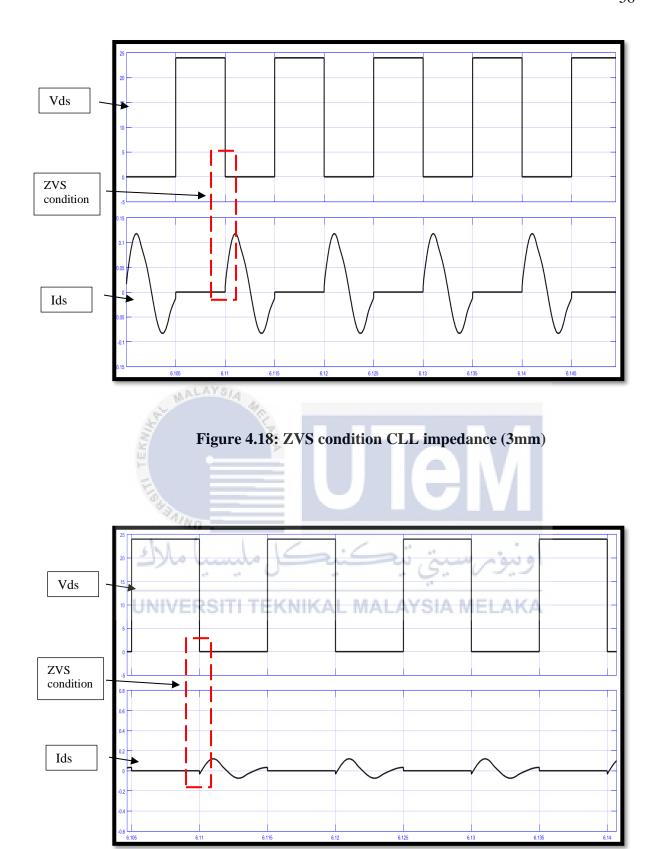

| Figure 4.18: ZVS condition CLL impedance (3mm)                          | 58 |

| Figure 4.19: ZVS condition CLL impedance (5mm)                          | 58 |

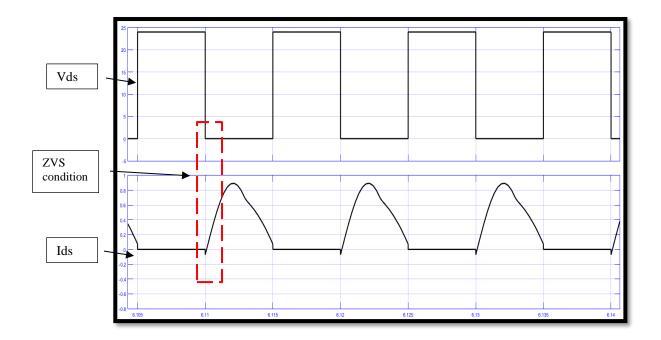

| Figure 4.20: ZVS condition LCCL impedance (1mm)                               | 59 |

|-------------------------------------------------------------------------------|----|

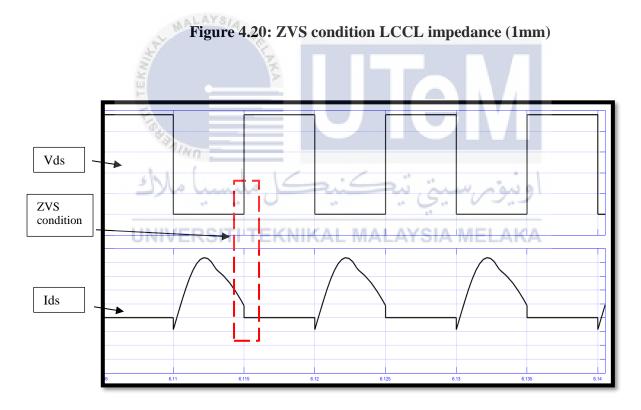

| Figure 4.21: ZVS condition LCCL impedance (3mm)                               | 59 |

| Figure 4.22: ZVS condition LCCL impedance (5mm)                               | 60 |

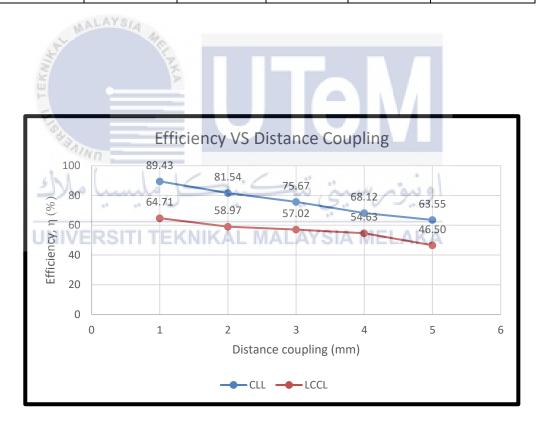

| Figure 4.23: Efficiency VS Distance coupling graph                            | 61 |

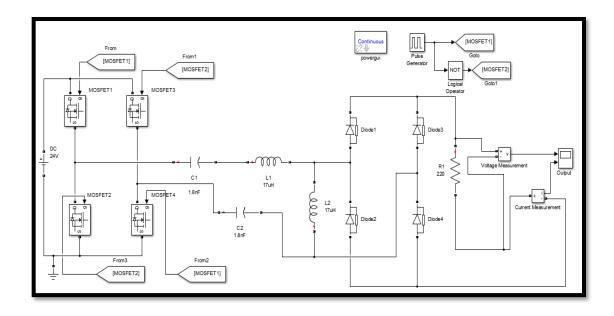

| Figure 4.24: CPT system schematic with Full-wave rectifier                    | 63 |

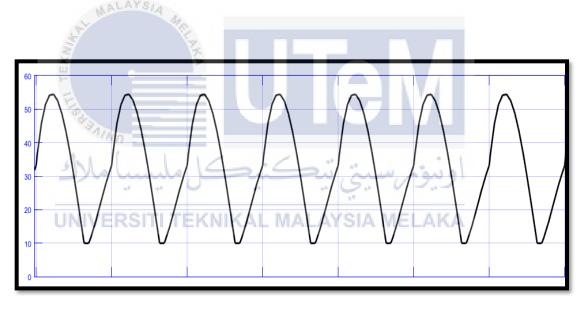

| Figure 4.25 : Output voltage CPT system schematic with Full-wave rectifier    | 63 |

| Figure 4.26: CPT system schematic with Full-wave rectifier (Capacitor filter) | 64 |

| Figure 4.27: Voltage and current output                                       | 64 |

## LIST OF TABLES

| Table 4.1: Calculation for Class D inverter parameter          | 39 |

|----------------------------------------------------------------|----|

| Table 4.2: Parameter Class D inverter                          | 46 |

| Table 4.3: Simulation results                                  | 48 |

| Table 4.4: Component values                                    | 48 |

| Table 4.5: Output results for CLL impedance matching schematic | 49 |

| Table 4.6: Component values for LCCL impedance                 | 51 |

| Table 4.7: Parameter for CLL impedance load variation          | 55 |

| Table 4.8: Parameter for LCCL impedance load variation         | 55 |

| Table 4.9: Parameter for CLL impedance distance variation      | 60 |

| Table 4.10: Parameter for LCCL impedance distance variation    | 61 |

| Table 4.11: Output results for CPT system with rectifier       | 65 |

#### LIST OF SYMBOLS AND ABBREVIATIONS

SITI TEKNIKAL MALAYSIA MELAKA

WPT : Wireless Power Transfer

CPT : Capacitive Power Transfer

AC : Alternating current

DC : Direct current

CLL: Capacitor Inductor - Inductor

EMI : Electromagnetic Interference

ZVS : Zero Voltage Switching

IPT : Inductive Power Transfer

V<sub>DC</sub> : Volts Direct Current

PWM : Pulse Width Modulation

LED : Light Emitter Diode

RMS : Root Mean Square

ESR : Equivalent Series Resistance

## LIST OF APPENDICES

Appendix A: PWM Coding Using Arduino

Appendix B : IRFZ44 MOSFET Datasheet

#### **CHAPTER 1**

#### **INTRODUCTION**

The first chapter of this thesis discusses the context of the project, project objective, problem statement of the project, scope of the project, an overview of the methodology, and project outline.

#### 1.1 Project Background

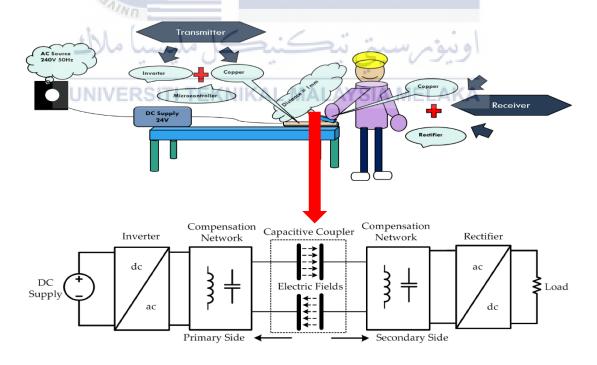

Nowadays, Wireless Power Transfer (WPT) has the potential to liberate us from power cord tyranny. This engineering is integrated into tools and systems of all kinds. This system could perform through an air gap, without needs from current-carrying wires. Instead of using physical connectors such as wires, the WPT may produce power from an alternating current (AC) source to any suitable batteries or devices. This

system also can be categorized into two part of technologies which are near-field and far field transmission. [1]

Capacitive Power Transfer (CPT) is one of the near-field transmission and advantageous systems in the WPT system. [2] The versatility of capacitive interfaces and their low cost had encouraged them to be very pleasing in the WPT system. The primary purpose of developing the CPT system is to prevent the disadvantages of WPT, where the issue of electromagnetic interference (EMI) possibly occurs, and the chances of the magnetic field to penetrate between the power source and load through a metal barrier is null. Hence, to increase the magnetic efficiency, obtaining a dependable coupling factor, and disallow EMI, the use of a magnetic shield and special shield are proposed.

A circuit topology where it consists of a Class D inverter along with a CLL matching circuit is proposed to operate the CPT system. This topology is capable of executing the direct current (DC) to AC conversion efficiently with corresponding to the switching losses by using MATLAB software and experimental approach. Next, to ensure the performance of the developed circuit, the input power, output power, switching losses, and dc-dc efficiency needs to be considered.

Eventually, the output power for the system expected to acquire 10W efficiently and able to suit any low power application. With the elimination of using physical wires, the appearance and sustainability of WPT on any low power application could be enhanced.

#### 1.2 Project Objective

In this study, several important goals were outstandingly set to be achieved after this task is completed.

- Design a CPT system based on Class D inverter topology that can enhance the system efficiency.

- 2. To analyze the performance of the developed CPT system based on Zero Voltage Switching (ZVS) condition, input power, output power and efficiency.

- Optimize the efficiency of CPT system using multistage impedance matching circuit that is capable of improving the ZVS condition that are less sensitive to the load and coupling variation.

#### 1.3 Problem Statement

Currently, the most common application of the WPT system used is Inductive Power Transfer (IPT). Still, then, the limitation of penetrating metal and electromagnetic interference (EMI) make the CPT system more reliable.

It is suitable to use a CPT system for an application that produces low power consumption due to the limitation of exhibits output power and efficiency. Moreover, the effectiveness of the system depends on the gap distance between the coupling plate and load variation. Hence, the solution solved by using the Class D inverter with the CLL impedance matching network.

#### 1.4 Scope of Project

This project works in several parts. The initial stage begins with the simulation of Class D inverter by using MATLAB software to simulate the circuit and achieve the condition of Zero Voltage Switching (ZVS). Hence, power MOSFET was used as switches, and meanwhile, the performances were analyzed by applying ZVS condition, input power, output power, and efficiency. On the other hand, the Class D inverter

combines with the CLL matching network to produce resonance circuits and efficient power transfer. Regarding the capacitive coupling plate, this project proposed to replace the four plates of capacitive copper or known as Bipolar structure with using a couple of capacitor at the transmitter and receiver part. [3] Some of the values of the parameter in developing the CPT system has been set initially to obtain the desired output.

- ➤ Input voltage = 24Volt

- ➤ Output power = 10Watt

- $\triangleright$  Frequency, f = 1MHz

- ➤ Distance gap between plates ≤1mm

- $\triangleright$  Duty cycle = 0.5

- $\triangleright$  Efficiency,  $\eta = \ge 85\%$

# UTeM

#### 1.5 Thesis Organization

Generally, there are five chapters to be written in this thesis. Each chapter had been organized structurally.

- Chapter 1 consist of the introduction of project, objective, problem statement, scope of work and thesis organization.

- Chapter 2 explains the literature review of CPT system based from the study on previous research.

- Chapter 3 will interprets the work flow and description towards completing this project.

- Chapter 4 is about explaining the progress result of project and discussion.

• Chapter 5 concludes the whole research and proposes the future enhancement of project.

#### **CHAPTER 2**

#### **BACKGROUND STUDY**

This chapter will discuss any literature discourse and review of the CPT system based on any sound sources such as journals, books, and relevant sources. In the process of developing this project, information and concept are essential to be considered as references to obtain the desired output and completed this project.

#### 2.1 Introduction

In this technology era, WPT is the most significant system that people have been using nowadays. Due to the current trends, the awareness of the WPT through the use of the CPT method is essential for the understanding and will be reviewed in this

chapter. Throughout in developing this project, a number of researches and studies have been done for the topic of the WPT system, CPT system, capacitive coupling plate, Class D inverter/converter, and resonance circuit.

#### 2.2 Wireless Power Transfer Technology

Due to the reduction of low power density, high cost, and heavyweight, unique technical challenges are faced with the design and deployment of the battery-powered system. Hence, the WPT system has been introduced where it provides a brand new way for an electrical-driven device to obtain energy, thus increasing overdependence on the battery. [4] WPT system is capable of delivering an overview of the concept as well as an excellent analysis of the development issues to be addressed to achieve optimal efficiency in high power transmission. [5] Besides, it also offers an excellent introduction to high-resonance WPT design theory, explaining fundamental system principles such as frequency splitting, ideal operating distance (capacitive coupling), and device behavior as it becomes over and under-coupling.

Generally, the WPT system consists of two conventional techniques in delivering power, which are the far-field and the near-field transmissions. [6] By adopting the acoustic, optical, and microwave as the energy carrier, the far-field WPT can be realized. On the other hand, the near-field technique uses the inductive coupling effect of non-radiative electromagnetic fields, including capacitive and inductive mechanisms. According to the project title research, CPT has been chosen over inductive power transfer (IPT) due to the advantages of the capability of penetrating through metal-body, reduce energy loss, and good anti-interference ability of the magnetic field. [7]

Figure 2.1 Wireless power transfer – Overview

It usually is possible to compare the form of WPT with IPT and CPT method, where both of the systems are frequently used in a wide variety of applications nowadays. Firstly, the achievable power density for both systems makes them different from others, where the IPT is capable of high power density compared to CPT. In mutual methods, currently, the industry technology prefers contact-base electrical connection with the WPT method rather than the IPT. The concurrent concern in a variety of applications is the development of the IPT. Usually, this feature uses WPT stand for rotational devices that transfer power between stationary and rotating components using slip rings.

There is an inductive system of the immense dominance of inductive systems in the mechanical structure. Still, the capacitive methods have niche applications within the motor or generator community of Microelectromechanical System (MEMS). Thus, it

is effortless for the capacitive method to be designed at the MEMS scale. Moreover, it contains a power density equal to or higher than its magnetic equivalents.

The theoretical development of IPT technology has been very successful. It will provide power in the range of industrial applications such as powering consumer electronics devices, powering connections for implantable medical devices, [8] electric vehicle charging, [9] and wireless charging for robots. [10] Nevertheless, the main weakness of IPT has made the system hard to be implemented. [11] Last but not least, the CPT system completely overcomes the IPT limitation, where it is much better in penetrating a metal shielding environment.

#### 2.3 Capacitive Power Transfer Topology

CPT system is a system that relies on the coupling capacitance that use to transmit power. [12] Due to the advantages of capability on penetrating through any metal shielding environment and achieving high power density, the CPT system has been dominance in the innovation technology nowadays based on electrical field coupling in WPT. [13]

By referring to Figure 2.2, the CPT system topology consists of two main parts where primary side reacts as the transmitter unit while the secondary side represents the receiver unit. The purpose of transmitter unit is to transform the signal from dc signal to high-frequency ac signal because the capacitive coupling requires only ac energy to transfer the power via the electrical fields. [14] Apart from that, an inverter is required to perform the conversion signal task. Meanwhile, in the receiver unit,

high-frequency ac energy is safely converted back into dc with the used of rectifier to meet the requirements specified by the load parameters.

Figure 2.2: Block diagram of proposed CPT system [15]

#### 2.3.1 Class D Inverter Topology

A Class D inverter that contain numbers of power MOSFET use to transmit the dc signal with peak amplitude same as the voltage input signal received with considering the total resistance in power MOSFET and voltage forward of diode. The power MOSFET are responsible to create a switching signal condition and react as the switches. The output signal produced by the Class D is supposed to be in a digital signal and continuous time depending on the instantaneous duty cycle. [16] In Figure 2.3 shows the schematic of Class D inverter with resistor load.

Figure 2.3: Schematic Class D inverter with R load

In this application, an AC output is synthesized from a DC input by closing and opening the switches in an appropriate sequence. [17] The output voltage V<sub>0</sub> can be +V<sub>DC</sub>, -V<sub>DC</sub>, or zero, depending on which switches are closed. Note that S<sub>1</sub> and S<sub>2</sub> the should not be closed at the same time, nor should S<sub>3</sub> and S<sub>4</sub>. Otherwise, a short circuit would exist across the Dc source. Real switches do not turn ON or OFF instantaneously. Therefore, switching transition must be accommodated in the control of the switches by developing the PWM controller. [18] Overlap of switch "ON" times will result in a short circuit, sometimes called a *shoot-through fault*, across the DC voltage source. In practical, the dead time is required to avoid "shoot-through" faults.

The simplest switching scheme for the Class D inverter produces a square wave output voltage. The switches connect the load to  $+V_{DC}$  when  $S_1$  and  $S_4$  are closed or to  $-V_{DC}$  when  $S_2$  and  $S_3$  are closed. By referring to Figure 2.4, the periodic switching of

the load voltage between  $+V_{DC}$  and  $-V_{DC}$  produces a square wave voltage across the load. Although this alternating output is non-sinusoidal, it may be an adequate AC waveform for some application.

Figure 2.4: Square wave output voltage

#### 2.3.2 CLL Impedance Matching

The DC-to-AC voltage transfer function of the inverter is almost independent of the load variations at a switching frequency higher than the resonant frequency.

[19] An important advantage of the inverter is that the load presented by the resonant circuit to the switches is inductive at this frequency. [20] In addition, the circuit has high efficiency over a wide range of load resistance.

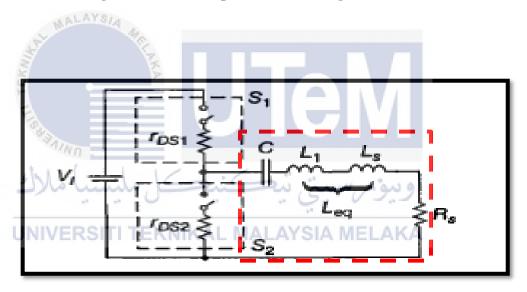

The CLL resonant inverter shown in Figure 2.5 is composed of four bidirectional four-quadrant switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  and a resonant circuit  $CL_1L_2$ . The resonant capacitor C is connected in series with the inductor  $L_1$  and  $L_2$  while the load is connected in parallel with the inductor  $L_2$ . The switches consists of MOSFETs and their body diodes, and are driven by rectangular-wave voltage sources  $v_{gs1}$  and  $v_{gs2}$ . Each switch can conduct a positive or a negative current. The transistors are driven by rectangular wave voltage sources  $v_{gs1}$  and  $v_{gs2}$ . Switches  $S_1$  and  $S_4$ ,  $S_2$  and  $S_3$  are

alternatively turned on and off at the switching frequency  $f = \omega/2\pi$  with a duty cycle 50%.

The parallel R and  $L_2$  can be converted into a series Rs-Ls circuit as shown in Figure 2.6 at a given frequency. The total series equivalent inductance is  $Leq = L_1 + L_s$ . In Figure 2.6 also, the DC voltage source and the switches  $S_1$  and  $S_4$ ,  $S_2$  and  $S_3$  are modeled by a square-wave voltage source, where the low level of the square wave is zero and the high level is  $V_{DC}$ . The equivalent on-resistance of the MOSFETs is  $r_{DS} \approx (r_{DS1} + r_{DS2})/2$ . The parasitic resistance r of the inverter is composed of the resistance of the switch  $r_{DS}$ , the equivalent series resistance (ESR) of the capacitor  $r_{Cr}$ , and the ESR<sub>s</sub> of the inductors  $r_{L1}$  and  $r_{L2}$ .

Waveforms in the CLL inverter for  $f > f_r = 1 / (2\pi\sqrt{LeqC})$  are the same as parallel-resonant inverter. The operation of the inverter above resonance is preferred because the reverse recovery of the MOSFET body diodes does not affect adversely the circuit operation. The input voltage vds2 of the resonant circuit is a square wave. Assuming the loaded quality factor or at the resonant frequency  $f_r$  is high, the capacitor current i is nearly sinusoidal and flows alternately through switches  $S_1$  and  $S_4$ , or  $S_2$  and  $S_3$ .

If  $R << X_{L2} = \omega L_2$ , most of the capacitor current flows through the load resistance, and therefore  $I_m$  is inversely proportional to the load resistance, resulting in high part-load efficiency. When the load resistance R becomes greater than  $X_{L2}$ , most of the capacitor current flows through the resonant inductor  $L_2$ , making  $I_m$  independent of R. Therefore, the efficiency is low at part loads.

Figure 2.5: CLL Impedance matching schematic

Figure 2.6: Series equivalent inductance

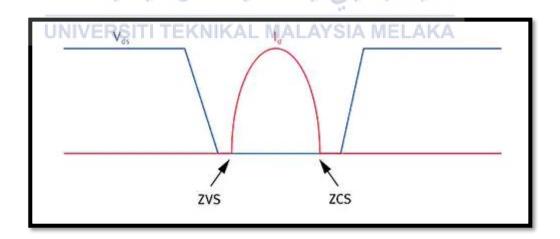

#### 2.3.2.1 Zero Voltage Switching (ZVS)

Zero Voltage Switching (ZVS) is one solution which allows a return to faster switching frequency at higher input voltage and voltage drop. [21] Like virtually all contemporary switching voltage regulators, this technique uses pulse width modulation (PWM)-based operation, but with a different additional phase to the PWM

timing to permit for ZVS operation. ZVS allows for "soft switching" by the voltage regulator, preventing the switching losses typically accrued during conventional operation and timing of PWM.

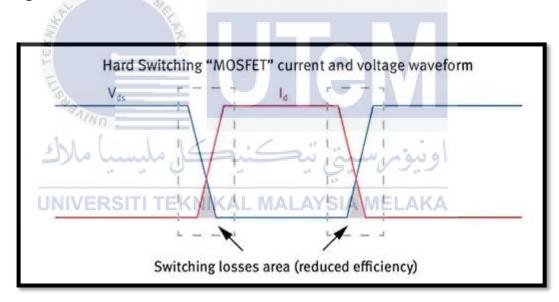

While many contemporary non-isolated buck voltage regulators suffer high-switching losses due to the simultaneous presence of high-current and the voltage stress on the integrated MOSFET of the regulator during the transitions. With switching frequency and input voltage, these losses increase and limit the operation of maximum frequency, efficiency, and power density. Hard switching presences when the MOSFET switches performing transition on and off during the overlap between voltage and current. [22]

Figure 2.7: Voltage regulator losses occur during voltage/current overlap when the MOSFET switches [23]

Increased electromagnetic interference (EMI) arising from the voltage regulator circuitry is the drawback of fast switching. In other hands, there is one method to reduce EMI effects by using a switching regulator that uses an improved

hard-switching technique called quasi-resonant switching or known as "valley" switching, while also making advantage of fast switching to increase performance. The MOSFET is turned on during quasi-resonant switching when the voltage across drain and source is at a minimum (in a valley) to reduce the switching losses. This enables the device to operate with a more modest voltage or current change rate, thereby reducing EMI. Another side benefit of quasi-resonant switching is that a degree of frequency latency is added, increasing the RF emission spectrum and further reducing the EMI, as switching is activated when a valley is detected, rather than at a constant frequency.

Quasi-resonant switching is a useful approach for assessing the productivity of voltage converters, but the execution of full soft switching can further improve the situation. [23] The voltage decreases to zero before turning on or off the MOSFET during soft switching, removing any variation between voltage and current and reducing losses.

Figure 2.8: Soft-switching MOSFET current and voltage waveform [23]

A conventional PWM power conversion during the MOSFET's on time but with "resonant" switching transitions is the best term to be explained for soft switching. The method was considered as PWM power using a constant off-time control that changes the frequency of conversion, or on-time to maintain output voltage regulation. For a given unit of time, this approach is synonym to constant frequency conversion using an adjustable duty cycle.

The control of the output voltage is accomplished by changing the effective duty cycle (and therefore on-time), by varying the frequency of conversion. During the off-time ZVS switch, the resonant tank circuit of the regulator resonates through the voltage through the switch from zero to its peak and back to zero when the switch can be reactivated, facilitating lossless ZVS.

The advantages of ZVS are that it capable to reduces the harmonic spectrum of any EMI (centering it on the switching frequency) and permit higher frequency operation resulting in reduces, easier to filter noise and the use of minor filter components.

# UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### 2.3.3 Capacitance of Coupling Plate

By recognizing the relationship between distance and efficiency of the capacitive coupling sheet, the performance of the CPT device can be optimized. Next, by referring to Equation 2.1, the capacitance can be inferred, as defined by the plate area, is directly proportional to the dielectric constant and physical size of the surface. Capacitance is inversely proportional to the distance between plates. [24]

$$C = \frac{A\mathcal{E}_{\circ}\mathcal{E}r}{d} \tag{2.1}$$

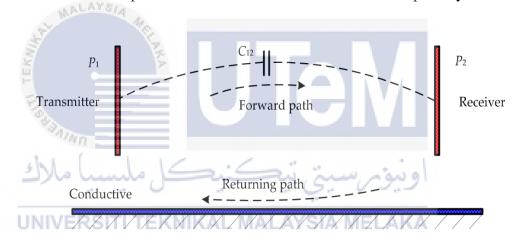

Generally speaking, several capacitive plate systems are consisting of a two-plate coupler structure, four-plate parallel structure, stacked structure, six-plate structure, and repetitive structure. Two-plated coupler arrangement, as shown in Figure 2.9, also known as the bipolar structure of the CPT system, has a more straightforward benefit than any other. The system uses only two plates for power transfer, where the first is for the transfer power, and other use to receive the energy. The relation between these two plates in the conductive path would influence the resulting of a quasi-wireless CPT device as a metal to the metal power receiver. Next, the mutual capacitance between two plates provides the way for the current to flow forward to the load and then needs a conductive path to allow the current to rush back to the primary side.

Figure 2.9: Two-plate capacitive coupler structure

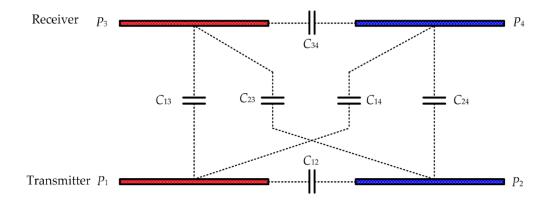

In the other hands, a four plate parallel structure is also known as a bipolar structure. Conversely, four plate structure is connecting each other in the parallel form as shown in Figure 2.10.

Figure 2.10: Four-plate capacitive coupler structure [25]

Each plate in Figure 2.10 is the coupling capacitance. This will result in six capacitances, where  $C_{13}$  and  $C_{24}$  are known as the vital coupling capacitances, then  $C_{14}$  and  $C_{23}$  are classified as cross-coupling capacitances. On the other hand, the  $C_{12}$  and  $C_{34}$  are defined as the self-coupling capacitance. The capacitive coupler works as a two-port network where the primary port is the input and secondary port react as the output. [26] It should be emphasized that this two-port network can be used as the equivalent of various coupler structures.

The difference between the configurations, on the other hand, would affect the power transfer efficiency because the CPT system is a small volume and profile, particularly on the receiving side of power, which means it can be used for small scale applications. The flexibility in design and low cost makes it ideal when compared to the other WPT type for power delivery in the reconfigurable and moving system.

#### 2.3.4 Rectifier circuit

In Figure 2.2 has already explained the purpose of rectifier circuit that contribute to this system. In addition, regarding the circumstances, the ac-to-dc

converter safely converts the high frequency ac power to suitable shape with the load parameter requirements and predominantly uses a diode rectifier with capacitive filter as the ac-to-dc converter.

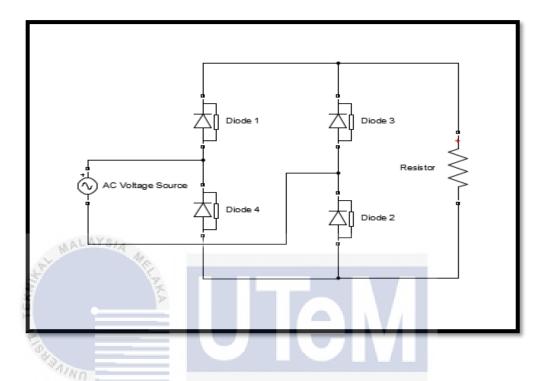

Figure 2.11: Single phase Full-wave Rectifiers – R load

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

Diodes  $D_1$  and  $D_2$  conduct together and  $D_3$  and  $D_4$  conduct together. Kirchoff's voltage law around the loop containing the source,  $D_1$  and  $D_3$  cannot conduct simultaneously. The load current can be positive or zero but can never be negative. Besides, the voltage across the load is +Vs when  $D_1$  and  $D_2$  are ON. The voltage across the load is -Vs when  $D_3$  and  $D_4$  are ON. The maximum voltage across a reverse-biased diode is the peak value of the source. This can be shown by Kirchoff's voltage law around the loop containing the source  $D_1$  and  $D_3$ . With  $D_1$  ON, the voltage across  $D_3$  is -Vs.

Next, the current entering the bridge from the source is  $I_{D1}$  –  $I_{D4}$ , which is symmetric about zero. Therefore, the average source current is zero. Moreover, the rms source current is the same as the rms load current. The source current is the same as the load current for one-half of the source period and is the negative of the load current for the other half. The squares of the load and source currents are the same, so the rms current are equal.

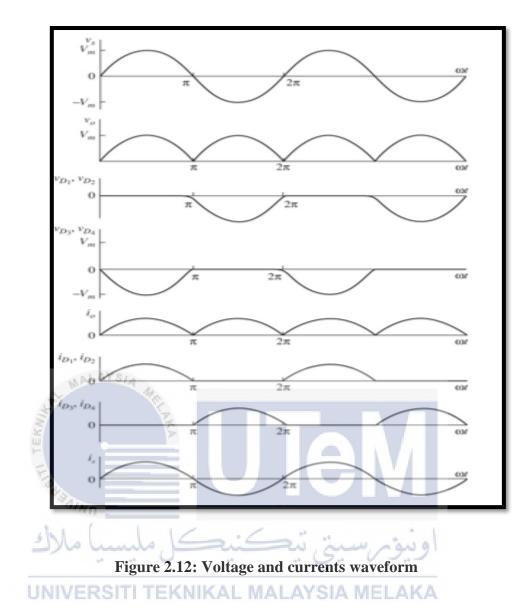

The fundamental frequency of the output voltage is  $2\omega$ , where  $\omega$  is the frequency of the ac input since two periods of the output occur for every period of the input. The Fourier series of the output consists of a DC term and the even harmonics of the source frequency.

The voltage across a resistive load for the bridge rectifier is expressed as:

Vo

$$(\omega t) = \{ \text{Vm sin } \omega t \text{ for } 0 \le \omega t \le \pi$$

(2.2)

$$\{ -\text{Vm sin } \omega t \text{ for } \pi \le \omega t \le 2\pi \}$$

The DC component of the output voltage is the average value and load current is simply the resistor voltage divided by resistance:

$$Vo = \frac{1}{\pi} \int Vm \sin \omega t \ d(\omega t) = \frac{2Vm}{\pi}$$

$$Io = \frac{Vo}{R} = \frac{2Vm}{\pi R}$$

(2.3)

The rms output current:

$$Irms = \frac{Im}{\sqrt{2}}$$

(2.4)

Then, placing a large capacitor in parallel with a resistive load can produce an output voltage that is essentially DC. In the full-wave circuit, the time that the capacitor discharges is smaller than that for the half-wave circuit because of the rectified sine wave in the second half of each period. Figure 2.13 and Figure 2.14 shows the diagram of full-wave rectifier with capacitance filter and the output voltage.

Figure 2.13: Full-wave rectifier with capacitance filter

Figure 2.14: Output voltage

The output voltage can be defined from the equation as stated below by assuming ideal diodes.

$$V0 (\omega t) = \begin{cases} |Vm \sin \omega t| & \text{one diode pair on} \\ (Vm \sin \theta)e^{-\frac{\omega t - \theta}{\omega RC}} & \text{diodes off} \end{cases}$$

(2.5)

Where  $\theta$  is the angle where the diodes become reverse biased as stated in equation 2.6, which is the same as that for the half-wave rectifier.

$$\theta = \tan^{-1}(-\omega RC) = -\tan^{-1}(\omega RC) + \pi \tag{2.6}$$

The peak-to-peak voltage variation, or ripple, is the difference between maximum and minimum voltages as stated in equation 2.7.

$$\Delta Vo = Vm - |Vm \sin(\pi + \alpha)| = Vm (1-\sin \alpha)$$

(2.7)

The approximation of peak-to-peak ripple can be defined in the equation 2.8.

$$\Delta V_0 \approx \frac{Vm\pi}{\omega RC} = \frac{Vm}{2fRC} \tag{2.8}$$

#### 2.4 Summary

This section discusses the concept of Class D inverter, impedance matching network and rectifier. This complete topology seems to be suitable for any electronic devices that consume with low power application. Therefore, the Class D inverter is used for the non-dissipative switching through the ZVS method to achieve higher efficiency and reduce stress in the semiconductor power rating. [27]

Besides, the CLL resonant inverter topology that used in this system is capable to achieve zero-voltage switching from zero load to a full load and zero current switching for output rectifiers and makes the implementation of a secondary rectifier easy. The power distribution depends on both load impedance and relative positions of receivers to the transmitter. [28] It is important to analyze the performance of Ids and Vds at MOSFET configuration (no overlapping occurred) in order to ensure the power losses at power input are avoided by applying a high operating frequency. [29] Next, an optimized design approach is suggested to achieve high performance over a wide load spectrum, understanding that dead time is a critical factor affecting the entire system design and using thorough investigation.

#### **CHAPTER 3**

#### **METHODOLOGY**

In chapter one, there are roughly explanation had been discuss through the concept and fundamental of this project. Then, in this chapter will elaborate more about the methods that implemented to accomplish this project. The overall methods explain based on the flowchart and introduction to the project construction.

#### 3.1 Introduction

This approach offers detail and accurate data on the characteristic of the devices used in this CPT system. All the information used in this project based on the summarized review in chapter two.

Next, the initial process in developing this project is by considering the value of components used in the CPT system. A strong fundamental of electronic theories is required in order to well-performed this part. After that, it is possible to simulate the

circuit to obtain mutual results with the mathematical approach before proceed to the experimental parts. All the results then will be analyzed based on input power, output power and efficiency. At last, the ethical issues addressed in the process are also explored to ensure the completion of the project.

#### 3.2 Flowchart Methodology

This section describes the methodology used during the development of this project. The process throughout the project will be discussed as below and referring to Figure 3.1.

#### 1. Background study

- Study the concept and fundamental of WPT and CPT system based from published journal and relevant sources.

- Identify the limitation of CPT

- 2. Calculation and design of Class D inverter circuit

- Develop calculation to obtain the value of components.

- Compare the result with the theoretical of ZVS.

- 3. Components selection and simulation

- Develop the Class D inverter simulation by using MATLAB software.

- Combine the Class D inverter circuit with impedance matching network.

- Identify the output, efficiency and ZVS with theoretical.

- Combine the Class D inverter with CLL impedance with rectifier circuit.

- 4. Develop microcontroller to control the PWM for the inverter circuit

- Microcontroller use to ensure the smoothness of switching among the switching devices without any overlapping.

- To provide the duty cycle as stated in project scope

- 5. Design Class D inverter with rectifier circuit.

- Test the simulation for rectifier with the Class D inverter CLL topology.

- Check the P<sub>out</sub>, P<sub>in</sub>, η and ZVS condition with theoretical.

- 6. Performance of the evaluation with theoretical part

- Develop Class D inverter with LCCL impedance.

- Compare the result between CLL and LCCL impedance matching network to analyze the ZVS condition, input power and output power towards load and distance variation.

Figure 3.1: Flowchart for methodology

#### 3.3 CPT System Circuit Configuration

In this project, three main parts of the circuit operate the purpose of developing the CPT system. Those three circuits are Class D inverter, impedance matching network configuration and rectifier configuration. Besides, those configurations are meant to fulfil the objectives, as stated in chapter one.

#### 3.3.1 Coding for controlling the PWM

PWM operates by pulsing DC and changing the amount of time each pulse stays 'on' to monitor the amount of current flowing through a system. PWM is physical, meaning it has two states; on and off (which corresponds to 1 and 0 in the binary sense, being precise to describe in microcontrollers.) In this project, Arduino UNO software has been chosen to be the medium in controlling the PWM. The main reason PWM circuits are so efficient is that they do not attempt to use resistance to partially restrict current flow. [30] They turn the current on and off. Then they only vary the amount of time it's going.

Figure 3.2: Arduino UNO software

The squares in the PWM diagram below are the pulses representing 'on' time, and the depressed areas reflect the 'off' time of the control. The squares and the distressed areas are the same 'width', which means that the duty cycle is 50%. Typically, PWM signals are square waves, as in the picture below.

Figure 3.3: A PWM signal (square wave) with a 50% duty cycle

If the duty cycle were 0%, as seen below, the entire signal would be flat. A 0% PWM duty cycle means that the power is eliminated. An LED would not be operational in such a state and this always would be off.

Figure 3.4: PWM signal (square wave) with a 0% duty cycle

PWM circuit usually require a very low, and a large, power source to break things down further. With the help of power transistors, the tiny power source controls the big one. The tiny one produces the signal, and the aforementioned transistors control the 'heat' which is the large current and voltage which heat on the LED. That tiny power source could be a GPIO microcontroller pin like an Arduino I/O pin, the output pin for a 555 timer, among others.

Establishing the duty cycle signal to 30% will also contribute in a duty cycle of 30% for the power, as the large current is only a modulated replica of the tiny current (which is the signal). This principle enables extremely developed microcontrollers (often called MCUs) and other computers to control, at a reasonable cost, very large currents. The signal is produced by the microcontroller/MCU, the signal then controls a power transistor.

#### 3.3.2 Class D inverter configuration

The flowchart of Class D inverter in Figure 3.5 is used to represent the analysis of achieving the following expectations:

- The zero-voltage switching (ZVS) condition was to determine the on and off state of MOSFET sequentially.

- ii. The output waveform of Class D inverter is obligatory in a square wave waveform.

- iii. The peak amplitude should be the same as the input value of Vdc.

- iv. Considering the ideal switches condition for this configuration.

#### 3.3.3 Impedance Matching Configuration

In the transmitter part where the dc signal needs to be converted to ac signal, the impedance matching of CLL topology is used as the resonance configuration. First, throughout the Class D circuit, the output is still in a digital form. Hence, the use of the impedance matching configuration is to develop the digital way to resonance form.

Figure 3.6: Class D inverter with CLL impedance matching schematic

In this part, it is required to perform the mathematical approach first to obtain the value for components, current and voltage, power and efficiency. All parameters are calculated based on the theory. [19]

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

i. Maximum DC input power

$$P_{\text{IMAX}} = \frac{Primax}{\eta} \tag{3.1}$$

ii. Maximum value DC input current

$$I_{\text{IMAX}} = \frac{Pimax}{Vin} \tag{3.2}$$

iii. Value of components

$$C = \frac{Ql}{\omega_{\circ}Rimin} \tag{3.3}$$

$$L = \frac{Rimin}{\omega_{o}Ql} \tag{3.4}$$

$$L_1 = L_2 = \frac{L}{1 + \frac{1}{A}} \tag{3.5}$$

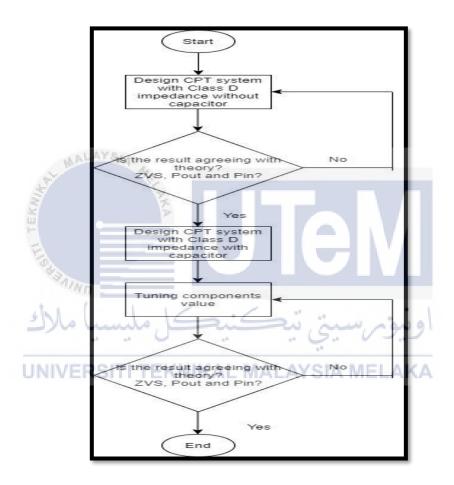

In this part also, an analysis has been developed in order to fulfil objective 2 and objective 3. The comparison of impedance matching network has been performed by comparing two difference topology which are CLL impedance and LCCL impedance with the same Class D inverter. Those two topology has been analyzed towards the efficiency performance against the load variation and distance variation.

For (objective 2), the analysis towards the ZVS condition where the waveform of Vds and Ids for both topology had been observed in order to notice the overlapping existence between Vds and Ids. Thus, this condition will affected the power input and power output performance where the overlapping will causes the power losses.

Then, for (objective 3), a range of load variation and distance variation has been setup to analyze the performance of efficiency towards both parameter. Also, the analysis can be observed through the Vds and Ids waveform where it represent the input power of the CPT system and also the output power where the performance has been analyzed through the load resistor.

#### 3.3.4 Rectifier Configuration

In the CPT method, the receiver circuit needed to monitor the phase of transferring the signal from ac to dc. Figure 3.7 shows the receiver circuit flowchart, which consists of the rectifier. Hence, the Class D implemented in this project will quickly attain voltage from ac to dc.

So that an ideal rectifier is used in this project, power can only be used in a particular voltage step. Due to this issue, the ideal diode has been used in this project

since the component selection in MATLAB software only provided ideal diode components.

Alternatively, after the result has been obtained by tuning the circuit, tabulate the table of comparative value between theoretical and simulation. Last but not least, to proceed with the next step, the outcome as a theoretical one must have perfect ZVS.

Figure 3.7: Flowchart of rectifier

By completing the full CPT system by using Class D inverter with CLL impedance and LCCL impedance, the comparison and analysis can be made in order to justify the capability of topology to enhance the system efficiency. (Objective 1)

#### 3.4 Implementation

This section introduces the low power application to achieve high value for performance. The constant parameter in this project are the duty cycle which is 50%,  $V_{DC}=24V \text{ and efficiency} \geq 85\%.$

The IRFZ44 MOSFET was chosen to be used in this project based from the criteria that fulfil the requirement of operating in fast switching mode and higher input value for  $V_{DS}$ . Besides, the advantage of this MOSFET is capable of producing without using a driver circuit. Next, the software used to develop the PWM is Arduino UNO. The pulse that generates by the PWM is essential to clarify the duty cycle was achieved.

Next, as stated in the previous chapter, the value for coupling capacitance must be precise to achieve the desired efficiency.

Figure 3.8: Picture of CPT system for purposes of low power application

#### **CHAPTER 4**

#### **RESULTS AND DISCUSSION**

This segment addressed and explained the research result at the initial stage of study based on the research questions highlighted. The research outcome describes the study results in terms of statistics and in written language. Graphical illustrations, table and diagram define the most crucial aspects of the result.

### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### 4.1 Introduction

Based on researches and experimental that has been done during the PSM 1 and PSM 2, the results are about to be explained in this chapter. Referred to the objective that has been mentioned in the earlier section, this system is estimated to transfer power wirelessly with an amount of 10Watt and suits for any low power application devices.

This CPT system started with developing the simulation of configuration by using MATLAB software where all the results and waveform are included in this chapter. Besides, the comparison between theoretical and simulation are also has been tabulated precisely.

Table 4.1: Calculation for Class D inverter parameter

|                                                                                                                                                                                                                                                            | Value   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| a) Maximum DC input power                                                                                                                                                                                                                                  | 11.76W  |

| $P_{\text{IMAX}} = \frac{PRimax}{\eta}$                                                                                                                                                                                                                    |         |

| b) Maximum value DC input current                                                                                                                                                                                                                          | 0.49A   |

| $I_{IMAX} = \frac{PImax}{Vin}$                                                                                                                                                                                                                             |         |

| c) Quality Factor, Q <sub>L</sub>                                                                                                                                                                                                                          | 0.707   |

| $Q_L = \frac{1}{\sqrt{2}}$                                                                                                                                                                                                                                 |         |

| d) Capacitance, C $C = \frac{QL}{\omega_{0} RImin}$                                                                                                                                                                                                        | 750pF   |

| e) Inductance, L $L = \frac{RImin}{\omega o \ QL}$                                                                                                                                                                                                         | 33.77uH |

| f) Inductance $L_1$ and $L_2$ $L_1 = \frac{L}{1 + \frac{1}{A}}$ $UL_2 = \frac{ERSITI}{1 + A}$ UNIVERSITY TEKNIKAL MALAYSIA MELAKA                                                                                                                          | 17uH    |

| g) Impedance, Z <sub>o</sub>                                                                                                                                                                                                                               | 212.16Ω |

| $Z_0 = \frac{RImin}{QL}$                                                                                                                                                                                                                                   |         |

| h) Amplitude of the fundamental component of the voltage at the                                                                                                                                                                                            | 30.56V  |

| input resonant circuit.                                                                                                                                                                                                                                    |         |

| $V_{\mathrm{M}} = \frac{4}{\pi} (vi)$                                                                                                                                                                                                                      |         |

| i) RMS value of V <sub>i</sub>                                                                                                                                                                                                                             | 21.61V  |

| $V_{\rm rms} = \frac{v_m}{\sqrt{2}}$                                                                                                                                                                                                                       |         |

| j) Voltage transfer function from V <sub>i</sub>                                                                                                                                                                                                           | 0.9     |

| $\mathbf{M}_{\mathrm{VS}} \equiv \frac{vrms}{vi}$                                                                                                                                                                                                          |         |

| k) Magnitude of the DC-to-AC voltage transfer function                                                                                                                                                                                                     | 1.27    |

| $\mathbf{M}_{\mathrm{V1}} \equiv \frac{VRi}{Vi} = \frac{2\sqrt{2}}{\pi \sqrt{(1+A)^2 \left(1 - \left(\frac{\omega o}{\omega}\right)^2\right)^2 + \left(\frac{1}{QL}\left(\frac{\omega}{\omega o}\frac{A}{A+1} - \frac{\omega o}{\omega}\right)\right)^2}}$ |         |

|                                                                                                                                                                                                                                                            |         |

| 1)  M <sub>VR</sub>   = 1                                                                                                                                                                                                                                                                               | 1.414           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| l) $ \mathbf{M}_{\mathrm{VR}}  = \frac{1}{\sqrt{(1+A)^2 \left[1 - \left(\frac{\omega o}{\omega}\right)^2\right]^2 + \frac{1}{QL^2} \left(\frac{\omega}{\omega o}\right) \left(\frac{A}{A+1}\right) - \left(\frac{\omega o}{\omega}\right)^2}}$                                                          |                 |

| $\sqrt{[(\omega)]} QL^2(\omega b) (A+1) (\omega)$                                                                                                                                                                                                                                                       |                 |

| m) Current through capacitor, I <sub>m</sub>                                                                                                                                                                                                                                                            | 498.85mA        |

|                                                                                                                                                                                                                                                                                                         | 1,50,002,1111,1 |

| $I_{M} = \frac{4 Vi}{1 + \left[QL\left(\frac{\omega o}{\omega}\right)(1+A)\right]^{2}}$                                                                                                                                                                                                                 |                 |

| $I_{M} = \frac{4 Vi}{\pi Zo QL} \sqrt{\frac{1 + \left[QL\left(\frac{\omega o}{\omega}\right)(1+A)\right]^{2}}{\left(1+A\right)^{2} \left[1 - \left(\frac{\omega o}{\omega}\right)^{2}\right]^{2} + \frac{1}{QL^{2}} \left(\frac{\omega}{\omega o} \frac{A}{A+1} - \frac{\omega o}{\omega}\right)^{2}}}$ |                 |

| n) Amplitude of output current of Class D inverter                                                                                                                                                                                                                                                      | 288.04mA        |

| $I_{OM} = \frac{4 Vi}{}$                                                                                                                                                                                                                                                                                |                 |

| $\pi Zo QL \sqrt{(1+A)^2 \left[1 - \left(\frac{\omega o}{\omega}\right)^2\right]^2 + \left[\frac{1}{QL} \left(\frac{\omega}{\omega o} \frac{A}{A+1} - \frac{\omega}{\omega o}\right)\right]^2}$                                                                                                         |                 |

| o) Voltage across capacitor, V <sub>CM</sub>                                                                                                                                                                                                                                                            | 105.85V         |

| $V_{CM} = \left(\frac{\omega o}{\omega}\right) \left(\frac{4 \text{ Vi }  Mvr }{\pi O I}\right) \sqrt{1 + \left[QL\left(\frac{\omega o}{\omega}\right)(1 + A)\right]^2}$                                                                                                                                |                 |

| $\left[\begin{array}{cccc} & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ \end{array}\right] $                                                                                                                                                                                                 |                 |

| p) Voltage across inductor L <sub>1</sub> , V <sub>L1</sub>                                                                                                                                                                                                                                             | 52.87V          |

|                                                                                                                                                                                                                                                                                                         | 02.07           |

| $V_{L1} = \left(\frac{\omega}{\omega o}\right) \left(\frac{A}{1+A}\right) \left(\frac{4 \ Vi \  Mvr }{\pi \ QL}\right) \sqrt{1 + \left[QL\left(\frac{\omega o}{\omega}\right) (1+A)\right]^2}$                                                                                                          |                 |

| q) Voltage across inductor L2, $V_{L2} = V_0$ of the inverter                                                                                                                                                                                                                                           | 43.11V          |

| $V_{L2} = (\sqrt{2}) (M_{V1}) (Vi)$                                                                                                                                                                                                                                                                     |                 |

| r) Power output, P <sub>Ri</sub>                                                                                                                                                                                                                                                                        | 10.73W          |

| $P_{Ri} = \frac{8Vt^2}{(1 + t^2)^2 (1 + (w + v^2)^2)}$                                                                                                                                                                                                                                                  |                 |

| $P_{Ri} = \frac{8Vi^2}{\pi^2 Zo \ QL \left\{ (1+A)^2 \left[ 1 - \left( \frac{\omega o}{\omega} \right)^2 \right]^2 + \frac{1}{QL^2} \left( \frac{\omega}{\omega o} \frac{A}{A+1} - \frac{\omega o}{\omega} \right)^2 \right\}}$                                                                         |                 |

|                                                                                                                                                                                                                                                                                                         |                 |

| s) Total parasitic resistance of the inverter SIA MELAKA                                                                                                                                                                                                                                                | Assume          |

| , · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                 | ideal           |

| $r = 2_{rds} +_{rcr} +_{rL1} + \frac{rL2}{1 + \left(\frac{\omega L2}{Ri}\right)^2}$                                                                                                                                                                                                                     |                 |

| t) The conduction loss                                                                                                                                                                                                                                                                                  | Assume          |

| $Pr = \frac{rIm^2}{2}$                                                                                                                                                                                                                                                                                  | ideal           |

|                                                                                                                                                                                                                                                                                                         |                 |

| u) Efficiency, η                                                                                                                                                                                                                                                                                        | 91.23%          |

| $\eta = \frac{Pri}{Pi}$                                                                                                                                                                                                                                                                                 |                 |

|                                                                                                                                                                                                                                                                                                         |                 |

Based from the above equation in the table [19], it can be assume that the MOSFET used are in ideal condition since this project only require a simulation topology. Nevertheless, if the project is going to be implement for hardware part, the internal resistance need to be considered since each MOSFET has own characteristics.

#### 4.2 Simulation Result

The results based from the simulation performs are highlighted in this chapter.

The simulation part consists of three main parts which are Class D inverter, impedance matching network and rectifier.

#### **4.2.1 PWM Controls Signal Using Arduino**

In this project, as mentioned earlier in Chapter 1, a 50% duty cycle is used to control the signal from power to be in 'on' and 'off' state respectively. A 50% of duty cycle seems to be a perfect value for the signal to switching smoothly in an equally mode. The signal was tested by using Proteus software where the software is able to provide an oscilloscope with Arduino libraries included.

It is necessary to concern the rise time and fall time of the significant MOSFET used to avoid overlap occurrence between rising and falling signal. All the fundamental features can be access through the datasheet provided by the manufacturer.

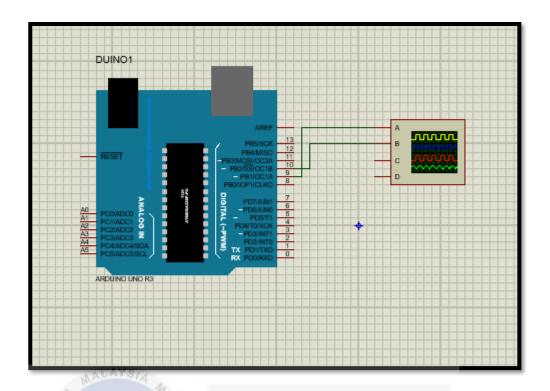

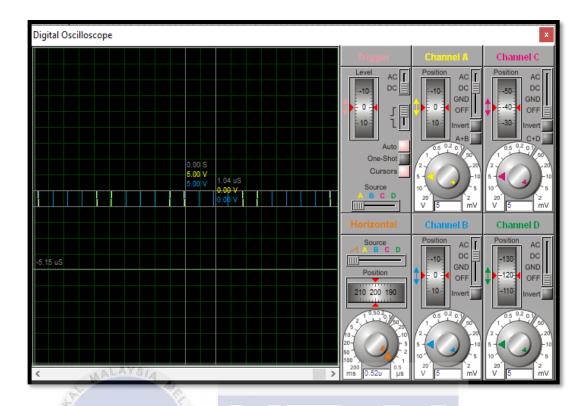

**Figure 4.1: Simulation PWM connection (Proteus Software)**

Referred to above diagram, Arduino UNO R3 was chose as the microcontroller based on the features and capability. Meanwhile, pin 9 and pin 10 had been chosen as the output pin from the Arduino. The output had been measured by the oscilloscope at Channel A and Channel B.

Figure 4.2: PWM waveform (inverted signal)

Based from the output waveform, it determine that the PWM is providing a 5V input to the gate terminal of MOSFET. The input voltage is switching repeatedly in the control of the duty cycle set. In this project, for one complete cycle, it takes around 1 microseconds while there are positive and negative state in that period. During the positive cycle, the PWM will provide 5V and 0V during the negative cycle.

In this PWM system, there are two signals provided intervening each other. It is use to invert the signal for each pair of MOSFET contained in the Class D inverter. In other hands, it is compulsory to position both the output signal at ground level to ensure the amplitude are same and no overlapping occurrence between signal.

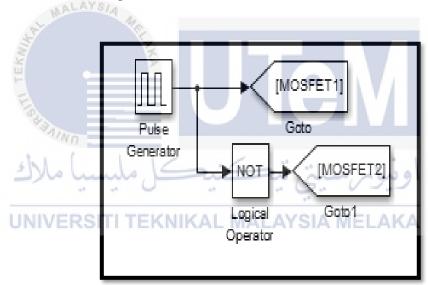

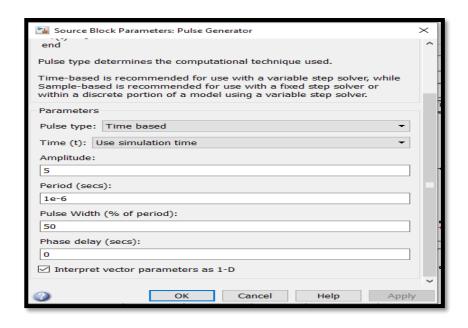

#### **4.2.3 PWM Control Signal Using MATLAB**