# MULTILEVEL INVERTERS WITH FEEDBACK CONTROLLER

# NABILAH ATIKAH BINTI ABDUL RAHIM

2021

### MULTILEVEL INVERTERS WITH FEEDBACK CONTROLLER

## NABILAH ATIKAH BINTI ABDUL RAHIM

A report submitted in partial fulfilment of the requirements for the degree of Bachelor of Electrical Engineering with Honours

## UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2021

### DECLARATION

I declare that this thesis entitled "MULTILEVEL INVERTERS WITH FEEDBACK CONTROLLER is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | Star MALAYSIA MEL                   |  |

|-----------|-------------------------------------|--|

| Name      | : Nabilah Atikah Binti Abdul Rahim  |  |

| Date      | : 30 June 2021                      |  |

|           | اونيومرسيتي تيكنيكل مليسيا ملاك     |  |

|           | UNIVERSITI TEKNIKAL MALAYSIA MELAKA |  |

## APPROVAL

I hereby declare that I have checked this report entitled Multilevel Inverter with Feedback and in my opinion, this thesis it complies the partial fulfillment for awarding the award of the degree of Bachelor of Electrical Engineering with Honours

| Signature      | :                                 |

|----------------|-----------------------------------|

| Supervisor Nam | ne:<br>Azvita 67 Alics            |

| Date           | :<br>5772021                      |

| SITI TEKNING   | UTEM                              |

| الح            | اونيۆم سيتي تيكنيكل مليسيا ملا    |

| UN             | IVERSITI TEKNIKAL MALAYSIA MELAKA |

## **DEDICATIONS**

To my beloved mother and father

#### ACKNOWLEDGEMENTS

In preparing this report, I was in contact with many people which is my parents, siblings and my supervisor. They have contributed towards my understanding and thought. I wish to express my sincere appreciation to my main project supervisor, Dr.Azrita Binti Alias for motivation, guidance critics and advice. This project would not have been the same as the one mentioned here without their continued support and involvement.

My fellow classmates should also be recognized for their support. My sincere appreciation also extends to all my friends and others who have offer me many thoughts and opinions on my project. Their views and tips are useful indeed. Unfortunately, it is not possible to list all of them in this limited space. I am grateful to all my family members.

I praise Allah the Supreme Creator above all else, for granting me everything necessary to complete this mission.

TEKNIKAL MALAYSIA MELAKA

UNIVERSITI

#### ABSTRACT

The use of multi-level inverters has become important in recent days, particularly at high-strom sites. The benefits in the modularity, failure control, stability and waveform with a less harmonic output distortion received greater interest from the multi-level inverter in the current industry. In this paper the topology of the inverter at 3, 5 and 7 stages has been studied. The proposed topology took into account considerations such as minimizing and reducing overall harmonic distortions, increasing the waveform output efficiency and obtaining greater power. In terms of THD and switching confidence, the output efficiency of the proposed topology has been studied and compared to traditional inverters using carrier-based pulsed width modulation techniques. The proposed device has been developed with a single source and a double source inverter. For the proposed topology, the MATLAB simulation generated a sinusoidal waveform.

اونيونر،سيتي تيڪنيڪل مليسيا ملاك

#### ABSTRAK

Sejak kebelakangan ini, "Multilevel Inverter" telah menjadi sesuatu yang keperluan dan juga amat diperlukan terutama sekali dalam bidang kuasa voltan tinggi. Terdapat pelbagai "Multilevel Inverter" antaranya kelebihan modulariti, kegagalan pengurusan, kebolehpercayaan dan bentuk gelombang dengan mengurangkan penyimpangan harmonik pada keluaran yang mendapat perhatian lebih dalam pada industri semasa. Dalam topologi ini adalah pada tahap 3, 5, dan 7 yang telah dianalisis. Topologi yang dicadangkan telah mempertimbangkan faktor-faktor seperti mengurangkan keseluruhan distorsi harmonik dan mengurangkan, meningkatkan kualiti bentuk gelombang output, dan daya yang lebih tinggi diperoleh. Kualiti prestasi topologi yang dicadangkan telah dianalisis dari segi THD dan beralih kepercayaan dan dibandingkan dengan penyongsang konvensional yang ada menggunakan teknik modulasi lebar berdasarkan pembawa. Dicadangkan telah dikembangkan menggunakan unit penyongsang sumber tunggal dan sumber berganda. Simulasi MATLAB telah dilakukan untuk topologi yang dicadangkan dan bentuk gelombang keluaran yang telah dihasilkan.

UNIVERSIT TEKNIKAL MALAYSIA MELAKA

## TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                   | PAGE                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| DECLARATION                                                                                                                                                                                                                                                                       |                                     |

| APPROVAL                                                                                                                                                                                                                                                                          |                                     |

| DEDICATIONS                                                                                                                                                                                                                                                                       |                                     |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                  |                                     |

| ABSTRACT i                                                                                                                                                                                                                                                                        |                                     |

| ABSTRAK ii                                                                                                                                                                                                                                                                        |                                     |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                 | iii                                 |

| LIST OF TABLES v                                                                                                                                                                                                                                                                  |                                     |

| LIST OF FIGURES vi                                                                                                                                                                                                                                                                |                                     |

| CHAPTER 1INTRODUCTION1.1Introduction1.2Motivation1.3Problem Statement1.4Objective1.5Scope                                                                                                                                                                                         | <b>1</b><br>1-2<br>3<br>4<br>5<br>5 |

| CHAPTER 2 LITERATURE REVIEW                                                                                                                                                                                                                                                       |                                     |

| <ul> <li>2.1 Introduction</li> <li>2.2 Inverter and Multilevel Inverter</li> <li>2.2.1 Diode Clamp Multilevel Inverter</li> <li>2.2.2 Flying Capacitor Multilevel Inverter</li> <li>2.2.3 Cascaded H-Bridge Multilevel Inverter (CHMI)</li> </ul>                                 | 6<br>6-7<br>7<br>8<br>9-10          |

| <ul> <li>2.3 The Sinusoidal Pulse Width Modulation (SPWM)</li> <li>2.3.1 The SPWM for Multilevel Inverter</li> <li>2.3.2 Types of SPWM Techniques</li> </ul>                                                                                                                      | 10-11<br>11<br>12                   |

| <ul> <li>2.3.2 Types of SF with Techniques</li> <li>2.4 The Total Harmonic Distortion</li> <li>2.5 Feedback Control</li> <li>2.5.1 Proportional Integral Derivative Controller (PID)</li> <li>2.5.2 Advantages and Disadvantages of PID controller</li> </ul>                     | 12<br>12<br>13<br>14<br>15          |

| 2.6 Summary                                                                                                                                                                                                                                                                       | 15                                  |

| CHAPTER 3 METHODOLOGY                                                                                                                                                                                                                                                             | 16                                  |

| <ul> <li>3.1 Introduction</li> <li>3.2 Project Procedure</li> <li>3.3 The Implementation of the Open-Loop System</li> <li>3.4 The Basic Working Principle of the Cascaded H Bridge Multilevel Invert</li> <li>3.5 3-Level Cascaded H-Bridge Multilevel Inverter Design</li> </ul> | 16<br>17<br>18<br>ter 19-20         |

# PAGE

| <ul><li>(MATLAB- SIMULINK)</li><li>3.6 Phase 5-Level Cascaded H-Bridge Multilevel Inverter Design</li></ul> |                                | 20                                                                   |       |

|-------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|-------|

|                                                                                                             | (MATLAB-SIMULINK)              |                                                                      |       |

| 3.7                                                                                                         |                                | Level Cascaded H-Bridge Multilevel Inverter Design (MATLAB-          | 21    |

| SIMUI                                                                                                       |                                |                                                                      | 22    |

| 3.8                                                                                                         | ,                              | plementation of the Closed-Loop System                               | 23    |

| 3.9                                                                                                         | Designing of K Gain Controller |                                                                      | 24    |

| 3.10                                                                                                        | 8 8                            |                                                                      |       |

| СНАР                                                                                                        | TER 4                          | RESULTS AND DISCUSSIONS                                              | 29    |

| 4.1                                                                                                         | Introdu                        |                                                                      | 29    |

| 4.2                                                                                                         |                                | mulation Result                                                      | 29    |

|                                                                                                             | 4.2.1                          | The 3-Level CHMI Without Low Pass Filter                             | 30    |

|                                                                                                             | 4.2.2                          | The 3-Level CHMI With Low Pass Filter                                | 31    |

|                                                                                                             | 4.2.3                          | The Range of Modulation Index for the 3-Level Multilevel Inverter    | 32-33 |

|                                                                                                             | 4.2.4                          | The Modulation Index and Effect on Total Harmonic Distortion for the |       |

|                                                                                                             |                                | 3-Level Multilevel Inverter                                          | 34    |

|                                                                                                             | 4.2.5                          | 3-Phase 5-Level CHMI Without Low Pass Filter                         | 34    |

|                                                                                                             | 4.2.6                          | The 3-Phase 5-Level CHMI With Low Pass Filter                        | 36    |

|                                                                                                             | 4.2.7                          | The Range of Modulation Index for the 5-level Multilevel Inverter    | 37    |

|                                                                                                             | 4.2.8                          | The Modulation Index and Effect on Total Harmonic Distortion for the | 5     |

|                                                                                                             |                                | Level Multilevel Inverter                                            | 38    |

|                                                                                                             | 4.2.9                          | The 7-Level CHMI                                                     | 39    |

|                                                                                                             | 4.2.10                         | Closed-loop simple k gain controller                                 | 40-42 |

|                                                                                                             | 4.2.11                         | Closed-loop simple PID controller                                    | 43-45 |

|                                                                                                             |                                | Malunda Kai Gi in maint                                              |       |

| СНАР                                                                                                        | TER 5                          | CONCLUSION AND RECOMMENDATIONS                                       | 46    |

| 5.1                                                                                                         | Conclu                         | SION<br>UNIVERSITI TEKNIKAL MALAYSIA MELAKA                          | 46    |

| REFE                                                                                                        | RENCI                          | ES                                                                   | 47-48 |

## LIST OF TABLES

| Table 3.1 : | The Voltage level and Switch Control for 5 Level CHMI                                                                       | 19 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2 : | Table 3.2: The Gantt Chart                                                                                                  | 20 |

| Table 4.1 : | The Modulation Index and The Correlating Total Harmonic Distortion                                                          | 25 |

| Table 4.2 : | The Modulation Index and The Correlating Total Harmonic Distortion                                                          | 29 |

| Table 4.3:  | The Output Voltage and The Correlating Total Harmonic<br>Distortion with The Same Resistance and Different Input<br>Voltage | 40 |

| Table 4.4 : | The Output Voltage and The Correlating Total Harmonic<br>Distortion with The Different Resistance and Same Input<br>Voltage | 41 |

| Table 4.5 : | The Output Voltage and The Correlating Total Harmonic<br>Distortion with The Same Resistance and Different Input<br>Voltage | 43 |

| Table 4.6 : | The Output Voltage and The Correlating Total Harmonic<br>Distortion with The Different Resistance and Same Input<br>Voltage | 43 |

|             | UNIVERSITI TEKNIKAL MALAYSIA MELAKA                                                                                         |    |

## LIST OF FIGURES

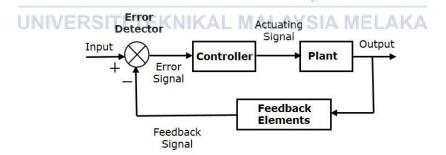

| Figure 1.1 :   | The Closed Loop Control System                                                                 | 2  |

|----------------|------------------------------------------------------------------------------------------------|----|

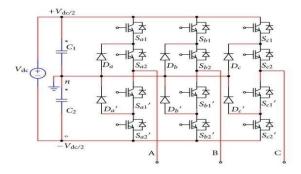

| Figure 2.1 :   | 3-Level Topology of Diode-Clamped Inverter                                                     | 7  |

| Figure 2.2 :   | 3-Phase 5-Level Topology of Flying Capacitor Multilevel<br>Inverter                            | 8  |

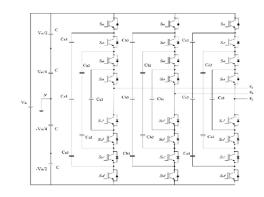

| Figure 2.4 :   | The 5-Level Topology of H-Bridge Multilevel Inverter                                           | 10 |

| Figure 2.5 :   | The Feedback System                                                                            | 13 |

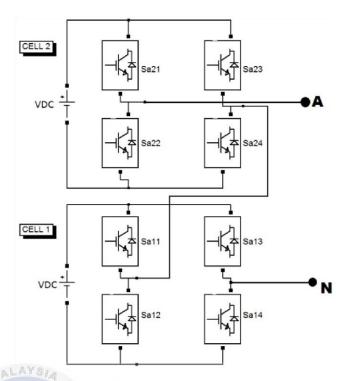

| Figure 3.1 :   | Single phase three level CHMI                                                                  | 19 |

| Figure 3.2 :   | Single phase five level CHMI                                                                   | 19 |

| Figure 3.3 :   | Staircase voltage waveform for single phase                                                    | 20 |

| Figure 3.4 :   | 3-level Cascaded H-Bridge Multilevel Inverter Design                                           | 20 |

| Figure 3.5 :   | 3 Phase 5-level Cascaded H-Bridge Multilevel Inverter                                          | 21 |

|                | Design                                                                                         |    |

| Figure 3.6:    | The 3-phase 7-level Cascaded H-Bridge Multilevel<br>Inverter Design                            | 22 |

| Figure 3.7:    | Project Flow with Feedback Controller                                                          | 23 |

| Figure 3.8:    | The 3-phase 7-level Cascaded H-Bridge Multilevel                                               | 24 |

| 1 19010 0101   | Inverter Design with K Gain Controller System                                                  | 2. |

| Figure 3.9:    | PID Block Diagram                                                                              | 25 |

| Figure 3.10:   | The PID Equivalent Block Diagram                                                               | 25 |

| Figure 3.11:   | The PID Control System                                                                         | 26 |

| Figure 3.12: — | The Circuit for 3-Phase 7-Level CHMI with PID Controller<br>System STITEKNIKAL MALAYSIA MELAKA | 27 |

| Figure 4.1 :   | The Output Voltage of 3-Level Without Low Pass Filter                                          | 30 |

| Figure 4.2 :   | The THD Value for the 3-Level Without Low Pass Filter                                          | 30 |

| Figure 4.3 :   | The Output Voltage for the 3-Level With Low Pass Filter                                        | 31 |

| Figure 4.4 :   | The THD value for the 3-Level With Low Pass Filter                                             | 31 |

| Figure 4.5 :   | The THD value for 3-level CHMI with the modulation index $= 0.80$                              | 32 |

| Figure 4.6 :   | The Output Voltage for 3-level CHMI for Modulation Index = 0.80                                | 32 |

| Figure 4.7 :   | The THD value for 3-level CHMI with the Modulation Index $= 0.60$                              | 33 |

| Figure 4.8 :   | The Output Voltage for 3-level CHMI for Modulation Index = 0.60                                | 33 |

| Figure 4.9 :   | The Output Voltage of 5-Level Without Low Pass Filter                                          | 34 |

| Figure 4.10 :  | The THD Value for the 5-Level Without Low Pass Filter                                          | 35 |

| Figure 4.11 :  | Output Voltage with Modulation Index at 0.80                                                   | 36 |

| Figure 4.12 :  | Output Voltage and Current when Modulation Index at 0.80                                       | 36 |

| Figure 4.13 : | The THD value for 5-Level CHMI Value After                 | 37 |

|---------------|------------------------------------------------------------|----|

|               | Implementation of Filter                                   |    |

| Figure 4.14 : | The 3-Phase 5-Level CHMI with Modulation Index $= 1.3$     | 37 |

| Figure 4.15 : | The 3-Phase 5-Level CHMI with Modulation Index $= 0.6$     | 38 |

| Figure 4.16 : | The Output Voltage of 7-Level                              | 39 |

| Figure 4.17 : | The THD value for 7-Level Open Loop                        | 39 |

| Figure 4.18 : | The 3-Phase 7-Level CHMI with Modulation Index, The        | 40 |

|               | Correlating Total Harmonic Distortion and Vrms in Voltage  |    |

|               | phase A                                                    |    |

| Figure 4.19 : | The 3-Phase 7-Level CHMI of the Output Voltage in Voltage  | 40 |

|               | phase A                                                    |    |

| Figure 4.20 : | The Output Voltage of 7-Level with modified PID controller | 43 |

| Figure 4.21 : | The 3-Phase 7-Level CHMI of the Output Voltage in Voltage  | 43 |

|               | phase A                                                    |    |

| Figure 4.22 : | The 3-Phase 7-Level CHMI with Modulation Index, The        | 44 |

| MIL           | Correlating Total Harmonic Distortion and Vrms in Voltage  |    |

| TEK.          | phase A VIII COLORINA                                      |    |

| 5             | اونيۈم سيتي تيڪنيڪل مليسيا ملا                             |    |

|               |                                                            |    |

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Background

Demand for electrical appliances has grown over the years. Technology played an important part in inventing new electrical equipment to satisfy demand. All electronic equipment differs however in terms of power usage, some of which are intended to use alternating current and some to use direct current.

Power converters are the system used for converting direct current to alternate current and vice versa. An inverter is an electric power unit, used to convert direct current (DC) into AC, and rectifiers transform AC into DC that exactly performs the opposite function of the inverter. The inverter is used in applications involving electrical power to be transferred directly from DC to AC or indirectly from AC to AC. For many fields, DC to AC conversion is useful, including harmonic compensation for power conditioning, motor drives and the incorporation of renewable energy grid.

The multi-level inverter has been used as an alternative since 1975 in high and mediumvoltage conditions. The multi-level inverter is similar to an inverter. There are three most widely used multi-level inverter topologies including multilevel inverters for cascading Hbridge, multi-level diode clamps and multi-level inverters for flying condensers. Multi-level inverters have recently been introduced as a very significant element in the application of high power and medium voltage. A variety of inverter topologies were implemented and used for different applications. Multi-level inverters are favoured in the topologies largely because of their efficiency in generating higher voltage from a lower rating driven unit, improved voltage waveform, lower pulse width modulation frequency and reduced overall harmonic distortion (THD). The section control mechanism as a good controller can, however, have a major efficiency impact because the inverter, for example the frequency of switching, minimizes switching errors, is stable and, from a control point of view, has a high transient response.

A closed-loop control system is a series of mechanical or electronic systems that automatically change a variable process to the appropriate status or fixed point without human interaction. Closed-loop control schemes are manually input-needed relative to openloop control systems. A closed-loop control system is a control system that uses the idea of an openloop system as its forward route but provides one or more feedback paths between its output and its inputs. This system is also known as a feedback control system. The relation to "feedback" basically means that part of the output is passed back to the input and is part of the exciting system[1]. In Diagram 1.1 below, the closed-loop control method is presented. Closedloop systems are configured to automatically achieve and sustain the necessary yield situation in addition to the actual state. This is achieved by generating an error signal which distinguishes the output from the input of the reference. In other words, a "closed-loop system" is a fully automatic control system that relies somewhere on the control procedure's feedback. Closed circuit systems have many benefits over open circuit systems. The primary advantage of a locked feedback system is that it decreases the sensitivity of a system to external disturbances

Figure 1.1: The Closed Loop Control System

#### 1.2 Motivation

Multilevel power transfer was first introduced in the 19th century. The basic theory involves the use of a limited number of switches for a minimal amount of supply. Thus, the number of active semiconductor switches to be deployed has expanded. Power conversion in limited voltage phases. The smaller voltage measures lead to a better output waveform power quality and lower voltage tension (dv/dt) and elctromagnetic compatibility problems [2]. New approaches such as the topology of low-switch frequency high-power devices[3] have been recommended. The traditional inverter typically uses the two-level inverter to get a controllable voltage. There are, however, certain disadvantages for two stage inverters that work at high frequencies that switch power losses and limitations. Due to the drawbacks, multi-level inverter increases the number of switches. The multi-step H-bridge inverter uses condensers and switches that require fewer components at each level. One of the benefits of this multilevel inverter is that it requires fewer components than diode-squeezed and flight condenser inverters.

After the reading of some posts, it reveals that with cascaded H-Bridge using SPWM a better performance can be achieved. The benefits of SPWM are low power consumption, greater energy efficiency of up to 90 percent, simple to introduce and monitor, and no variance of temperature and aging that can contribute to drift or decay. The lesser value of THD has been shown and the voltage is higher than most inverters.

The control system is commonly used in all industries and the input system is used every day. The feedback management device is used to efficiently control the operation or plant. In addition, it is exceptionally precise since the controller manipulates the signal until the signal is zero error. It is therefore less vulnerable to nonlinearity and environmental changes, plus the device bandwidth is very high.

#### **1.3 Problem Statement**

In recent decades much research has focussed on discovering alternative green sources of energy in the atmosphere and minimizing the maximum reliance on fossil fuels. The invention of the inversor has provided a greeting solution for the use of this DC as an AC power most widely used by machines and machinery since most renewable energies produce a DC powder. The conventional two-level inverter was used in the early decades because the criterion was not as significant when it was used to supply the inverter.

But it is not easy to connect the single power semiconductor switch (conventional twostage inverter) directly to the medium-voltage grids with quick growth in the industry and the emergence of higher power devices which hit the megawatt-story. However, there has been much interest in the heavy duty industry and high power applications. Therefore, owing to the drawbacks of this traditional two-level inverter, it is preferable to use the Multilevel IR (MLI) that has a range of advantages over the single-level IR, for example minimal harmonic distortion that generates an almost synodic waveform without a filtering circuit. In this project, we are discussing how the feedback controller will overcome the problem by stimulating the Cascaded H-Bridge as a multi-level inverter with SPWM as switching technique for phases 5, 7 and 9. In addition, the output waveform will also be supplied for output voltage, current, power factor and the value of THD.

#### 1.4 Objective

The aims of this project is to design and simulate the 3-level, 5-level and 7-level inverters using modified SPWM strategy and design the feedback controllers. The objective of this project are as follow :

- Design and stimulate the 3-level, 5-level and 7-level inverter using modified SPWM strategy

- Analyze the output waveform quality such as output voltage and current, and THD

- Design the feedback controller and analyze its performance by changing the load and voltage input

- 1.5 Scope

These are the scope of this project:

- Use the Cascaded H-Bridge for 3-level, 5-level and 7-level configuration as multilevel inverter with SPWM switching strategy.

- The software that been used in this project for design purposes:

1. MATLAB Simulink.

- Use a simple K Gain and modified PID controller as a feedback controller.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Introduction

In this chapter, the multi-level inverter will be explained in more detail. The understanding of the final year project portion used in this project will be strengthened by this literature review. Plus, it will also answer the techniques used by sinusoidal pulse width modulation (SPWM) to decrease harmonic load voltage.

#### 2.2 Inverter and Multilevel Inverter

Direct current (DC) may be transformed by an electrical system that is an inverter to alternating current (AC). This inverter is typically used for home emergency backup. In most countries the DC input voltage is normally smaller, while the AC output is equal to either 120 volts or 240 volts according to the country in which the grid supply voltage is given. The inverter's basic functioning involves an oscillator, control circuit, power unit drive circuit, switching equipment and a transformer.

# Including its different advantages, including low voltage tension, low harmonically and

EMI efficiency on power switches, multifunctional inverters have gained a lot of interest in medium voltage and high-performance applications. The multi-level inverter is an inverter and an option in high-power and medium-voltage industrial applications. An electronic power system is a multi-stage inverter that can provide the ideal voltage alternating level at the output with several low DC voltages as a source. The multi-level inverter has three basic topologies: the Cascaded H-Bridge, Diode Clamped and Flying Capacitor multilevel inverter. There are 3 main layers in each topology, consisting of 3, 5 and 9 levels. When it was initially used in a third level inverter, medium voltage levels were considered the neutral point since the NPC inverter essentially doubles the voltage levels of the unit without the need for a direct voltage match. For example, SPWM technology is more common because of its multiple modulation

methods such as PWM, SPWM, SVPWm and MPWM. The SPWM technology is more popular than others because of the following merits[6]. The length of each pulse varies with respect to the frequency of the sinus wave that is determined in the middle. It is suitable for applications MATLAB / SIMULINK.

#### Diode Clamp Multilevel Inverter

This principal principle is planned to supply diodes in separate phases and multi-voltage condenser banks. A diode transfers a slight voltage, which makes most electrical devices more stressful. Half the input DC voltage is the full output voltage. This is the biggest downside of the multi-level clamped inverter diode. Higher power devices have been required in recent years in various industrial applications. A multi-level converter allows the use and achievement of high power ratings of renewable energy sources.

Multi-degree inverter clamps require switches, diodes, and a single condenser for a half-input DC output voltage. The multi-level inverter has distinct benefits: it can produce high voltages and lower dv/dt, draw current with very little distortions, generate low frequency voltages, minimize engine lock tension and lower speeds. The multilevel clamped diode inverter is also called the Neutral Point Clamped inverter [6]. This topology is largely weak due to the unequal distribution of voltage between connected condensers[8][12]. For higher output levels, too, many diodes are needed. This design is, however, limited to three levels of problems with condenser balance. You can solve this problem by using a 2-time voltage source or by cascading two multi-tiered diode inverters

Figure 2.1 : 3-Level Topology of Diode-Clamped Inverter [13]

Flying Capacitor Multilevel Inverter

The Meynard and Foch invented the flying condenser multilevel inverter in the mid-1990s[4]. The new modification of multi-level inverters over the time is called this multi-level flying capacitor. The configuration of the multi-level inverter is similar to the diode clamp, but the use of the capacitor in the diode clamping position varies. In comparison, the voltage is higher when the condenser is near to the source, but the load is lower. Moreover, capacitor clamping topology has been a possible candidate for multi-inverter applications, as flying capacitor tension can be controlled even if the voltage level is greater than three by choosing redundant conditions[8].

In general, this multi-level inverter topology is more stable than the others. The topology of flying capacitor involves diodes, capacitor and switching modules. Each branch consists of cells connected together in this inverter, and each cell has a single capacitor and two power switches. Each leg consists of a switching resistor. The N cell inverter has 2n switches and the N+1 voltage is zero.

The Flying Capacitor Multilevel Inverter, on the other hand, has its own benefits for balancing, the Flying Capacitor needs to be redundant in phases. It also has the ability to control reactive and active power flows. Moreover, the harmonic content will decrease in amplitude when the voltage level increases.

Figure 2.2: 3-Phase 5-Level Topology of Flying Capacitor Multilevel Inverter [9]

#### Cascaded H-Bridge Multilevel Inverter (CHMI)

Baker and Bannister[6] explained in the mid-1970s that the inverter could produce multi-level voltage from various DC voltage sources. This cascaded H-bridge can be built with up to two or three H Bridge inverters (CHB). The CHB inverter gained a lot of competition due to the need for medium-voltage high-energy converters. The cascaded H-bridge inverters require less component volume relative to the other two multilevel inverters.

A cascaded H-bridge (CHB) structure can involve two or more Hbridge inverters. The cascaded H-bridge inverter has attracted tremendous interest due to the increased demand for medium-tension high-power inverters. A single DC source or a single DC source may be supplied with a CHB inverter. The multi-level cascaded H-bride inverter requires fewer components in each stage, with capacitor and switches. This topology consists of a set of power cells that can easily be scaled by power. The arrangement of capacitor and switch pairs is called an H-bridge 24 that determines the separate DC voltage output for each H-bridge. The H-bridge cells are normally attached in a cascade on their AC side for low-harmonic distortion and a medium voltage. One of the benefits of this type of multilevel inverter is that compared to flying or clamped diode capacitor inverters, it requires fewer components. The inverter price and weight are smaller than the two converters. Some of the modern switching techniques include soft switching.

#### UNIVERSITI TEKNIKAL MALAYSIA MELAKA

In the case of conventional multiphase inverters, multi-level cascade inverters are used to eliminate the required voluminous transformer. With its modular topology, the Cascaded multi-level inverters attain higher voltage, higher power levels (13.8 kV.30 MVA) and higher performance, amongst the few inverter topologies, such as Neutral Point Clamped (NPC), Cascaded H-Bridge (CHB) and Flighting Capacitors (FCs). This topology is based on a mixture of multiple inverters in one row. The major limitations, on the other hand, are that as the voltage level grows the number of components such as switches increases. Therefore prices and weight are raising.

Figure 2.4 : The 5-Level Topology of H-Bridge Multilevel Inverter [16]

### 2.3 The Sinusoidal Pulse Width Modulation (SPWM)

The Sinusoidal Width Modulation is a pulse modeling method that is used in inverters as well as techniques for decreasing the low-frequency harmonics in the inverter shape. The inverter will produce an AC voltage output from a DC voltage input to reproduce a sinusoidal wave by generating one or more square voltage pulses every half cycle by means of switching circuits. The perfect sinusoidal waveform is referred to as the modulating wave in contrast with a much higher frequency triangular waveform, known as the carrier wave. The resulting drive signals induce a quasi-sin load voltage wave to produce several inverter switches on each halfcycle of various pulsed widths. The beneficial aspects of SPWM are menial changeover errors, reduced output harmonics and quick deployment.

Sinusoidal pulse width modulation is a method for calculating the pulse of control for the development of matrix converter switches. In this article, SWPM attempts to reduce the problem of harmonic distortions by using the concept of pulse width minimization[17]. The inverter switches for the voltage source can be triggered and disabled when needed. Just once in a loop the top switch, a square waveform output, is activated and disabled. A better harmonic profile can be obtained if enabled many times in a cycle[8].

Sinusoidal pulse width modulation (SPWM) has its own advantages: SPWM helps a system to achieve the most accurate performance of 90 percent. Furthermore, the power loss in the switching system reduces. When a switch is triggered and the power is transmitted to the load, there is virtually no voltage drop across the switch. SPWM also has its own drawbacks: it has dramatically intensified switching frequencies which lead to greater stress on connected switching devices and hence to loss of faith on those devices.

#### The SPWM for Multilevel Inverter

The multi-stage inverter technique SPWM comprises relating reference phase voltage signals to a variety of symmetrical level shifted carrier waves of PWM generation. t The level shifted carrier waves were seen to be necessary for a n level inverter compared with the sinusoidal relation. Various multi-carrier strategies to reduce the THD ratios with the triangular carriers have been developed based on the SPWM. Thanks to its ability to produce output voltage with less harmonic distortion, lower dv/dt, less distortion input power, lower standard mode voltage and the ability to operate at a low turning frequency, a multi-level voltage source is favoured over the three-level reversal.

# The method provides more sinusoidal and less THD waveform. The inverter switch,

adjusted by the SPWM system, produces a higher waveform of the output sinusoidal voltage. Selective harmonic exclusion and multi-level SPWM involves multiple carriers. Each independent DC voltage source needs its own carrier for multi-carrier SPWM techniques. The switching from different SPWM and THD carrier techniques analysis by FFT analysis is provided for each switch and the effect can be observed[18].