## **Faculty of Electrical Engineering**

# DESIGN AND DEVELOPMENT OF SINGLE PHASE CASCADED H-BRIDGE MULTI-LEVEL INVERTER

AHMAD FIRDAUS BIN ROSLAN

**Bachelor of Electrical Engineering**

2018

## DESIGN AND DEVELOPMENT OF SINGLE PHASE CASCADED H-BRIDGE MULTILEVEL INVERTER

## AHMAD FIRDAUS BIN ROSLAN

A report submitted in partial fulfillment of the requirements for the degree of Bachelor of Electrical Engineering

**Faculty of Electrical Engineering**

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2018

## **DECLARATION**

I declare that this report entitled "Design and Development of Single Phase Cascaded H-Bridge Multilevel Inverter" is the result of my own research except as cited in the references. The report has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | 1                          |

|-----------|----------------------------|

| Name      | : Ahmad Firdaus Bin Roslan |

| Date      | :                          |

## **APPROVAL**

I hereby declare that I have read through this report entitled "Design and Development of Single Phase Cascaded H-Bridge Multilevel Inverter" and found that it has comply the partial fulfillment for awarding the degree of Bachelor of Electrical Engineering.

| Signature         | ·                               |

|-------------------|---------------------------------|

| Supervisor's Name | e : En.Ahmad Aizan Bin Zulkefle |

| Date              |                                 |

## **DEDICATION**

To my beloved parents for their enduring love, motivation and support

#### **ABSTRACT**

Inverter is a power electronics device which is used to convert Direct Current (DC) into Alternating Current (AC). The conventional inverter that produces two voltage levels are no longer fulfils the requirement of reducing harmonic distortions. Therefore, Multi-Level Inverter (MLI) is implemented to solve the problem of high harmonic distortion. Instead of two levels of output, the MLI are used to produce multiple steps/stages of voltages levels to obtain a smoother and almost sinusoidal waveform. In addition, Multi-Level Inverter is treated as the one who used frequently and mostly in power converter topologies especially in handling high power and medium voltage industries. However, three of the most commonly used multi-level inverters topologies are Cascaded H-bridge Multi-Level Inverters (CHMLI), Diode Clamped Multi-Level Inverters (DCMLI), and Flying Capacitor Multi-Level Inverters (FCMLI). This project proposed a single phase cascaded h-bridge multi-level inverter (CHMLI) topology in which requires lesser number of components and it is easier to control if compared to the other methods. Inverter of different voltage levels (up to 11-Levels) are designed and simulated using MATLAB Simulink. Level Shifted Multi-Carrier PWM control scheme is used to control the operation of power switches for CHMLI in this project. The results are compared in terms of THD. These results are analyzed and discussed at the end of this report. The value of THD is found to be reduced as the number of voltage level of CHMLI increased. Besides, the hardware developing of single phase 5-Levels CHMLI is designed by using IGBTs that controlled by Field-Programmable Gate Array (FPGA) using the same PWM control scheme in simulation. Both the results from simulation and hardware are compared in the end of this project.

## **ABSTRAK**

Inverter adalah peranti elektronik kuasa yang digunakan untuk menukar arus terus (DC) ke dalam arus ulang-alik (AC). Penyongsang konvensional yang menghasilkan dua tahap voltan tidak lagi memenuhi kehendakan pasaran iaitu mengurangkan kekacauan harmonik. Oleh itu, Multi-Level Inverter (MLI) dilahirkan untuk menyelesaikan masalah herotan harmonik tinggi. MLI digunakan untuk menghasilkan arus dalam bentuk tingkatan yang mana gelombangnya lebih serupa dengan arus ulang-alik. Di samping itu, kerap Multi-Level Inverter digunakan dan kebanyakannya dipakaiguna dalam pengendalian kuasa tinggi dan industri voltan sederhana. Walau bagaimanapun, tiga topologi yang terutamanya merupakan Cascaded H-bridge Multi-Level Inverters (CHMLI), Diode Clamped Multi-Level Inverters (DCMLI), dan Flying Capacitor Multi-Level Inverters (FCMLI). Projek ini mencadangkan Cascaded H-Bridge Multi-Level Inverter (CHMLI) topologi satu fasa yang memerlukan bilangan yang komponen yang kecil dan lebih mudah untuk mengawal berbanding dengan kaedah lain. Inverter tahap voltan yang berbeza (sehingga 11-Level) direka dan simulasi dijalankan mengguna MATLAB Simulink. Tahap teranjak skim kawalan Multi-Carrier PWM digunakan untuk mengawal operasi suis kuasa untuk CHMLI dalam projek ini. Keputusan dibandingkan dari segi THD. Keputusan ini dianalisis dan dibincangkan pada akhir laporan ini. Nilai THD didapati semakin berkurang apabila tahap voltan CHMLI meningkat. Bagi kerja perkakasan membangunkan satu fasa 5-Levels CHMLI akan direka dengan menggunakan IGBT yang dikawal oleh Field-Programmable Gate Array (FPGA) menggunakan skim kawalan PWM yang sama dalam simulasi seperti report ini. Perbandingan kedua-dua dapatan daripada simulasi dan perkakasan akan dikonklusikan dalam bahagian tamat projek ini.

## **ACKNOWLEDGEMENTS**

Alhamdulillah, first of all I would like to thank God as finally I was able to finish my Final Year Project. This project had been done with all afford even though I got problems to choose title or idea on my project. Luckily, the problem can be settling down and I was able to adapt properly and wisely.

Then, I would like to take this opportunity to express my sincere acknowledgement to my supervisor En.Ahmad Aizan Bin Zulkefle from the Faculty of Electrical Engineering Universiti Teknikal Malaysia Melaka (UTeM) for his essential supervision, support and encouragement towards the completion of this thesis and always gives me guidance and helped me to get through the difficulties throughout the progress of development of this project.

Finally, thanks to my beloved family and friends that always support and give contributions on ideas and help me during my hard time. Without them, I could not complete this report and project and special thank you to everyone who had been to the crucial parts of realization of this project.

## TABLE OF CONTENTS

| CHAPTER | TITLE                                              | PAGE |

|---------|----------------------------------------------------|------|

|         | ABSTRACT                                           | I    |

|         | ABSTARK                                            | II   |

|         | ACKNOWLEDGEMENTS                                   | III  |

|         | TABLE OF CONTENT                                   | IV   |

|         | LIST OF TABLES                                     | VIII |

|         | LIST OF FIGURES                                    | X    |

|         | LIST OF ABBREVIATIONS                              | XIII |

| 1       | INTRODUCTION                                       |      |

|         | 1.1 Background                                     | 1    |

|         | 1.2 Problem Statement                              | 3    |

|         | <b>1.3</b> Motivation                              | 4    |

|         | <b>1.4</b> Objectives                              | 6    |

|         | <b>1.5</b> Scope                                   | 6    |

|         | 1.6 Conclusion                                     | 7    |

| 2       | LITERATURE REVIEW                                  |      |

|         | 2.1 Introduction                                   | 8    |

|         | 2.2 Multi-Level Inverter Topology                  | 9    |

|         | 2.2.1 Diode-Clamped Multi-Level Inverter (DCMI)    | 10   |

|         | 2.2.2 Flying Capacitor Multi-Level Inverter (FCMI) | 15   |

|         | 2.2.3 Cascaded H-Bridge Multi-Level Inverter       | 18   |

|         | 2.3 Pulse-Width Modulation                         | 20   |

3.4.4 Final Hardware Testing

3.5 Conclusion

58

59

| 4 | RESULTS                                                          |    |

|---|------------------------------------------------------------------|----|

|   | 4.1 Introduction                                                 | 60 |

|   | 4.2 Simulation Results                                           | 60 |

|   | <b>4.2.1</b> Pulse Width Modulation                              | 60 |

|   | <b>4.2.1.1</b> Pulses for 3 Level Inverter                       | 61 |

|   | <b>4.2.1.2</b> Pulses for 5 Level Inverter                       | 62 |

|   | <b>4.2.1.3</b> Pulses for 7 Level Inverter                       | 63 |

|   | <b>4.2.1.4</b> Pulses for 9 Level Inverter                       | 64 |

|   | <b>4.2.1.5</b> Pulses for 11 Level Inverter                      | 65 |

|   | 4.2.2 Simulation of different Level of MLI                       | 66 |

|   | <b>4.2.2.1</b> Simulation of 3-Level Inverter                    | 67 |

|   | <b>4.2.2.2</b> Simulation of 5-Level Inverter                    | 68 |

|   | <b>4.2.2.3</b> Simulation of 7-Level Inverter                    | 70 |

|   | <b>4.2.2.4</b> Simulation of 9-Level Inverter                    | 71 |

|   | <b>4.2.2.5</b> Simulation of 11-Level Inverter                   | 72 |

|   | <b>4.2.2.6</b> Summary of the different MLI level                | 73 |

|   | 4.2.3 Simulation of Various Amplitude Modulation                 | 74 |

|   | Ratio, m <sub>a.</sub>                                           |    |

|   | <b>4.2.3.1</b> Amplitude Modulation Ratio, m <sub>a</sub> =0.95  | 75 |

|   | <b>4.2.3.2</b> Amplitude Modulation Ratio, m <sub>a</sub> =0.75. | 76 |

|   | <b>4.2.3.3</b> Amplitude Modulation Ratio, m <sub>a</sub> =0.5.  | 77 |

|   | <b>4.2.3.4</b> Amplitude Modulation Ratio, m <sub>a</sub> =0.25. | 78 |

|   | 4.2.3.5 Summary of the Amplitude Modulation                      | 79 |

|   | Ratio, ma Simulation.                                            |    |

|   | 4.3 Summary on Preliminary Results                               | 80 |

|   | 4.4 Design and Development of Hardware                           | 80 |

|   | <b>4.4.1</b> Hardware Testing                                    | 81 |

|   | <b>4.4.2</b> 5-Levels Multi-Level Inverter                       | 84 |

|   | 4.5 Comparison of Simulation and Hardware                        | 86 |

**Development Results**

| 5 | CONCLUSION                |    |

|---|---------------------------|----|

|   | <b>5.1</b> Conclusion     | 88 |

|   | <b>5.2</b> Recommendation | 89 |

|   | REFERENCES                | 90 |

|   | APPENDICES                | 94 |

VII

## LIST OF TABLES

| <b>Table</b> | Title                                                 | Page |

|--------------|-------------------------------------------------------|------|

| Table 1.1    | Summary of Problem Statement                          | 4    |

| Table 2.1    | Switching condition of a single phase five-level DCMI | 13   |

| Table 2.2    | Switching state of five-level FCMI                    | 16   |

| Table 2.3    | Switching States of each IGBTs in CHMLI               | 19   |

| Table 3.1    | Gantt Chart for FYP 1                                 | 34   |

| Table 3.2    | Gantt Chart for FYP 2                                 | 35   |

| Table 3.3    | Number of H-Bridges in MLI                            | 35   |

| Table 3.4    | Switching State of Switches of 3-Levels Inverter      | 37   |

| Table 3.5    | Switching State of Switches of 5-Levels Inverter      | 37   |

| Table 3.6    | Switching State of Switches of 7-Levels Inverter      | 38   |

| Table 3.7    | Switching State of Switches of 9-Levels Inverter      | 39   |

| Table 3.8    | Switching State of Switches of 11-Levels Inverter     | 40   |

| Table 3.9    | Minimum & Maximum Amplitude of Carriers (3-Level      | 41   |

|              | Inverter)                                             |      |

| Γable 3.10   | Minimum & Maximum Amplitude of Carriers (5-Level      | 42   |

|              | Inverter)                                             |      |

| Γable 3.11   | Minimum & Maximum Amplitude of Carriers (7-Level      | 42   |

|              | Inverter)                                             |      |

| Table 3.12   | Minimum & Maximum Amplitude of Carriers (9-Level      | 43   |

|              | Inverter)                                             |      |

| Гable 3.13   | Minimum & Maximum Amplitude of Carriers (11-Level     | 44   |

|              | Inverter)                                             |      |

| Γable 3.14   | Parameters for Single Phase CHMLI                     | 48   |

| Γable 3.15   | List of components                                    | 51   |

| Table 4.1 | PWM Parameter                                       | 61 |

|-----------|-----------------------------------------------------|----|

| Table 4.2 | Fixed Parameter for MLI Level Simulation            | 67 |

| Table 4.3 | Total Harmonic Distortion (THD) Content in MLI      | 73 |

| Table 4.4 | Fixed Parameter for Various value of ma Simulation. | 74 |

| Table 4.5 | The THD of MLI for various ma                       | 79 |

| Table 4.6 | Comparison of Simulation and Hardware Development   | 86 |

|           | Results                                             |    |

## LIST OF FIGURES

| Figure      | Title                                                  | Page |

|-------------|--------------------------------------------------------|------|

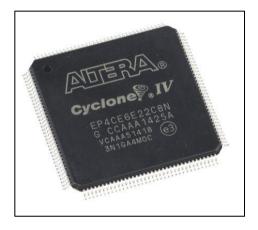

| Figure 1.1  | Altera FPGA Cyclone IV Programmable Chip               | 5    |

| Figure 2.1  | Differences of Waveforms                               | 9    |

| Figure 2.2  | Classification of Multi-Level Inverter                 | 10   |

| Figure 2.3  | Single-Phase 5-level Diode Clamped Inverter            | 11   |

| Figure 2.4  | Example of five-level DCMI output waveform             | 14   |

| Figure 2.5  | Single Phase 5-Level FCMI                              | 15   |

| Figure 2.6  | Single Phase 5-Level Inverter                          | 18   |

| Figure 2.7  | Classification of Modulation Technique                 | 21   |

| Figure 2.8  | PD-PWM                                                 | 24   |

| Figure 2.9  | POD-PWM                                                | 25   |

| Figure 2.10 | APOD-PWM                                               | 25   |

| Figure 2.11 | Optocoupler                                            | 28   |

| Figure 2.12 | Boost Converter                                        | 29   |

| Figure 3.1  | Flow Chart for FYP 1                                   | 32   |

| Figure 3.2  | Flow Chart for FYP 2                                   | 33   |

| Figure 3.3  | Phase disposition (PD) multicarrier PWM for a 3-level  | 41   |

|             | Inverter                                               |      |

| Figure 3.4  | Phase disposition (PD) multicarrier PWM for a 5-level  | 42   |

|             | Inverter                                               |      |

| Figure 3.5  | Phase disposition (PD) multicarrier PWM for a 7-level  | 43   |

|             | Inverter                                               |      |

| Figure 3.6  | Phase disposition (PD) multicarrier PWM for a 9-level  | 44   |

|             | Inverter                                               |      |

| Figure 3.7  | Phase disposition (PD) multicarrier PWM for a 11-level | 45   |

|             | Inverter                                               |      |

| Figure 3.8  | PWM Circuit for 3-Level Inverter                      | 45 |

|-------------|-------------------------------------------------------|----|

| Figure 3.9  | PWM Circuit for 5-Level Inverter                      | 46 |

| Figure 3.10 | PWM Circuit for 7-Level Inverter                      | 46 |

| Figure 3.11 | PWM Circuit for 9-Level Inverter                      | 47 |

| Figure 3.12 | PWM Circuit for 11-Level Inverter                     | 47 |

| Figure 3.13 | 3-Levels Inverter                                     | 48 |

| Figure 3.14 | 5-Levels Inverter                                     | 49 |

| Figure 3.15 | 7-Levels Inverter                                     | 49 |

| Figure 3.16 | 9-Levels Inverter                                     | 50 |

| Figure 3.17 | 11-Levels Inverter                                    | 50 |

| Figure 3.18 | IGBT                                                  | 52 |

| Figure 3.19 | DC-DC Converter (Boost) IQ0515SA                      | 52 |

| Figure 3.20 | Optocoupler HCPL3120                                  | 53 |

| Figure 3.21 | Capacitor                                             | 53 |

| Figure 3.22 | FPGA Cyclone IV DEO-nano Board                        | 54 |

| Figure 3.23 | Connection of Gate Driver                             | 55 |

| Figure 3.24 | Schematic Diagram for Gate Driver (Bottom Connection) | 55 |

| Figure 3.25 | IGBT Cascaded H-Bridge                                | 56 |

| Figure 3.26 | FPGA Output Pulses                                    | 57 |

| Figure 3.27 | Connection for Final Hardware Testing                 | 58 |

| Figure 4.1  | Pulses for 3 Level Inverter (1 H-Bridge)              | 61 |

| Figure 4.2  | Pulses for 5 Level Inverter (2 H-Bridge)              | 62 |

| Figure 4.3  | Pulses for 7 Level Inverter (3 H-Bridge)              | 63 |

| Figure 4.4  | Pulses for 9 Level Inverter (4 H-Bridge)              | 64 |

| Figure 4.5  | Pulses for 11 Level Inverter (5 H-Bridge)             | 66 |

| Figure 4.6  | (a) Output Voltage for 3 Level Inverter, (b) THD      | 68 |

|             | Content in 3 Level Inverter.                          |    |

| Figure 4.7  | (a) Output Voltage for 5 Level Inverter, (b) THD      | 69 |

|             | Content in 5 Level Inverter.                          |    |

| Figure 4.8  | (a) Output Voltage for 7 Level Inverter, (b) THD      | 70 |

|             | Content in 7 Level Inverter.                          |    |

| Figure 4.9  | (a) Output Voltage for 9 Level Inverter, (b) THD               | 71 |

|-------------|----------------------------------------------------------------|----|

|             | Content in 9 Level Inverter.                                   |    |

| Figure 4.10 | (a) Output Voltage for 11 Level Inverter, (b) THD              | 72 |

|             | Content in 11 Level Inverter.                                  |    |

| Figure 4.11 | Relationship of Levels vs %THDv                                | 73 |

| Figure 4.12 | (a) Output Voltage for $m_a$ = 0.95, (b) THD for $m_a$ = 0.95. | 75 |

| Figure 4.13 | (a) Output Voltage for $m_a$ = 0.75, (b) THD for $m_a$ = 0.75. | 76 |

| Figure 4.14 | (a) Output Voltage for $m_a$ = 0.5, (b) THD for $m_a$ = 0.5.   | 77 |

| Figure 4.15 | (a) Output Voltage for $m_a$ = 0.25, (b) THD for $m_a$ = 0.25. | 78 |

| Figure 4.16 | The THDv with Various Value of Amplitude Modulation            | 79 |

|             | Ratio.                                                         |    |

| Figure 4.17 | Fabricated PCB for Gate Driver                                 | 81 |

| Figure 4.18 | Gate Driver                                                    | 81 |

| Figure 4.19 | Compiling Result                                               | 82 |

| Figure 4.20 | Checking for Pulses                                            | 82 |

| Figure 4.21 | Output of Gate Driver Testing with FPGA                        | 83 |

| Figure 4.22 | Output of H-Bridge                                             | 83 |

| Figure 4.23 | 5-Levels Cascaded H-Bridge MLI                                 | 84 |

| Figure 4.24 | Output Voltage Waveform of 5-Levels MLI                        | 84 |

| Figure 4.25 | THD Content in Output Voltage                                  | 85 |

## LIST OF ABBREVIATIONS

DC : Direct Current

AC : Alternating Current

UPS : Uninterruptible Power Supplies

PWM : Pulse Width Modulation

MOSFET : Metal Oxide Semiconductor Field Effect Transistors

IGBT : Integrated Gate Bipolar Transistors

THD : Total Harmonic Distortion

MLI : Multi-Level Inverter

FPGA : Field Programmable Gate Array

CHMLI : Cascaded H-Bridge Multilevel Inverter

PS : Problem Statement

DCMLI : Diode-Clamped Multi-Level Inverter

FCMLI : Flying Capacitor Multi-Level Inverter

NPC : Neutral-Point Clamped

DSTATCOM : Distribution Static Compensator

PD : Phase Disposition

POD : Phase Opposition Disposition

APOD : Alternative Phase Opposition Disposition

DFT : Discrete Fourier Transform

HDL : Hardware Description Language

IC : Integrated Circuit

FFT : Fast Fourier Transform

FYP : Final Year Project

SPWM : Sine Pulse-Width Modulation

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Background

Inverter is an electronic device that converts direct current (DC) into alternating current (AC). Applications such as Uninterruptible Power Supplies (UPS), electric motor speed control, Power Grid, Solar and HVDC Power transmission are embedded with inverter in order to generate AC for their operation. The basic operation of an inverter is by switching on and/or off the transistors with Pulse Width Modulation (PWM) techniques. Transistors such as metal oxide semiconductor field effect transistors (MOSFET), thyristors and as integrated gate bipolar transistors (IGBT) are used for a more efficient output.

Efficiency of an inverter is very important in order to provide sufficient output for the entire system. Therefore, Total Harmonic Distortion (THD) is used to measure the quality of AC signal. The THD in an inverter is determined to prevent undesirable losses, malfunction of appliances hence increasing the efficiency of the inverter. While the conventional two-level inverter used today has drawback, where high harmonic distortions exist in its output [1]. The harmonics content or the quality of an AC signal can be determined in terms of total harmonic distortion (THD).

High level of harmonics can lead to undesirable losses, malfunctions of equipment, and some others critical consequences. To decrease the THD, the number of levels needs to be increased but it requires bulky hardware and it will be harder to control. However, the conventional two-level inverter has some disadvantages and restrictions to produce low THD and higher voltage level. Hence, the concept of multilevel inverter (MLI) has been introduced to overcome the situation since 1975 [12].

Therefore, Multi-level Inverter (MLI) is introduced due to the need of low distortion in the output voltage. Multi-level inverter is the new generation of power converter which complies to the demands of high power and medium voltage applications in the industry [2]. MLI is capable in reducing the Total Harmonic Distortion (THD) content in the generated output waveform. This could be done by implementing multiple level of DC Voltages which then leads to the creation of sinusoidal waveform. In the meantime, substituting most of the distortions in the output. Thus, a higher number of DC levels will result in a lower THD. Nevertheless, this improvement will result in a bulkier product and increases the difficulties in controlling the device.

Generally, the switching techniques that used in a MLI is called as Pulse Width Modulation (PWM). PWM is a modulation technique that used to encode messages into pulses signals to control the switches in a circuit. These pulses will trigger the state of switches either on or off. The switches in an inverter are triggered with PWM pulses to perform effective conversion of voltage and current from DC to AC. The generation of PWM requires a drive to encode the pulses required for the switches. Conventionally, the most popular brand of PWM drive in the market such as Allen Bradley, Altera, and Intel.

#### 1.2 Problem Statement

Conventional inverter has been used since the past decades in the field of industrial applications and power systems of lower power usage. Problems appeared when it comes to high power and medium voltages usage. Conventional inverters are found that no longer fulfill the requirement due to the incapable of reducing harmonic contents. It has high switching losses, lower efficiency and the lifespan of systems due to long term constraining. This lead to the growth of Multi-Level Inverter (MLI), the creation of multiple DC levels that combined into sinusoidal wave with reduced harmonic distortion. MLI topologies are introduced to be functioning under high frequency with lesser switching losses and higher efficiency.

The PWM generation for the pulses that to trigger the switches of inverter are said to be slightly complicated and time consumed to be enhance. The Altera Cyclone IV Field Programmable Gate Array (FPGA) is used due to its programmable advantages. The programmable pulses generation could help to improve the efficiency and ease the repair action.

Therefore, this thesis presents the design and development of single phase Cascaded H-bridge Multilevel Inverter (CHMLI) using FPGA (pulse generator) to produce a sinusoidal output waveform.

Table 1.1: Summary of Problem Statement

| PS  | Problem Statement                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------|

| PS1 | Conventional inverter not capable when it comes to high power and medium voltages usage.                                       |

| PS2 | Conventional inverters are found that no longer full fill the requirement due to the incapable of reducing harmonic contents.  |

| PS3 | Conventional inverters have high switching losses, lower efficiency and the lifespan of systems due to long term constraining. |

#### 1.3 Motivation

With the invention of MLI topologies, it offers great advantages and imparts an alternative for high power applications over a conventional two-level inverter. However, there are few types of MLI topologies and several issues need to be concerned. As for a diode-clamped inverter, it needs voltage balance control and requires excessive amount of clamped diodes when the output voltage level increases which affects the structure of the circuit to become more complex. Similar to diodeclamped inverter, a flying capacitor inverter needs huge amount of capacitors when it has high voltage level and therefore increases the cost.

On the contrary, a h-bridge inverter does not require diodes and capacitors which reduces the complexity and cost of the circuit. On top of that, it solves voltage balancing problem by cascading several h-bridge inverters with separate DC sources [13]. On the other hand, analogue circuit is mostly used in MLI topology as pulse generator and controller for power switches in the circuit.

The micro-controller or field-programmable gate array (FPGA) is an alternative for the topology as it is capable of controlling complicated applications and it allows real-time operations [14]. Consequently, it gives faster response and simplicity in control as comparing to an analogue circuit. A micro-controller or FPGA also provides flexibility in controlling a system in which an analogue circuit does not offer advantage as it is a single purpose-built circuit to serve only single operation [15]. With FPGA, it can change to any controlling method by altering the coding of the program easily and even monitor the process.

As illustrated in Figure 1.1, Field-programmable gate array (FPGA) is an alternative device for pulse generation and controller for power switches in the circuit of a MLI.

Figure 1.1: Altera FPGA Cyclone IV Programmable Chip

Field-programmable gate array (FPGA) is an alternative device for pulse generation and controller for power switches in the circuit of a MLI. FPGA can control complicated applications and allows a real-time operation. FPGA has flexibility in modifying the states or conditions of power switches. Therefore, it can alter the program easily by programming the coding in it and even monitoring the process of device.

## 1.4 Objectives

The objectives of this project are:

- a) To design a single phase cascaded h-bridge multi-level inverter up to eleven levels that provide nearly sinusoidal output voltage using MATLAB Simulink.

- b) To analyze the simulation results of different number of level of Multi-Level Inverter and amplitude modulation in terms of Total Harmonic Distortions (THD).

- c) To develop a Single Phase five Levels Cascaded H-Bridge Multi-Level Inverter circuit using FPGA.

- d) To analyze the hardware result of Single Phase Seven Levels Cascaded H-Bridge Multi-level inverter and compare with the simulation result.

#### 1.5 Scope

The scopes of the project are: -

- a) This project focuses on the design of single phase h-bridge cascaded multilevel inverter up to eleven levels to reduce harmonic content as well as THD.

- b) This multi-level inverter is built and tested with MATLAB Simulink to observe the changes in amplitude modulation with suitable level.

- c) The single phase five levels cascaded h-bridge multi-level inverter will be built using FPGA.

- d) The hardware results of single phase five levels CHMI will be compared to simulation results.