# A MODIFIED PID CONTROLLER DESIGN FOR 3-PHASE SPWM MULTILEVEL INVERTER

# AIZZAT HAFIZUDDIN BIN AHMED NASIR

A report submitted in partial fulfillment of the requirements for the degree of Bachelor of Electrical Engineering with Honours

**Faculty of Electrical Engineering**

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2019

# **DECLARATION**

I declare that this thesis entitled "A MODIFIED PID CONTROLLER DESIGN FOR 3-PHASE SPWM MULTILEVEL INVERTER is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

Signature :

Name : AIZZAT HAFIZUDDIN BIN AHMED NASIR

Date : 14/6/2019

# APPROVAL

I hereby declare that I have checked this report entitled "A MODIFIED PID CONTROLLER DESIGN FOR 3-PHASE SPWM MULTILEVEL INVERTER" and in my opinion, this thesis it complies the partial fulfillment for awarding the award of the degree of Bachelor of Electrical Engineering with Honours

Signature

Supervisor Name

DR AZRITA BINTI ALIAS

Date

# **DEDICATIONS**

To my beloved mother and father

## **ACKNOWLEDGEMENTS**

I would like to express everlasting gratitude my supervisor and everyone involved in this project directly or indirectly altogether the same. This project may not be able to be completed in the designated time without assistance and guidance of my supervisor Dr. Azrita Binti Alias thus, I am completely grateful with her generosity, kindness and willingness for my final year project.

I am also greatly thankful to all the staff of Faculty of Electrical Engineering for their precious cooperating assistance and guidance to me during the completion of this research. I also would like to take this opportunity to express my gratitude to my friends who have given myriad of ideas, opinions for my project with no less of cooperation and willingness. Moreover, I am also greatly indebted to my family for their endless support in financial and encouragement without any less of patient with me.

Beyond everything else, I thank to The One, The Supreme Creator for giving me all that is necessary in order to complete this project, a strong heart and a mental fortress mind.

1

## **ABSTRACT**

Multilevel inverter is an evolved version of the conventional inverter and have risen in favour by many in industries out of its capability to operate for medium to high rating power equipment. It boast several advantages over inverter such as generating higher voltage using low rating equipment, produce a more pure sinusoidal voltage wave with increasing levels and less losses from the switching frequency. This project is to analyse a 3-phase 5-level multilevel inverter with sinusoidal pulse width modulation (SPWM) by using a PI and modified PID controller as a method to maintain desire output by using MATLAB and MATLAB Simulink. The gating component applied are the MOSFETS that acts as the switching component. The feedback controller of PI and modified PID are also designed and calculated and then tuned on MATLAB with trial and error through proper procedure an applied to ensure a steady voltage output of the 3-phase 5-level cascaded h-bride multilevel inverter. The results are analysed in the form of total harmonic distortion (THD) and power factor where the CHMI have low THD and power factor of ~1. The performance of both controller are also analysed and compared where modified PID is slight better as it have better response which ia average at 0.126s compare than that of PI at 0.157s and more robust if there is disturbance or voltage change.

#### **ABSTRAK**

Inverter bertingkat adalah versi evolusi dari inverter konvensional dan telah menjadi pilihan kepada banyak industri disebabkan keupayaannya untuk beroperasi untuk peralatan kuasa sederhana hingga tinggi. Ia mempunyai beberapa kelebihan berbanding inverter seperti menghasilkan voltan yang lebih tinggi menggunakan peralatan penarafan yang rendah, menghasilkan gelombang voltan sinusoidal yang lebih tulen dengan peningkatan tingkat dan mengurangkan kehilangan kuasa dari kekerapan peralihan suis. Tujuan projek ini adalah menganalisis inverter bertingkat 5 tahap 3 fasa dengan modulasi lebar denyut sinusoidal (SPWM) dengan menggunakan pembawa tunggal dan 4 bentuk gelombang rujukan sebagai kaedah kawalan untuk menghasilkan output keinginan dengan menggunakan MATLAB. Komponen 'gating' yang digunakan adalah MOSFET yang bertindak sebagai komponen pensuisan. Pengawal maklum balas PI dan PID juga adalah direka dan diubahsuai untuk digunakan untuk memastikan output voltan mantap bagi inverter h-jambatan berbilang peringkat 5 tingkat. Hasilnya dianalisis dalam bentuk total distorsi harmonik (THD) dan faktor kuasa. Hasil dari implementasi kedua-dua sistem kawalan juga akan dianalisis dan perbandingan akan disertakan.

# TABLE OF CONTENTS

|             |                                                                             | PAGE            |

|-------------|-----------------------------------------------------------------------------|-----------------|

| DECL        | LARATION                                                                    |                 |

| APPR        | OVAL                                                                        |                 |

| DEDI        | CATIONS                                                                     |                 |

| <b>ACKI</b> | NOWLEDGEMENTS                                                               | 1               |

|             |                                                                             | 2               |

|             | TRACT                                                                       |                 |

| ABST        | TRAK                                                                        | 3               |

| TABI        | LE OF CONTENTS                                                              | 4               |

| LIST        | OF TABLES                                                                   | 6               |

| LIST        | OF FIGURES                                                                  | 7               |

| LIST        | OF SYMBOLS AND ABBREVIATIONS                                                | 10              |

| СНА         | PTER 1 INTRODUCTION                                                         | 11              |

| 1.1         | Background                                                                  | 11              |

| 1.2         |                                                                             | 13              |

| 1.3         | Problem Statement                                                           | 14              |

| 1.4         | Objective                                                                   | 15<br>15        |

| 1.5         | Scope                                                                       |                 |

| СНА         | PTER 2 LITERATURE REVIEW                                                    | <b>16</b><br>16 |

| 2.1         | Introduction                                                                | 16              |

| 2.2         | Inverter & Multilevel Inverter                                              | 18              |

|             | 2.2.1 Flying Capacitor Multilevel Inverter                                  | 19              |

|             | 2.2.2 Diode-Clamped Multilevel Inverter                                     | 20              |

|             | 2.2.3 Cascaded H-Bridge Multilevel Inverter                                 | 21              |

| 2.3         | Sinusoidal Pulse Width Modulation (SPWM) 2.3.1 SPWM for Multilevel Inverter | 22              |

|             | a gray A Tarahai ayan                                                       | 24              |

| 0.4         | 2.3.2 Types of SPWM Techniques Proportional Integral Derivative Controller  | 25              |

| 2.4         | a.s. 1. Deportional Integral (PI)                                           | 26              |

|             | 2.5.2 Advantages and Disadvantages of PID Controller                        | 27              |

|             | 2.5.3 Modification of PID Controller (PI-D)                                 | 28              |

|             | 2.5.4 Modification of PID Controller (I-PD)                                 | 29              |

| 2.6         | Summary                                                                     | 30              |

| CU          | APTER 3 METHODOLOGY                                                         | 3:              |

| 3.1         | Introduction                                                                | 3               |

| 3.2         | Project Project Reprise Taknikal Malaysia Malaka                            | 32<br>32        |

| 3.3         | Project Process Background Loop and Close Loop                              | 3.<br>34        |

| 3.4         | System Flowchart for Open Loop and Close Loop                               | ٦.              |

| 3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Basic Working Principle of Cascaded H-Bridge Multilevel Inverter (CHMI) The Switching Strategy for 3-phase 5-level CHMI Designing of Proportional Integral (PI) Controller Designing of I-D Controller Summary |                                                                                    |                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|

| CHAP                            | TER 4                                                                                                                                                                                                          | RESULTS AND DISCUSSIONS                                                            | 51              |

| 4.1                             | Introdu                                                                                                                                                                                                        | action                                                                             | 51              |

| 4.2                             | Modul<br>Carrier                                                                                                                                                                                               | ation Technique Using SPWM Switching Strategy by Comparing 1 and 4 Sinusoidal Wave | 51              |

| 4.3                             | Simula                                                                                                                                                                                                         | ation Result                                                                       | 52              |

|                                 | 4.3.1                                                                                                                                                                                                          | 3-Phase 5-level Cascaded H-bridge Multilevel Inverter (CHMI)                       | 53              |

|                                 | 4.3.2                                                                                                                                                                                                          | 3 Phase 5 Level CHMI Without Low Pass Filter                                       | 54              |

|                                 | 4.3.3                                                                                                                                                                                                          | 3 Phase 5 Level CHMI With Low Pass Filter                                          | 55              |

|                                 | 4.3.4                                                                                                                                                                                                          | Range of Modulation index for the 5 level Multilevel Inverter                      | 57              |

|                                 | 4.3.5                                                                                                                                                                                                          | Modulation Index and Its Effect on Total Harmonic Distortion                       | 59              |

|                                 | 4.3.6                                                                                                                                                                                                          | Close-loop System of Proportional Controller (PI)                                  | 62              |

|                                 | 4.3.7                                                                                                                                                                                                          | Closed-loop System of Modified Proportional Controller Derivative (PID)            | 64              |

|                                 | 4.3.8                                                                                                                                                                                                          | Table on Data of Voltage Change Effect on System PI and Modified PID Controller    | 66              |

|                                 | 4.3.9                                                                                                                                                                                                          | Discussion of The Result                                                           | 68              |

| 4.4                             | Summ                                                                                                                                                                                                           | ary                                                                                | 69              |

| CHAP                            | TER 5                                                                                                                                                                                                          | CONCLUSION AND RECOMMENDATIONS                                                     | 70              |

| 5.1                             | Conclu                                                                                                                                                                                                         | usion                                                                              | 70              |

| 5.2                             | Recon                                                                                                                                                                                                          | nmendation                                                                         | 70              |

| REFE                            | RENC                                                                                                                                                                                                           | ES                                                                                 | 71              |

| APPE                            | NDICE<br>Chart                                                                                                                                                                                                 | ES                                                                                 | <b>74</b><br>74 |

# LIST OF TABLES

| Table 1.1 Comparison between 2 level and 5 level CHMI inverter                    | 13         |

|-----------------------------------------------------------------------------------|------------|

| Table 2.1 Comparison of number of components utilised by each multilevel inverter |            |

| topologies[9]                                                                     | 17         |

| Table 2.2 Advantage and Disadvantage of SPWM [16]                                 | 21         |

| Table 2.3 Advantages and disadvantages for PID and PI controller                  | 27         |

| Table 2.4 Result from PID and I-PD controller [25]                                | 30         |

| Table 3.1 Voltage level and switching for 5-level CHMI.                           | 37         |

| Table 3.2 Parameter of the system                                                 | 39         |

| Table 3.3 Parameter for the switching method (SPWM)                               | 40         |

| Table 3.4 Uncompensated system and compensated system                             | <b>4</b> 4 |

| Table 4.1 Modulation Index and The Correlating Total HArmonic Distortion          | 59         |

| Table 4.2 Change of voltage effect on system by PI controller                     | 66         |

| Table 4.3 Voltage change effect on system by modified PID controller              | 67         |

| Table 4.4 Result from the simulation for 3 phase 5 level CHMI                     | 68         |

# **LIST OF FIGURES**

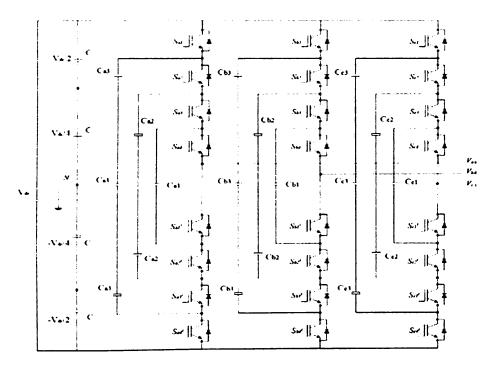

| Figure 2.1 3-phase 5 level of flying capacitor multilevel inverter [13]           | 18 |

|-----------------------------------------------------------------------------------|----|

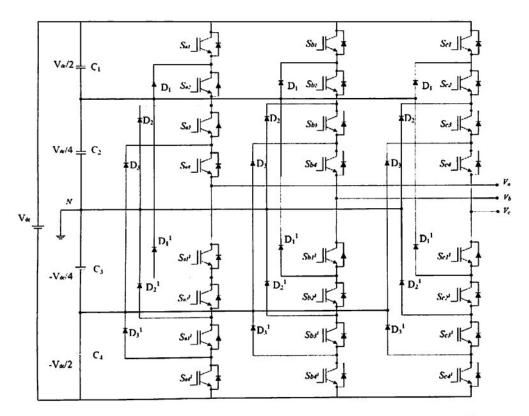

| Figure 2.2 3-phase 5 level topology of Diode-Clamped multilevel inverter [13]     | 19 |

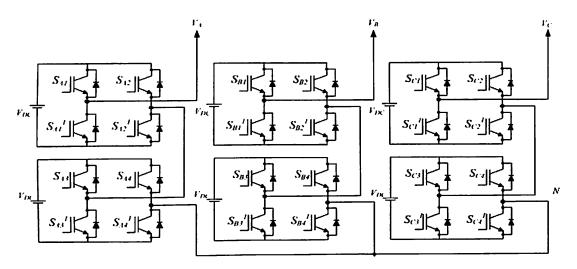

| Figure 2.3 3-phase 5 level topology of Cascaded H-Bridge multilevel inverter [13] | 20 |

| Figure 2.4 Example of SPWM principle where carrier waveform is compared with      |    |

| reference waveform [18]                                                           | 23 |

| Figure 2.5 Gating from the comparison between 2 signals [18]                      | 23 |

| Figure 2.6 Phase Disposition[21]                                                  | 24 |

| Figure 2.7 Phase Opposition Disposition[21]                                       | 24 |

| Figure 2.8 Alternative Phase Disposition[21]                                      | 25 |

| Figure 2.9 General concept of PID controller                                      | 26 |

| Figure 2.10 Basic principle of PI in block diagram[24]                            | 27 |

| Figure 2.11 Block diagram of PI-D with derivative feedback                        | 28 |

| Figure 2.12 Time domain equation for PID and I-PD controller [25].                | 29 |

| Figure 2.13 Block diagram for I-PD controller                                     | 29 |

| Figure 3.1 System development life cycle                                          | 32 |

| Figure 3.2 Project Flow and Summary                                               | 33 |

| Figure 3.3 Project flow without feedback control                                  | 34 |

| Figure 3.4 Project flow with feedback control                                     | 35 |

| Figure 3.5 Single phase 5-level CHMI                                              | 36 |

| Figure 3.6 3 phase 5 level Cascaded H-Bridge Multilevel Inverter Design           | 37 |

| Figure 3.7 Upper leg H-Bridge for 5 level CHMI                                    | 38 |

| Figure 3.8 Lower leg H-Bridge for 5 level CHMI                                    | 38 |

| Figure 3.9 A Universiti Teknika Malaysia Melaka                                   | 40 |

| Figure 3.10 The sinusoidal waveform and the single traingular carrier waveform for |    |

|------------------------------------------------------------------------------------|----|

| Va, 1                                                                              | 41 |

| Figure 3.11 The sinusoidal waveform and the single triangular carrier waveform     |    |

| for $Vb$ , 1                                                                       | 41 |

| Figure 3.12 Thes sinusoidal waveform and the single triangular carrier waveform    |    |

| for Vc, 1                                                                          | 42 |

| Figure 3.13 Simplified circuit used to obtain the transfer function                | 42 |

| Figure 3.14 Root locus tool editor for the transfer function of the system         | 43 |

| Figure 3.15 Designing the compensated sytem by adding integrator and zero pole     | 44 |

| Figure 3.16 Compensated system transient response                                  | 45 |

| Figure 3.17 Compensator editor for the system with the calculated real zero        | 45 |

| Figure 3.18 Ki and integrator of PI controller inside the subsystem                | 46 |

| Figure 3.19 The whole Pi controller with Kp                                        | 46 |

| Figure 3.20 PID Block Diagram                                                      | 47 |

| Figure 3.21 Equivalent Block diagram                                               | 47 |

| Figure 3.22 PI-D control system                                                    | 48 |

| Figure 3.23 Modified PID structure                                                 | 49 |

| Figure 3.24 Whole modified PID structure                                           | 49 |

| Figure 4.1 Switching Used for 3 phase 5 level CHMI                                 | 52 |

| Figure 4.2 Switches result from SPWM control structure                             | 53 |

| Figure 4.3 Output voltage without lowspass filter                                  | 54 |

| Figure 4.4 THD value for 3 phase 5 level CHMI without filter                       | 55 |

| Figure 4.5 Output voltage with modulation index at 0.85 at all phase               | 56 |

| Figure 4.6 Output voltage 3 phase for phase 0 when M=0.85                          | 56 |

| Figure 4.7 Output vol                                                              | 56 |

| Figure 4.8 THD for H-Bridge CHMI value after implementation of filter           | 57 |

|---------------------------------------------------------------------------------|----|

| Figure 4.9 3 Phase 5 level CHMI at MI 0.5                                       | 57 |

| Figure 4.10 3 phase 5 level CHMI with MI at 1.3                                 | 58 |

| Figure 4.11 Uncompensated system 3 phase 5 level CHMI                           | 60 |

| Figure 4.12 Uncompensated system of 3 phase 5 level CHMI experiencing voltage   |    |

| drop                                                                            | 61 |

| Figure 4.13 3 phase 5 level CHMI with PI controller system                      | 62 |

| Figure 4.14 3 phase 5 level CHMI with PI controller system experiencing voltage |    |

| drop                                                                            | 63 |

| Figure 4.15 3 phase 5 level CHMI with modified PID controller                   | 64 |

| Figure 4.16 3 phase 5 level CHMI with modified PID experiencing voltage drop    | 65 |

## LIST OF SYMBOLS AND ABBREVIATIONS

THD - Total Harmonic Distortion

PF - Power Factor

SPWM - Sinusoidal Pulse Width Modulation

SDLC - System Development Life Cycle

VSI - Voltage Source Inverter

CSI - Current Source Inverter

MLI - Multilevel Inverter

AC - Alternating Current

DC Direct Current

CHMI Cascaded H-Bridge Multilevel Inverter

PWM Pulse Width Modulation

PD Phase Disposition

POD Phase Opposition Disposition

APO Alternate Phase Disposition

PI Proportional-Integral

PID Proportional-Integral-Derivative

## **CHAPTER 1**

#### INTRODUCTION

## 1.1 Background

As the nation and its people are evolving into a new age of technology advancement so does the requirement for such task. The consumption of energy and resource alone are exceptionally high and resulting numerous of side effect such as burning of fossil fuel of which lead to the emission of greenhouse gas, which in turn lead to global warming. As culmination from such wanton cases, renewable energy has been a popular choice nowadays and simpler design for many electronic and more efficient controllers must be implemented.

An inverter is used to convert DC source into an AC source. Among its output commonly known are usually of 3 types of forms which is the square wave usually applied for some resistive loads, quasi/modified sine wave for inductor, capacitor, resistive loads and pure sine wave for prevalent application, thus classifying all of it into 3 types of inverter output waveform[1]. The inverter are also known to have been classified into 2 operation mode which is the voltage source inverter (VSI) and current source inverter (CSI), however, (VSI) have several distinct advantages over (CSI) such as being more efficient, highly dependable and quick dynamic response[2]. Which is why of it being implemented in this project.

However, as the growth renewable energy approached equipped with high power equipment and high power rating machineries are ever increasing, the topologies of inverter too must evolve to suits the need of the industry. Thus, a multilevel inverter is invented with design evolved from the existing one. A multilevel

inverter(MLI) is suitable for energy control of medium to high power rating equipment. With its topologies, a MLI is preferable purely because of its performance in generating a higher voltage from a lower rating powered device,

C Universiti Teknikal Malaysia Melaka

better voltage waveform ,using pulse width modulation control its switching frequency is reduced and smaller total harmonic distortion (THD)[3].

The focus however would be on the method of controlling section as a good controller can contribute a significant effect on the efficiency of the inverter, such as the switching frequency, minimizing the switching loss, steady state with fast transient response from control point of view. Variety of controller are available such as neural network and PID controller. Artificial neural network is such information etiquette is implement the way of brain processing work, involving the neural connection and mimicking it which is differ from conventional controllers[4]. For PID controller, it is a type feedback controller famous among controllers, PID stands for proportional, integral, derivative. In each application, coefficient of these three actions are varied to get optimal response and control. Controller input is error signal and output is given to the plant/process. Output signal of controller is generated, in such a way that, output of plant is try to achieve desired value[5].

However, among the controllers, PID is chosen because of its simple topology to implement such as a simple equation, require low amount of resource, more robust to tuning any discord, easier to calibrate by normal trial and error and better response to unmeasured disturbances. Model-based controllers recover from unmeasured disturbances with only an integral type of action, while PID has also the proportional and derivative action that immediately act on an unknown disturbance[5]. However, despite its advantageous characteristic, PID controller still have a setback. Which is the set point kick phenomenon from the derivative action. To avoid this, modification is made with an example PI-D and I-PD scheme where derivative action is only operated on feedback path so as to avoid any differentiation.

#### 1.2 Motivation

Development of renewable energy are rapidly expanding. Large scale renewable power plant are higher than ever and should not be neglected by the fact in 2018 the global solar installation only will be 109GW [6]. Thus, the needs of inverter are now more popular than ever and are an integral to the power distribution system. Application of inverter would bring much advantages to the industry especially of that multilevel inverter, famed for its capability to operate in medium to high power energy control equipment or grid. Moreover, as shown in Table 1.1 below 5 level inverter shown more efficiency than that of the 2 level.

Table 1.1 Comparison between 2 level and 5 level CHMI inverter

|                                    | Three phase 2- | Three phase 5-level CHMI |  |

|------------------------------------|----------------|--------------------------|--|

|                                    | Level Inverter | using SPWM               |  |

| THD value<br>after filter          | 14.54%         | 0.75%                    |  |

| Power<br>Factor(PF)                | ~1             | ~1                       |  |

| Voltage output (V <sub>rms</sub> ) | 88.89V         | 415.47V                  |  |

From Table 1.1 above it can be stipulated that 3 phase 5-level CHMI using SPWM give a better result as it have lower value of THD and higher value of voltage output than that 2 level inverter that have significant higher amount of THD.A modified controller is devised and simulate in this paper using MATLAB Simulink to inquire of its ability to operate under designated load and giving the intended voltage output not to mention smaller amount of total harmonic distortion.

## 1.3 Problem Statement

With the advancement of our technology development, the growth of electricity are also exponential, corresponding with the demand. Thus, multitudes of power distribution have been created and innovated to handle electricity distribution properly. One of the core component in the system is the inverter which is crucial in converting DC signal to AC signal and control the power flow in the distribution system. However, despite the commendable advancement in this field, setback and predicament are bound to occur.

The latter are usually in the form significant switching losses, voltage-balancing concerns and raised number of components. The needs of multilevel inverter however is undeniable as the growth of energy control of medium to high power rating equipment in renewable energy sector increase. For practical approach, in Power grid system, there are usually change of load where voltage drop may occur under certain condition so to speak. Thus, to maintain the purity of sine wave, a feedback controller need to be implemented so that the voltage output is maintained. This project is to research on the feedback controller implemented. Typical PID feedback controller however usually have set point kick phenomenon which is a condition where if the reference input is a step function, the manipulated variable will involve an impulse function, such set point kick phenomenon can cause equipment to be damaged. This project suggest modification to the PID controllers.

# 1.4 Objective

## This project endeavour to:

- Simulate three phase Cascaded H-bridge Multilevel Inverter with MATLAB-Simulink software using SPWM technique with one carrier.

- 2. Analyse the performance of CHMI in terms of total harmonic distortion (THD) and the power factor for open loop system.

- Design a feedback PI and modified PID controller and implement it into CHMI.

- 4. Analyse the performance of both controllers on the three phase Cascaded H-bridge Multilevel Inverter.

# 1.5 Scope

The scope for this project are:

- Resolved on the cascaded H-bridge for 5-level 3 phase

- Simulate the 3 phase H-bridge multilevel inverter by employing MATLAB Simulink.

- The voltage output  $(V_{rms})$  is 400V which is standard grid voltage, from the peak voltage sine wave output.

- Modified PID and PI are implemented as the controller.

## **CHAPTER 2**

#### LITERATURE REVIEW

## 2.1 Introduction

This chapter will discuss the topology of typical multilevel inverter available and frequent applied in the industries. This literature review will enhance understanding about component used in final year project. Moreover, this chapter will also discuss about the sinusoidal pulse width modulation (SPWM) technique used in order to reduce harmonic load voltage.

This chapter will also include literature review of controller being used and available, the working principle of controller.

## 2.2 Inverter & Multilevel Inverter

Designed of many electrical device is progressively being upgraded and applied in an industrial application which utilize large amount of power. Significant amount of appliances in industries however need medium or low power for their operation. The Multilevel inverter is like an inverter and it is used for industrial applications as alternative in high power and medium voltage situations.

As the industries is getting bigger and larger for production and technological advancement, multilevel inverter is being chosen for it advantageous characteristic such as multilevel inverters produce common mode voltage, reducing the stress of the motor and do not damage the motor, it also can operate at both fundamental switching frequencies that are higher switching frequency and lower switching frequency. It should be noted that the lower switching frequency means lower switching loss and higher efficiency is obtained[7]. Variety of multilevel inverter topology have been suggested in this review, three main topologies of multilevel inverters are the diode clamped inverter, flying capacitor inverter, and the cascaded h-bridge inverter[8] From table 2.1 below, it is shown and can be inferred that which among the 3 multilevel inverter comprised of the lowest number of component.

Table 2.1 Comparison of number of components utilised by each multilevel inverter topologies[9]

| Multilevel<br>Inverter<br>Topology | Number of level | Power<br>Switches | Power Diodes | DC Bus Capacitors |

|------------------------------------|-----------------|-------------------|--------------|-------------------|

| Flying<br>Capacitor                | 5               | 8                 | -            | 10                |

| Cascaded-<br>H Bridge              | 5               | 8                 | -            | -                 |

| Diode-<br>clamped                  | 5               | 8                 | 12           | 4                 |

From table 2.1 above, it is shown that cascaded h-bridge multilevel inverter have the lowest number of component employment than the other 2 at only 13 component. This shows that cascaded h-bridge is the most convenient to be used. This is further validated by the table above as more component will only resulting higher cost to build and more complex to handle the operating mechanism.

# 2.2.1 Flying Capacitor Multilevel Inverter

This type of multilevel inverter requires capacitor to be pre-charged. It is quite the same in term of topology with diode clamped multilevel inverter, however the capacitor is instead used to separate the input DC voltage. The capacitor near to the source have higher voltage while the one near to the load have lower voltage. They are known as Flying Capacitor Multilevel Inverter, purely from reason of the capacitors float with respect to earth's potential[10]. For each voltage output level, 4 switches are turned on. The amount of component needed is correlate with the formula (n-1) for the voltage sources,2(n-1) for switching devices and(n-1)x ((n-2))/2 for capacitor. n is the number of level[11].

Flying capacitor have its own advantages where the capacitors allow extra energy during long energy discharge transient when 'n' level is high and lower THD when the 'n' is high. It also, however posed significant disadvantages where the topology can be bulky and more expensive from the large number of capacitor used and complex control to maintain capacitor's voltage balance[12]. Figure 2.1 below shown the topology flying capacitor multilevel inverter.

Figure 2.1 3-phase 5 level of flying capacitor multilevel inverter [13]

# 2.2.2 Diode-Clamped Multilevel Inverter

The implementation of diodes which is to produce multiple voltage level through different phases to the capacitor banks that are arranged in series is the main idea for diode clamped inverter. It also reduced stress on other electrical devices by a diode that transfer limited amount of voltage. However, this topology also has its own drawback where its maximum output voltage is only half of the input DC voltage. This weakness can be countered by increasing the level of the inverter, thus increasing the switches, diodes and capacitors[7]. The design however is limited 3 level out of capacitor balancing issues. This problem can be resolved by using a two times voltage source or cascading two diode clamped multilevel inverters[11]. Figure 2.2 below shown 5-level topology for diode-clamped multilevel inverter.

Figure 2.2 3-phase 5 level topology of Diode-Clamped multilevel inverter [13]

## 2.2.3 Cascaded H-Bridge Multilevel Inverter

For CHMI, it is composed of two series connected H-bridge which are also fed by an independent voltages sources. Thus, the synthesized voltage waveform is the sum of all of the individual cell outputs mainly because the outputs of the H-bridge cells are arranged and connected in series. The output voltage is given by.

$$V = V1 + V2 \tag{2-1}$$

Where the output voltage of the first cell is known as V1 and the output voltage of the second cell is signified by V2. There are five level of output voltage which is 2V, V, 0, -V, -2V. The main advantages of cascaded H-bridge inverter are that it needs least number of components, modularized circuit and soft switching can be utilized. But the main disadvantage is that when the voltage level increases, the number of components such as switches increases and also the sources. Thus resulting the cost and weight to be increased. Field where high power and power quality are crucial is where the cascaded H-bridge multilevel inverters have been employed for example, static synchronous compensators, active filter and reactive power compensation applications, photo voltaic power conversion, continuously power supplies, and magnetic resonance imaging[13]. Figure 2.3 below shown topology 5-level cascaded h-bridge multilevel inverter.

Figure 2.3 3-phase 5 level topology of Cascaded H-Bridge multilevel inverter [13]