FPGA IMPLEMENTATION OF HOG ALGORITHM

USING SDSOC

CHEONG JIA MUN

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

C Universiti Teknikal Malaysia Melaka

### FPGA IMPLEMENTATION OF HOG ALGORITHM USING SDSOC

**CHEONG JIA MUN**

This report is submitted in partial fulfilment of the requirements for the degree of Bachelor of Electronic Engineering with Honours

> Faculty of Electronic and Computer Engineering Universiti Teknikal Malaysia Melaka

> > 2019

|                                                                                  | ITI TEKNIKAL MALAYSIA MELAKA<br>eraan elektronik dan kejuruteraan komputer<br>rang pengesahan status laporan<br>PROJEK SARJANA MUDA II      |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Tajuk Projek : FPGA                                                              | IMPLEMENTATION OF HOG                                                                                                                       |

|                                                                                  | THM USING SDSOC                                                                                                                             |

|                                                                                  | membenarkan laporan Projek Sarjana Muda<br>syarat-syarat kegunaan seperti berikut:                                                          |

| -                                                                                | at salinan untuk tujuan pengajian sahaja.<br>buat salinan laporan ini sebagai bahan                                                         |

| SULIT*                                                                           | (Mengandungi maklumat yang berdarjah<br>keselamatan atau kepentingan Malaysia<br>seperti yang termaktub di dalam AKTA<br>RAHSIA RASMI 1972) |

| TERHAD*                                                                          | (Mengandungi maklumat terhad yang<br>telah ditentukan oleh organisasi/badan di<br>mana penyelidikan dijalankan.                             |

| TIDAK TERHAD                                                                     |                                                                                                                                             |

|                                                                                  | Disahkan oleh:                                                                                                                              |

| (TANDATANGAN PENULIS)                                                            | (COP DAN TANDATANGAN PENYELIA)                                                                                                              |

| Alamat Tetap: <u>49, leboh tamarind,</u><br>taman selatan,<br><u>41200 klang</u> |                                                                                                                                             |

| Tarikh : <u>31 MEI 2019</u>                                                      | Tarikh : <u>31 MEI 2019</u>                                                                                                                 |

\*CATATAN: Jika laporan ini SULIT atau TERHAD, sila lampirkan surat daripada pihak berkuasa/organisasi berkenaan dengan menyatakan sekali tempoh laporan ini perlu dikelaskan sebagai SULIT atau TERHAD.

## DECLARATION

I declare that this report entitled "FPGA IMPLEMENTATION OF HOG ALGORITHM USING SDSOC" is the result of my own work except for quotes as cited in the references.

Signature : ..... Author : CHEONG JIA MUN Date : 31/05/2019

# APPROVAL

I hereby declare that I have read this thesis and in my opinion this thesis is sufficient in terms of scope and quality for the award of Bachelor of Electronic Engineering with Honours.

| Signature       | : |                                         |

|-----------------|---|-----------------------------------------|

| Supervisor Name | : | Profesor Dr. Zulkalnain Bin Mohd Yussof |

| Date            | : | 31/05/2019                              |

## DEDICATION

I dedicate this research work to my beloved father and mother who always support and encourage me through my education journey, my beloved lecturers, supervisor who do not stop giving knowledge and my beloved friends who always provide assistance.

### ABSTRACT

In today modern world, a precise and rapid pedestrian detection is an extremely important job for a wide range of applications in automotive and personal identification. One of the most reliable and common use algorithms of computer vision for object detection and human detection is Histogram of Oriented Gradients (HOG) algorithm. HOG is also a high complexity and compute intensive task for human detection. This project implementations of HOG algorithm using an embedded platform, that is the Zedboard development kit board which contains the Xilinx Zynq R-7000 All Programmable system on chip (SoC) that is comprised of both an ARMplatform processing system and an FPGA based programmable logic. This platform gave us the ability to execute different parts of the algorithm simultaneously both on the CPU and the FPGA. The platform has the advantages of being portable and small size high computing speed, low cost and able to be built with small cameras for monitoring purposes.

### ABSTRAK

Dalam dunia moden hari ini, pengesanan manusia yang tepat dan cepat adalah tugas penting bagi pelbagai aplikasi seperti pengenalan diri automotif dan orang. Algoritma "Histogram of Gradients Oriented (HOG)" adalah salah satu algoritma pengimejan yang paling dipercayai dan digunakan penglihatan komputer untuk pengesanan objek dan pengesanan manusia. Walau bagaimanapun, algoritma HOG juga merupakan kerumitan tinggi dan mengira tugas intensif untuk pengesanan manusia. Pelaksanaan projek algoritma HOG ini menggunakan platform terbenam, iaitu papan pengembangan Zedboard yang mengandungi sistem "Xilinx Zynq R-7000 All Programmable" pada cip (SoC) yang terdiri daripada sistem pemproses "ARMplatform" dan programmable berbasis FPGA logik. Platform ini memberi kita kemampuan untuk melaksanakan bahagian-bahagian algoritma yang berlainan secara serentak pada CPU dan FPGA. Sistem ini memberikan kelebihan saiz kecil, kos rendah, kelajuan pengkomputeran tinggi, dan mudah alih dan boleh dibina dalam kamera kecil untuk aplikasi pengawasan.

### ACKNOWLEDGEMENT

First and foremost, I would like to express my deep appreciation and gratitude to my supervisor, Professor Dr. Zulkalnain Bin Mohd Yussof who has provided advice, guidance and encouragement of his patience throughout the progress of this project. Next, my appreciation goes to the panels that have an opinion that allows the improvement of the quality of the report. Big thanks for my beloved parents and family who has been so supportive and make me stronger to face every challenge all these years. Finally, thanks to all those involved directly or indirectly especially friends who helped me and giving ideas in the process of completing this study.

## **TABLE OF CONTENTS**

| Dec  | laration                     | i   |

|------|------------------------------|-----|

| Арр  | proval                       | i   |

| Ded  | lication                     |     |

| Abs  | stract                       |     |

| Abs  | strak                        |     |

| Ack  | nowledgement                 | iii |

| Tab  | le of Contents               | iv  |

| List | of Figures                   | vii |

| List | of Tables                    | ix  |

| List | of Symbols and Abbreviations | x   |

| List | of Appendices                | xi  |

| CH   | APTER 1 INTRODUCTION         | 1   |

| 1.1  | Introduction of the Project  | 1   |

| 1.2  | Problem Statement            | 2   |

| 1.3  | Project Objectives           | 3   |

| 1.4  | Scope of Work                | 3   |

| 1.5  | Expected Outcome                                             | 4  |

|------|--------------------------------------------------------------|----|

| 1.6  | Thesis structure                                             | 4  |

| СНА  | PTER 2 BACKGROUND STUDY                                      | 5  |

| 2.1  | Introduction                                                 | 5  |

| 2.2  | Overview                                                     | 6  |

| 2.3  | Feature descriptor                                           | 6  |

| 2.4  | Sliding Window Based Pedestrian Detection or Human detection | 10 |

| 2.5  | Histogram of Oriented Gradients Feature Extraction Algorithm | 11 |

| 2.6  | Support Vector Machine (SVM)                                 | 19 |

| 2.7  | Non-maximal suppression                                      | 20 |

| 2.8  | Real Time Human Detection                                    | 21 |

| 2.9  | Software-Defined System on Chip (SDSoC).                     | 22 |

| 2.10 | Field-programmable gate array (FPGA) Zedboard Platform       | 23 |

| СНА  | PTER 3 METHODOLOGY                                           | 26 |

| 3.1  | Project Planning                                             | 27 |

| 3.2  | Research section                                             | 28 |

| 3.3  | Implementation in Visio studio 2017                          | 29 |

| 3.4  | Applying the performance in SDSoC Software                   | 29 |

| 3.5  | Hardware Implementation – Xilinx Zedboard                    | 31 |

| СНА  | PTER 4 RESULTS AND DISCUSSION                                | 33 |

v

| 4.1                                          | Introduction                    | 33 |

|----------------------------------------------|---------------------------------|----|

| 4.2                                          | HOG                             | 34 |

| Non-                                         | maximal suppression             | 37 |

| 4.3                                          | Software development            | 39 |

| 4.4                                          | Embedded System Performance     | 39 |

| 4.5                                          | Hardware implementation         | 42 |

| <b>CHAPTER 5 CONCLUSION AND FUTURE WORKS</b> |                                 | 48 |

| 5.1                                          | Conclusion                      | 48 |

| 5.2                                          | Recommendation for future works | 49 |

| REF                                          | ERENCES                         | 51 |

| APP                                          | ENDIX A                         | 56 |

| App                                          | endix B                         | 67 |

| Арр                                          | endix C                         | 69 |

vi

## **LIST OF FIGURES**

| Figure 2.1: The pipeline of GIST feature descriptor [7]                                                                                                                                    | 6               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

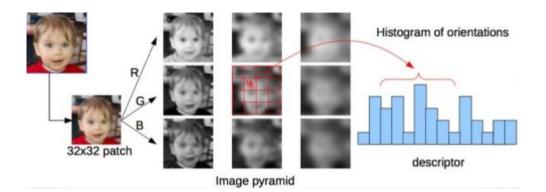

| Figure 2.2 SIFT feature description [8]                                                                                                                                                    | 7               |

| Figure 2.3: SIFT descriptor diagram [9]                                                                                                                                                    | 7               |

| Figure 2.4: Improved Haar-like features operators. (a) Edge features, (<br>triangle features/Line features, (c) Four triangle feature/Spatial diagonal feature-<br>Centre-surround feature |                 |

| Figure 2.5: Sliding Window Based detection in a frame [19]                                                                                                                                 | 10              |

| Figure 2.6: Block diagram of HOG based pedestrian detection                                                                                                                                | 11              |

| Figure 2.7: Illustration of image for sliding window-based object detection.                                                                                                               | 13              |

| Figure 2.8: Filter mask with coefficient in x and y directions                                                                                                                             | 15              |

| Figure 2.9: Gradient magnitude and orientation divided into nine bins for h<br>[19]                                                                                                        | nistogram<br>15 |

| Figure 2.10: HOG feature extraction flow (a) Input image (b) Gradient magn<br>orientation map of the sub-block of the image (c) Accumulated gradient or<br>(d) feature histogram           |                 |

| Figure 2.11: Rectangular R-HOG and circular C-HOG                                                                                                                                          | 18              |

| Figure 2.12: Support Vector Machine classifier for human detection [23]                                                                                                                    | 19              |

| Figure 2.13: Intersection over Union function                                                                                                                                              | 20              |

| Figure 2.14: Non-maximal suppression [26] (a) Original NMS detection (b NMS results (c) Improved NMS results                                                                               | )Original<br>21 |

| Figure 2.15: The ZYNQ chip Platform Architecture. [27]                                                                                                                                     | 22              |

| Figure 2.16: Platform Architecture of Zynq. [2]                                                                                                              | 23          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2.17: The Xilinx Zedboard overview.                                                                                                                   | 25          |

| Figure 3.1: Overall implementation technique flow chart                                                                                                      | 27          |

| Figure 3.2: The diagram when using SDSOC software.                                                                                                           | 30          |

| Figure 3.3: Diagram of implementation in Xilinx SDSoC software platform.                                                                                     | 30          |

| Figure 3.4: The project block diagram when implementing in software and hardw                                                                                | vare<br>31  |

| Figure 4.1: Structure when implementing in software and hardware                                                                                             | 33          |

| Figure 4.2: The gradient magnitude and orientation                                                                                                           | 34          |

| Figure 4.3: Block normalization algorithm                                                                                                                    | 35          |

| Figure 4.4: HOG feature descriptor flow (a) Input image (b) Gradient magnitude orientation map of the sub-block of the image (c) 8x8 cells feature histogram | and<br>36   |

| Figure 4.5: HOG feature descriptor (a) Input image (b) the positive SVM weight computed HOG                                                                  | t (c)<br>37 |

| Figure 4.6: Applying non-maxima suppression                                                                                                                  | 38          |

| Figure 4.7 Non-maximum suppression                                                                                                                           | 38          |

| Figure 4.8: The codes are compiled in Visual Studio.                                                                                                         | 39          |

| Figure 4.9: HOG is implementing in SDSoC                                                                                                                     | 40          |

| Figure 4.10: Profiling results of HOG algorithm using SDSoC                                                                                                  | 41          |

| Figure 4.11: Built configuration in SDSoC                                                                                                                    | 42          |

| Figure 4.12: Steps to present the profiling oh HOG algorithm                                                                                                 | 43          |

| Figure 4.13: The profiling of HOG algorithm according to implementation platfo                                                                               | orm<br>43   |

| Figure 4.14: The performance estimation report of project                                                                                                    | 43          |

| Figure 4.15: The structure when implementing in hardware                                                                                                     | 44          |

## LIST OF TABLES

ix

| Fable 2.1: Comparison between SIFT and HOG feature descriptor                  | 8 |

|--------------------------------------------------------------------------------|---|

| Table 2.2: HOG descriptor parameter for several different object classes [22]1 | 8 |

| Fable 2.3: Xilinx Zedboard platform technical specification                    | 5 |

| Table 3.1: The project software and hardware implementation                    | 2 |

| Fable 4.1: HOG algorithm flow4                                                 | 1 |

| Table 4.2: Comparison of computation time for one HOG 4                        | 5 |

| Table 4.3: Result of HOG algorithm for human detection4                        | 6 |

| Fable 4.4: Result of HOG algorithm for human detection with error              | 6 |

### LIST OF SYMBOLS AND ABBREVIATIONS

- HOG : Histogram of Oriented Gradients

- FPGA : Field-Programmable Gate Array

- SDSoC : Software-Defined System-On-Chip

- ARM : Advanced RISC Machines

- SIFT : Scale-invariant Feature Transform

- SVM : Support Vector Machine

- PD : Pedestrian Detection

- USB : Universal Serial Bus

- RGB : Red Green Blue

- ASID : Application Specific Integrated Circuit

- HDL : Hardware Description Language

- PC : Personal computer

- IDE : Integrated development environment

- API : Application programming interface

- NMS : Non-maximum Suppression

- IoU : Intersection over Union

## LIST OF APPENDICES

| Appendix A: Zedboard Hardware User's Guide                    | 56 |

|---------------------------------------------------------------|----|

| Appendix B: Computation of magnitude and orientation gradient | 67 |

| Appendix C: Poster design                                     | 69 |

### **CHAPTER 1**

### **INTRODUCTION**

This chapter explained about the introduction of this project following by the the problem statement. For the project background, an explanation about the lightning has been described. Project objectives, scopes and preliminary results from this project also discussed in this chapter. All the details for each section of the project have been discussed in this chapter.

#### **1.1** Introduction of the Project

Object detection is a hot research topic over the last two decades and the real-time processing speed are also important especially in automotive sector that involve pedestrian detection, vehicle detection and traffic signal in the surrounding. [1] The HOG algorithm is a feature extraction that commonly used for object detection. This project is using a heterogeneous Field programmable gate array FPGA/ARM processor and Xilinx SDSoC (Software-Defined System on Chip) for object detection. Xilinx Zynqa is a hybrid system and features a dual ARM Cortex-A9 processor and a FPGA processor that provides the adaptability of processing pace on a single chip.[2] In this project, evaluation on Zedboard with histogram of oriented gradients (HOG) algorithm for object detection will be analyze. For object classification, linear support vector machine (lnSVM) will be use. This system provides a more efficient implementation of HOG algorithm in FPGA, by considerably reducing the area, low cost, high computing speed, while maintaining accuracy compared to the original algorithm, portable and able to build in small cameras for surveillance applications. Finally, the project able to build for many applications of object detection including human detection, car detection etc.

#### **1.2 Problem Statement**

Object detection is one of the key problems in emerging self-driving car industry for example pedestrian and human detection, vehicle detection and traffic signal detection. However, object detection will need large memory capacity because of the size of input image issue. The high complexity of object detection needed longer processing time or even causing delay. [3] The size of network input is limited by the amount of memory; therefore, poor performance will also occur due to network latency. This will affect the accuracy and efficiency on object detection. On the same time, a graphics processing unit (GPU) is a computer chip which need higher cost, large area and large energy. Therefore, this project is implementing HOG algorithm in FPGA using SDSoC will reduce the problem and it is simplicity and mobility. [4]

#### **1.3 Project Objectives**

The objective of this project is:

- To implement of Histogram of Oriented Gradients HOG algorithms onto Fieldprogrammable gate array (FPGA) platform for object detection

- To evaluate and analyze the performance of SDSoC implemented HOG algorithm in terms of accuracy and speed.

#### 1.4 Scope of Work

The scope of work in this project is to study and evaluate FPGA implementation of HOG algorithm using SDSoC. The literature review of FPGA SDSoC and HOG algorithm from the journal using as a reference to get the information about this project. The final project is focus on object detection and classification. The algorithms will be coded by C programming language in Visual Studio 2017. First, study HOG algorithm and C programming language. Later, HOG algorithm in C programming language for HOG is implement and compile in software. After the code is successfully built, Xilinx SDSoC software platform is using to assess the performance of system when implemented HOG algorithm in terms of speed. The performance analysis will help on decision making for better performance. FPGA SDSoC Xilinx later is used to compiler for C code to hardware SD card booth file. SVM will be use as object classification for detected object. Besides, all the final data of performance is analyzed with frames per second (FPS). Preliminary Result will be obtaining and as a reference for following works.

#### **1.5 Expected Outcome**

The expected outcome for this project is implement of FPGA with HOG algorithm using SDSoC to detect object. FPGA SDSOC Xilinx is used for object detect. The object will be capture automatically when it detected the object. The rate for the frame per second of the image that capture for this project is expected to proceed up to 30 frame per second. All the images that captured by camera will be stored in local drive storage. At last, the inference time of object detect will be classified according to the design.

#### **1.6** Thesis structure

This dissertation contains five chapters:

Chapter 1 discusses more on the background, problem statement, objectives, scope of this project study and expected outcome. It gives an overview for the study. Chapter 2 explains the literature reviews about the computer vision, object detection, HOG, classifier SVM, FPGA SDSOC Xilinx and Xilinx Zedboard. Chapter 3 will cover the methodology and technique that will be implemented in this project. The approach for software implementation of Visual Studio 2017 software and Xilinx software and hardware implementation of Xilinx Zedboard are presented in this chapter. In chapter 4, the outcome of this project is discussed and presented on how the system performance. This section will likewise discuss the result acquired in a detailed manner. Chapter 5 presents the conclusion and future research. On the same time, the preference and the shortcoming of this project also discussed. This project can be improved in the future to make the object detection in FPGA more useful and functioning.

### **CHAPTER 2**

### **BACKGROUND STUDY**

#### 2.1 Introduction

This project required to do a lot of researches and finding for the facts and theory about the background for each section. This is because with this finding and facts, this project can be proceeding more smoothly and successful. This chapter explains in detail about the review for the related previous research paper and journals of computer vision, object detection, HOG, FPGA and SDSoC. Based on the idea methods and techniques that been used in those previous researches, the best solution was selected and applied to this project as the methodology.

#### 2.2 Overview

Although computer technology that related to computer vision technology and image processing have only exploded recently, it helps to detect object with several classes can classified it with a known class, such as cars, traffic signs, people or face in an image or video. [1] Today, many different interesting and useful detection algorithms or applications are proposed and implement according to desire application by different researchers or companies to achieve accurate and real time pedestrian detection. Human detection is an integral part of any video surveillance system with numerous applications in numerous computer vision fields. For example, automotive sector of robotics, Advanced driver-assistance systems (ADAS) developed and unmanned ground vehicles (UGV). [1], [3], [5]

#### 2.3 Feature descriptor

Numerous innovative feature descriptors have been present in recent decades, Feature descriptor use in computer vision for the visual features description of the content in image or video. [5] They describe elementary characteristics such as, the color, texture, shape or the motion, among others. [6] In 2001, GIST is the first scene recognition and a typically computed global image descriptor for scene classification purposes over the entire image shown in figure 2.1 is proposed by A. Olivia. [7]

Figure 2.1: The pipeline of GIST feature descriptor [7]

6