# DESIGN AND DEVELOPMENT OF AN ULTRA-LOW POWER CMOS VOLTAGE REGULATOR

BEE SHEI ER

This Report Is Submitted in Partial Fulfillment of Requirements for The Bachelor Degree of Electronic Engineering (Computer Engineering) With Honours

Faculty of Electronics and Computer Engineering

Universiti Teknikal Malaysia Melaka

June 2017

| UTEM<br>INIVERSITI TEKNIKAL MALAYSIA MELAKA | <b>UNIVERSTI TEKNIKAL MALAYSIA MELAKA</b><br>FAKULTI KEJURUTERAAN ELEKTRONIK DAN KEJURUTERAAN<br>KOMPUTER<br><b>BORANG PENGESAHAN STATUS LAPORAN</b>                                   |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                             | PROJEK SARJANA MUDA II                                                                                                                                                                 |  |

| Tajuk Project                               | : Design and Development of an Ultra-Low Power CMOS Voltage<br>Regulator for IoT Devices                                                                                               |  |

| Sesi Pengaiian                              | : 1 6 / 1 7                                                                                                                                                                            |  |

|                                             | n Laporan Projek Sarjana Muda ini disimpan di Perpustakaan dengan                                                                                                                      |  |

| syarat-syarat kegunaar                      | n seperti berikut:                                                                                                                                                                     |  |

| 2. Perpustakaan                             | h hakmilik Universiti Teknikal Malaysia Melaka.<br>dibenarkan membuat salinan untuk tujuan pengajian sahaja.<br>dibenarkan membuat salinan laporan ini sebagai bahan pertukaran antara |  |

| institusi penga                             |                                                                                                                                                                                        |  |

| 4. Sila tandakan                            |                                                                                                                                                                                        |  |

| T. Shu undukun                              |                                                                                                                                                                                        |  |

| SULIT*                                      | *(Mengandungi maklumat yang berdarjah keselamatan atau<br>kepentingan Malaysia seperti yang termaktub di dalam<br>AKTA RAHSIA RASMI 1972)                                              |  |

| TERHAD                                      | **( Mengandungi maklumat terhad yang telah ditentuk oleh<br>Organisasi/badan di mana penyelidikan dijalankan)                                                                          |  |

| TIDAK                                       | TERHAD                                                                                                                                                                                 |  |

|                                             | Disahkan oleh:                                                                                                                                                                         |  |

|                                             |                                                                                                                                                                                        |  |

| (TANDATANGAN P                              | ENULIS) (COP DAN TANDATANGAN PENYELIA)                                                                                                                                                 |  |

| Tarikh:                                     |                                                                                                                                                                                        |  |

C Universiti Teknikal Malaysia Melaka

"I hereby declare that the work in this project is my own except for summaries and quotations which have been duly acknowledge."

| Signature | :                          |

|-----------|----------------------------|

| Author    | : BEE SHEI ER              |

| Date      | :2 <sup>nd</sup> JUNE 2017 |

"I acknowledge that I have read this report and in my opinion this report is sufficient in term of scope and quality for the award of Bachelor of Electronic Engineering Electronic (Computer Engineering) with Honours"

| Signature         | :                           |

|-------------------|-----------------------------|

| Supervisor's Name | : Dr WONG YAN CHIEW         |

| Date              | : 2 <sup>nd</sup> JUNE 2017 |

For my lovely mother and father

#### ACKNOWLEDGEMENT

Upon the completion of this project, I would like to take this opportunity to express my sincere gratitude to Universiti Teknikal Malaysia Melaka (UTeM) for its conducive learning environment. Issac Newton once said: "If I have seen further, it is by standing on the shoulders of giants."Thank you the giant,UTeM.

For my beloved supervisor, Dr Wong Yan Chiew. A billion thanks to such a wonderful lecturer for all the unmeasurable guidance, constant advice, and great inspiration. I am also deeply grateful for the time Dr Wong spent to monitor on the progress of this project despite of her everyday busy schedule. I will not be able to complete this project without the support from Dr Wong through crucial moment. This project is truly a very remarkable experience for my enrolment in analogue integrated circuit design field. Thanks to my giant, Dr Wong.

I feel truly blessed by all the help provided by Mr Sreedharan Baskara Dass from Synopsys and master student of Dr Wong, Mohamad Khairul Bin Mohd Kamel. They are the strong technical support behind this project. They aided me through hard times using the design tool and make the completion of this project possible. They are never being impatient when tackling unexpected issues faced by me. Heartfelt appreciation for their kindness.

#### ABSTRACT

The Low Dropout Voltage Regulator (LDO) is widely used in the industry for wide range of applications such as smart phones, tablets, wearables. These LDOs are usually demanded to be ultra-low quiescent current. Low current consumption in LDO is favouring longevity of the battery life, such LDO become part of the powering solution for IoT devices that needed long sustain battery life at all times. The objectives of this work are focusing on realization of low current consumption that gives high power efficiency low dropout voltage regulator. The design of ultra-low power LDO in this work utilises the simple topology which comprising a bandgap reference, error amplifier, a feedback-voltage divider and a pass device. The design specification for current consumption of the LDO design is in micro ampere and the operating temperature of the LDO design is between -40 degrees Celsius to 125 degrees Celsius for the input range from 1.6 V to 5V. The LDO is designed and developed in Silterra 130nm technology by using Synopsys design tool and the performance of the LDO is analysed.

### ABSTRAK

Low Dropout Voltage Regulator (LDO) digunakan secara meluas dalam industri untuk pelbagai aplikasi seperti telefon pintar, tablet dan sebagainya. LDOs biasanya diperlukan dengan penggunaan arus yang sangat rendah. LDO yang memerlukan arus yang rendah adalah memihak umur panjang hayat bateri, LDO tersebut boleh dijadikan salah satu penyelesaian untuk aplikasi IOT yang perlu lama mengekalkan hayat bateri pada setiap masa. Objektif kerja ini memberi tumpuan kepada merealisasikan penggunaan arus rendah di LDO untuk memberikan kuasa tinggi kecekapan bagi LDO. Reka bentuk LDO di kerja ini mengaplikasikan topologi yang ringkas dan mudah. Topologi ini mengandungi *bandgap reference, error amplifier, feedback-voltage divider* dan *pass device*. Spesifikasi reka bentuk LDO tersebut adalah berada di mikro ampere dan suhu operasi reka bentuk LDO adalah antara -40 darjah Celsius hingga 125 darjah Celsius untuk kemasukan volt daripada 1.6 V untuk 5V. LDO tersebut dicipta dalam teknologi 130nm Silterra dengan menggunakan Synopsys dan prestasi LDO tersebut dianalisiskan.

## **TABLE OF CONTENT**

| CONTENT                   |                                   | PAGE |

|---------------------------|-----------------------------------|------|

|                           |                                   |      |

| PROJ                      | ECT TITLE                         | i    |

| CONF                      | <b>TIRMATION ON REPORT STATUS</b> | ii   |

| DECL                      | ARATION                           | iii  |

| SUPERVISOR'S CONFIRMATION |                                   | iv   |

| DEDECATION                |                                   | V    |

| ACKN                      | NOWLEDGEMENT                      | vi   |

| ABSTRACT                  |                                   | vii  |

| ABSTRAK                   |                                   | viii |

| LIST OF TABLE             |                                   | xiii |

| LIST OF FIGURE            |                                   | xiv  |

| LIST                      | OF ACRONYMS                       | xvi  |

| GLOS                      | SARY                              | xvii |

|                           |                                   |      |

| СНАР                      | TER I INTRODUCTION                | 1    |

|                           |                                   |      |

| 1.1                       | Project Background                | 1    |

| 1.2                       | Problem Statement                 | 2    |

| 1.3                       | Objective                         | 3    |

| 1.4                       | Scope Of Project                  | 3    |

C Universiti Teknikal Malaysia Melaka

## CHAPTER II LITERATURE REVIEW

5

Х

3

| 2.1 | Introduction                                           | 5  |

|-----|--------------------------------------------------------|----|

| 2.2 | Low Dropout Voltage Regulator                          | 5  |

| 2.3 | Architecture And Working Principle Of Ldo              | 6  |

| 2.4 | Design Consideration                                   | 8  |

|     | 2.4.1 Power Efficiency                                 | 8  |

|     | 2.4.2 Reference Voltage Design Consideration           | 9  |

| 2.5 | Low Dropout Voltage Regulator Topologies               | 14 |

|     | 2.5.1 Advanced Adaptive Biasing Compensation Technique | 15 |

|     | 2.5.2 Advanced Dynamic Push Pull Techniques            | 16 |

|     | 2.5.3 Slew Rate Enhancement Technique                  | 17 |

| 2.6 | Benchmarking Of Ldo Topology                           | 18 |

| 2.7 | Summary                                                | 20 |

### **CHAPTER III METHODOLOGY**

21

| 3.1 | Introduction                | 21 |

|-----|-----------------------------|----|

| 3.2 | Analogue Custom Design Flow | 21 |

| 3.3 | Ldo Schematic Design Flow   | 23 |

| 3.4 | Ldo Layout Design Flow      | 24 |

| 3.5 | Ldo Design Plan             | 26 |

| 3.6 | Summary                     | 27 |

### CHAPTER IV THE LDO DESIGN

| 4.1         | Introduction                                    | 28 |

|-------------|-------------------------------------------------|----|

| 4.2         | Bandgap Reference                               | 28 |

|             | 4.2.1 Design Specification Of Bandgap Reference | 29 |

|             | 4.2.2 Bandgap Reference Design                  | 29 |

| 4.3         | Error Amplifier                                 | 33 |

|             | 4.3.1 Design Specification Of Error Amplifier   | 34 |

|             | 4.3.2 Error Amplifier Design                    | 34 |

| 4.4         | Proposed Low Dropout Voltage Regulator Design   | 41 |

|             | 4.4.1 Feedback Resistors Design                 | 42 |

|             | 4.4.2 Ldo Design Parameters                     | 42 |

|             | 4.4.3 Ldo Layout Design                         | 43 |

| 4.5         | Summary                                         | 46 |

|             |                                                 |    |

|             |                                                 |    |

| СНАР        | TER V RESULT AND DISCUSSION                     | 47 |

|             |                                                 |    |

| 5.1         | Introduction                                    | 47 |

| 5.2         | Bandgap Reference Simulation                    | 47 |

| 5.3         | Error Amplifier Simulation                      | 49 |

| 5.4         | Final Ldo Design Simulation                     | 49 |

|             | 5.4.1 Steady State Analysis50                   |    |

|             | 5.4.2 Dynamic State Analysis52                  |    |

|             | 5.4.3 High Frequency Analysis54                 |    |

| 5.5         | Benchmarking                                    | 55 |

| 5.6 Summary |                                                 | 56 |

| СНАР       | TER VI CONCLUSION     | 58 |

|------------|-----------------------|----|

| 5.1        | Conclusion            | 58 |

| 5.2        | Future Recommendation | 59 |

|            |                       |    |

|            |                       |    |

| REFERENCES |                       | 60 |

| Appendix A |                       | 64 |

| Appendix B |                       | 70 |

## LIST OF TABLE

| Table 2.1 Benchmarking Of Low Power LDO          | 19 |

|--------------------------------------------------|----|

| Table 3.1 Design Specification                   | 26 |

| Table 4.1 Bandgap Reference Design Specification | 29 |

| Table 4.2 Error Amplifier Design Specification   | 34 |

| Table 4.3 Process Parameters For NMOS And PMOS   | 37 |

| Table 4.4 The Design Parameters                  | 43 |

| Table 5.1 The Benchmarking With Other Works      | 55 |

| Table 5.1 Summary Of Simulation Results          | 57 |

## LIST OF FIGURE

| Figure 2.1 Conventional LDO                                              | 7  |

|--------------------------------------------------------------------------|----|

| Figure 2.4 Bandgap Reference                                             | 10 |

| Figure 2.2 LDO With Advanced Adaptive Biasing Circuit                    | 15 |

| Figure 2.3 LDO With Advanced Dynamic Push-Pull Techniques                | 16 |

| Figure 2.4 LDO With Analogue Driver Using Slew Rate Enhancement Circuit  | 17 |

| Figure 3.1 Analogue Full Custom Design Flow                              | 23 |

| Figure 3.2 LDO Schematic Design Flow                                     | 24 |

| Figure 3.3 (a) LDO Layout Design Flow                                    | 25 |

| Figure 3.4 (b) LDO Layout Design Flow                                    | 25 |

| Figure 4.1 The Concept Of Bandgap Reference                              | 29 |

| Figure 4.2 CTAT Through A Diode                                          | 30 |

| Figure 4.3 PTAT Generation Through Multiple Diodes                       | 32 |

| Figure 4.4 Proposed Bandgap Reference                                    | 33 |

| Figure 4.5 Proposed Error Amplifier                                      | 35 |

| Figure 4.6 NMOS And PMOS Configuration                                   | 36 |

| Figure 4.7 Operating Point Analysis Setting                              | 36 |

| Figure 4.8 NMOS And PMOS DC Operating Points                             | 36 |

| Figure 4.9(a) Small Signal Model of Two Stage Op-Amp                     | 37 |

| Figure 4.9(b) Small Signal Model of Two Stage Op-Amp With Miller Theorem | 37 |

| Figure 4.10 Proposed LDO Design                                          | 42 |

| Figure 4.11 Layout Floor Plan For Bandgap Reference                      | 44 |

| Figure 4.11 DRC Errors                                                   | 45 |

| Figure 4.12 LVS Errors                                                   | 45 |

| Figure 4.2 Output Reference Voltage (Vref) Versus Temperature Variation  | 48 |

| Figure 4.3 Output Reference Voltage (Vref) Versus Supply Voltage Variation 48 |

|-------------------------------------------------------------------------------|

| Figure 4.3 Open Loop-Frequency Response Of Error Amplifier 49                 |

| Figure 4.5 (a) LDO Output Voltage Versus Input Voltage 50                     |

| Figure 4.5 (b) LDO Output Voltage Versus Input Voltage 51                     |

| Figure 4.6 LDO Output Voltage Versus Load Current Changes From 0Ao 40mA 52    |

| Figure 4.7 LDO Output Voltage Response And Input Voltage Changes Versus Time  |

|                                                                               |

| Figure 4.8 LDO Output Voltage Response And Load Current Changes Versus Time   |

|                                                                               |

| Figure 4.9 Power Supply Rejection Ratio (PSSR)55                              |

xv

## LIST OF ACRONYMS

| LDO  | Low Dropout Voltage Regulator         |

|------|---------------------------------------|

| PMOS | P-type Metal-Oxide-Semiconductor      |

| IoT  | Internet of Things                    |

| SoC  | System on Chip                        |

| РТАТ | Proportional to absolute temperature  |

| СТАТ | Complementary to absolute temperature |

| DC   | Direct Current                        |

| GBW  | Gain-Bandwidth product                |

| NMOS | N-type Metal-Oxide Semiconductor      |

| PMOS | P-type Metal-Oxide Semiconductor      |

| DRC  | Design Rule Check                     |

| LVS  | Layout Versus Schematic               |

| PSRR | Power Supply Rejection Ratio          |

| SR   | Slew Rate                             |

### GLOSSARY

**ERROR SIGNAL**

A voltage whose magnitude is proportional to the difference between an actual and desired position

### INPUT COMMON MODE RANGE

The average voltage of the inverting and non-inverting input

C Universiti Teknikal Malaysia Melaka

**CHAPTER I**

### INTRODUCTION

#### 1.1 PROJECT BACKGROUND

Power management for Internet of Things (IoT) devices is a challenging task. With the new data from Juniper Research reveals that the number of IoT devices will triple to over 38 billion units by 2020, the power solution for incoming wave of IoT devices in the future is becoming critical. IoT devices are always power-hungry as they require long sustain battery life to operate. It is almost impossible to have them wired and plugged in to power supply all the time as they are meant to work wirelessly. Therefore, to address this problem, scientists, and researchers study on the power solution for IoT devices such as utilizing ambient energy source and working on different battery technologies[1].

An ultra-low power low-dropout voltage regulator (LDO) can be part of the solution for power hungry IoT devices. It is a common block in power management system to regulate input voltage to a fix, steady and clean output voltage and prevent potential damage caused by fluctuated voltage as well as overloading A LDO is designed to be high power efficiency to prolong battery life for IoT devices. It is expected to consume less current and drains less power from the battery to achieve longevity in the battery life.

#### **1.2 PROBLEM STATEMENT**

The power solution for IoT devices become significantly important especially the feature of the device drains battery very fast. This leads to the needs of frequent replacement of the battery in the device. The use of rechargeable battery seems to be a good option to avoid frequent replacement of battery but it has its own limitation as well. The rechargeable battery usually exhausts after a few hundred charge cycles and it will need a replacement eventually. Therefore, a low power LDO is designed. It consumes less current and prolong battery life in a way that less power is drain from the battery for the functionality of the LDO. However, a LDO requires low quiescent current in realizing a low power LDO design. This cannot be achieved with a conventional LDO due to the high quiescent current in conventional LDO. Moreover, the performance of the LDO must be compromised for a low quiescent current. The low quiescent deteriorates the driving capability of the pass device and causes poor performance of the LDO during changing of output load. Any buffer or driver that is added in front of the pass device will increase the driving force at the gate of the pass device but at the same time, it consumes quiescent current in the LDO. Due to this matter, the power consumption of the LDO is increased and leading to poor efficiency of the LDO [2].

#### **1.3 OBJECTIVE**

The main objectives of this project are:

- I. Identify the key design parameters in low power CMOS LDO regulator design

- II. To propose a new design methodology for high efficient low power CMOS LDO regulator

- III. To design and develop the high efficiency low CMOS LDO regulator

- IV. To verify the proposed methodology theoretically and analytically through modelling

#### **1.4 SCOPE OF PROJECT**

The design of the proposed LDO circuit is consisting of a bandgap reference, error amplifier and a pass device. A low power LDO topology is investigated and utilized in this proposed work to achieve low quiescent current and leading to high power efficiency design of LDO. The design considerations of each building blocks in the LDO circuit is considered to realize an ultra-low power LDO design. The LDO is designed and simulated using Synopsys tool. The LDO design will be for the use of device level in an IoT device. Finally, the design is completed until layout design that is ready for fabrication.

#### **1.5 THESIS STRUCTURE**

The dissertation is organized as follows:

I. Chapter I Introduction

This chapter presents the background study, problem statement, objectives as well as the scope of the study. The introduction of this project provides an overview of the proposed work.

II. Chapter II Literature Review

C) Universiti Teknikal Malaysia Melaka

This chapter presents the architecture and working principle of lowdropout voltage regulator (LDO). Furthermore, a discussion on various low-dropout voltage regulator topologies from various research papers, the design consideration of LDO and bench marking will be included in this chapter.

#### III. Chapter III Methodology

The full design flow of analogue design and the analogue design rules are presented in this chapter. The design specification of this project is also presented in this chapter.

#### IV. Chapter IV The LDO Design

This chapter presents the schematic, layout of the proposed work and the detail working on how to design the LDO. This chapter is consisting the design specification. The final LDO design with all the parameters is also displayed in this chapter. At the end of this chapter, the layout design of the final LDO design is presented.

#### V. Chapter V Result and Discussion

This chapter will present the simulation analysis and discussion. The analysis and discussion is involving the bandgap reference, error. The bandgap reference simulation will verify the operating temperature followed by error amplifier simulation that verify the open loop frequency response of the error amplifier. The final LDO simulation is analysed for its steady state analysis and dynamic state analysis as well as high frequency analysis. The discussion is about the result achieved. amplifier and the final LDO design.

#### VI. Chapter VI Conclusion

This chapter summarizes the findings from overall results and discussion of the project. The future recommendation is also presented at the end of this chapter.

CHAPTER II

#### LITERATURE REVIEW

#### 2.1 INTRODUCTION

This chapter presents an overview of the low-dropout voltage regulator (LDO). It also includes the architecture and working principle of a conventional low-dropout voltage regulator (LDO) and a review of various low-dropout voltage regulator topologies. The design consideration and bench marking of LDO will be presented in the following sections of this chapter.

#### 2.2 LOW DROPOUT VOLTAGE REGULATOR

Low-dropout voltage regulator (LDO) is a type of linear voltage regulator and like any other voltage regulator, it regulates input voltage to give a fix, steady and clean output voltage. It is different from other linear voltage regulator in term of its drop-out voltage. LDO has low-dropout voltage which typically lower than 1V while

the drop-out voltage means the minimum differential voltage between the output and input at the instance it stops to regulate [3]. In other words, the low dropout voltage can be understood as the low input to output difference. When the difference of input and output is low, a lower value of minimum input voltage is required by the LDO to provide the fixed amount of output voltage Thus, the low drop-out nature of LDO is said to be appropriate for portable devices as the input supply voltage of portable devices will not be high [4].

LDO can be categorized as low power LDO or high power LDO. These two types of LDO are different in terms of their output current. Low power LDO are those consuming low current within themselves when no load is applied. This type of current is known as quiescent current. It is one of the parameter to refer as to compare how low power is the LDO. Most portable applications require low power LDOs because the battery supply is limited unlike power supply from the socket. Low power and low quiescent current flow is highly demand in portable electronics industry for long battery life and increased battery efficiency. On the other hand, high power LDO consumes higher current which typically greater than 1A. It is commonly used in industrial and automotive applications.

#### 2.3 ARCHITECTURE AND WORKING PRINCIPLE OF LDO

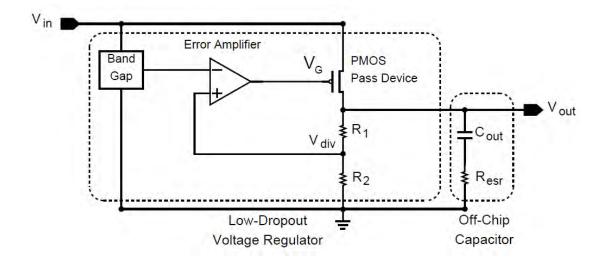

The basic blocks of a conventional LDO include the bandgap, error amplifier, pass device of PMOS, a resistive feedback network which made up of two feedback resistors R1 and R2, a decoupled capacitor  $C_{out}$  with a parasitic resistor  $R_{esr}$  as shown in Figure 2.1.

Figure 2.1 Conventional LDO

A LDO needs a voltage reference to operate. The voltage reference is used to compare with the scale down voltage to produce fix and steady required regulated voltage. The bandgap plays an important role in establishing the voltage reference for LDO. Since both bandgap and LDO have the same function of providing fix and steady output voltage, therefore it is of utmost importance to differentiate these two components. A LDO is required to provide steady current and voltage to numbers of blocks while a bandgap must be able to provide steady voltage only to a single block like in a LDO.

The error amplifier in the LDO compares the bandgap reference and the scaled down output voltage, it also controls the current flow through the pass device to meet the output requirement. Pass device is a PMOS with common source connection that places between input and output voltage. It is an important part of the LDO and occupied almost half of the LDO design area in the chip. This device is huge because it bears a big responsibility to drive the current flow to the load. Feedback resistors R1 and R2 are a voltage divider that scale down the output voltage to a suitable value for error amplifier to compare with bandgap reference. The scaled down voltage is a negative feedback to the positive terminal of the error amplifier while the bandgap feds to the negative terminal of the amplifier[5]. Lastly, a large off-chip capacitor is needed at the output of the LDO to improve the stability. [3], [6]