# HARMONIC MINIMIZATION OF A SINGLE PHASE CASCADED H-BRIDGE MULTILEVEL INVERTER

# MUHAMMAD SYAHIR AFIF BIN ABDUL RAHMAN

# BACHELOR OF ELECTRICAL ENGINEERING

# (INDUSTRIAL POWER)

# UNIVERSITI TEKNIKAL MALAYSIA MELAKA

# DECLARATION

# I declare that this thesis entitled "HARMONICS MINIMIZATION OF A SINGLE PHASE CASCADED H-BRIDGE MULTILEVEL INVERTER" is the result of my own

research except as cited in the references.

| Signatur | e:                                      |

|----------|-----------------------------------------|

| Name     | : Muhammad Syahir Afif Bin Abdul Rahman |

| Date     | : 15 June 2017                          |

## APPROVAL

I hereby declare that I have read through this thesis and found that is comply the partial fulfillment for awarding the degree of Bachelor of Electrical Engineering (Industrial Power)

Signature : ..... Name : Prof. Madya. Ir. Dr. Rosli Bin Omar Date : 15 June 2017

## ACKNOWLEDGEMENT

In the name of Allah, The Most Beneficent, The Most Gracious and The Most Merciful. It is deepest sense gratitude of the Almighty that give me strength and ability to complete this Final Year Project report.

A special appreciation I give to my final year project supervisor, Prof. Madya. Ir. Dr. Rosli Bin Omar, whose give me a valuable guidance, lessons, support, and helped me to coordinate my project especially in writing this report.

Special thanks go to my family for their moral support to me and comfort me when I was in distress while to complete this project. Besides that, I would also like to acknowledge with much appreciation to all my friends who help and support me in order to complete my Final Year Project.

Furthermore I would also like to express my gratitude to staff of Univesiti Teknikal Malaysia Melaka (UTeM), who gave me the permission to use all required equipment and necessary materials in laboratory to complete my Final Year Project.

## ABSTRACT

This project represent the research of harmonic minimization of a single phase cascaded H-bridge multilevel inverter (CHB-MLI). Multilevel inverter is used to combine a desired single or three-phase voltage waveform and also to minimize the harmonics in the electrical system. This project use cascaded H-bridge (CHB) topology due to least number of components use, output voltage level are doubled, and easy to controlled compared with diode clamp (DC) and flying capacitor (FC) topology. This research use three and five levels cascaded H-bridge multilevel inverter based on Newton-Raphson technique controller by using MATLAB/SIMULINK in order to reduce the harmonic in electrical system. The value of total harmonic distortion (THD) has been obtained based on the simulation design of three and five levels CHB-MLI.

Next, prototypes of single phase three and five level CHB-MLI based on Newton-Raphson technique controller using DSPTMS320F2812 has been analyzed. The parameter based on simulation has been used in order to analyze the proposed prototypes of CHB-MLI. The source codes has been created and embedded into DSPTMS320F2812 in order to operate the prototypes of CHB-MLI. The modulation index that has been used in this research were 0.84 for optimization and 0.68 for non-optimization. Based on this research, the output voltage of total harmonic distortion (THD<sub>V</sub>) and output current of total harmonic distortion (THDi) content in the CHB-MLI has been analyzed. The performance of the proposed system was compared between the simulation and experimental results for optimization and non-optimization technique. Furthermore, the simulation and experimental results demonstrate which one of the proposed CHB-MLI has better performance in minimizing the harmonics contents. The waveforms of output voltage and current were smooth and low harmonic contents which suitable to be used in photovoltaic (PV) application.

#### ABSTRAK

Projek ini membentangkan kajian tentang pengurangan harmonik satu fasa penyongsang bertingkat cascaded H-bridge (CHB-MLI). Penyongsang bertingkat digunakan untuk menggabungkan satu atau tiga fasa gelombang voltan yang dikehendaki dan juga untuk mengurangkan harmonik dalam sistem elektrik. Projek ini menggunakan cascaded H-bridge (CHB) kerana bilangan komponen yang digunakan adalah sedikit, tahap voltan output adalah dua kali ganda, dan mudah untuk dikawal berbanding kapasitor terbang (FC) dan diod diapit (DC) topologi. Kajian ini menggunakan tiga dan lima tingkat penongsang bertingkat cascaded H-bridge berdasarkan kawalan teknik Newton-Raphson dengan menggunakan MATLAB/SIMULINK bertujuan untuk mengurangkan harmonik dalam sistem elektrik. Nilai jumlah herotan harmonic (THD) telah diperolehi berdasarkan reka bentuk simulasi tiga dan lima tingkat CHB-MLI.

Seterusnya, prototaip satu fasa tiga dan lima tingkat CHB-MLI berdasarkan kawalan Newton-Raphson teknik menggunakan DSPTMS320F2812 telah dianalisis. Parameter berdasarkan simulasi telah digunakan bertujuan untuk menganalisis prototaip CHB-MLI. Kod sumber telah dicipta dan ditanam ke dalam DSPTMS320F2812 untuk menjalankan prototaip CHB-MLI. Indeks modulasi yang telah digunakan dalam kajian ini ialah 0.84 untuk pengoptimuman dan 0.68 untuk bukan pengoptimuman Berdasarkan kajian ini, voltan keluaran jumlah herotan harmonik (THD<sub>v</sub>) dan arus keluaran jumlah herotan harmonik (THD<sub>v</sub>) dan arus keluaran jumlah herotan harmonik (THDi) dalam CHB-MLI telah dianalisis. Prestasi sistem yang dicadangkan telah dibandingkan antara simulasi dan keputusan eksperimen untuk teknik pengoptimuman dan bukan pengoptimuman. Tambahan pula, keputusan simulasi dan eksperimen menunjukkan CHB-MLI yang dicadangkan yang mana satu mempunyai prestasi yang lebih baik dalam mengurangkan kandungan harmonik. Bentuk gelombang voltan dan arus keluaran adalah licin dan rendah kandungan harmonik yang sesuai untuk digunakan dalam aplikasi photovoltaic (PV).

# **TABLE OF CONTENTS**

| CHAPTER | TITLE                                         | PAGE |

|---------|-----------------------------------------------|------|

|         | ACKNOWLEDGEMENT                               | i    |

|         | ABSTRACT                                      | ii   |

|         | TABLE OF CONTENTS                             | iv   |

|         | LIST OF TABLES                                | vii  |

|         | LIST OF FIGURES                               | viii |

| 1       | INTRODUCTION                                  |      |

|         | 1.1 Project Background                        | 1    |

|         | 1.2 Problem Statement                         | 2    |

|         | 1.3 Objectives                                | 3    |

|         | 1.4 Project Scope                             | 3    |

|         | 1.5 Expected project outcome                  | 4    |

| 2       | LITREATURE REVIEW                             |      |

|         | 2.1 Introduction                              | 5    |

|         | 2.2 The Concept of Inverter                   | 5    |

|         | 2.2.1 Types of Inverter Ouput Waveform        | 7    |

|         | 2.3 The Concept of Multilevel Inverter        | 9    |

|         | 2.3.1 Neutral Point Clamp Multilevel Inverter | 9    |

|         | 2.3.2 Flying Capacitor Multilevel Inverter    | 11   |

| 2.3.2 Frying Capacitor Multilever inverter    | 11 |

|-----------------------------------------------|----|

| 2.3.3 Cascaded H-Bridge Multilevel Inverter   | 12 |

| 2.4 Description of Harmonics                  | 14 |

| 2.4.1 Effect of Harmonics Distortion          | 15 |

| 2.4.2 Harmonic Fundamental Equation           | 15 |

| 2.5 Control Technique for Multilevel Inverter |    |

2.5.1 Sinusoidal Pulse Width Modulation 16

| 2.5.2 Space Vector Pulse Width Modulation  | 17 |

|--------------------------------------------|----|

| 2.5.3 Selective Harmonic Elimination Pulse | 17 |

| Width Modulation                           |    |

| 2.5.4 Newton-Raphson Technique             | 18 |

| 2.6 The Concept of DSPTMS320F2812          |    |

| 2.7 Summary and discussion of the review   |    |

|                                            |    |

**RESEARCH METHODOLOGY**

| 3.1 Introduction              | on of the Methods Utilized                      | 20 |

|-------------------------------|-------------------------------------------------|----|

| 3.2 Flow Chart of the project |                                                 | 21 |

| 3.3 Discussion                | n on selected design using MATLAB/SIMULINK      | 23 |

| 3.3.1                         | Simulation of Optimization three-levels         |    |

|                               | cascaded H-bridge multilevel inverter by        |    |

|                               | using MATLAB/SIMULINK                           | 23 |

| 3.3.2                         | The proposed Switching Scheme for three-levels  |    |

|                               | cascaded H-bridge multilevel inverter           | 25 |

| 3.3.3                         | The Switching Block design for three-levels     |    |

|                               | cascaded H-bridge multilevel inverter by        |    |

|                               | using MATLAB/SIMULINK                           | 26 |

| 3.3.4                         | Simulation of Optimization five-levels cascaded |    |

|                               | H-bridge multilevel inverter by using           |    |

|                               | MATLAB/SIMULINK                                 | 27 |

| 3.3.5                         | The proposed Switching Scheme for five-levels   |    |

|                               | cascaded H-bridge multilevel inverter           | 29 |

| 3.3.6                         | The Switching Block design for five-levels      |    |

|                               | cascaded H-bridge multilevel inverter by        |    |

|                               | using MATLAB/SIMULINK                           | 30 |

| 3.3.7                         | Simulation of Non-Optimization three-levels     |    |

|                               | cascaded H-bridge multilevel inverter           |    |

|                               | by using MATLAB/SIMULINK                        | 31 |

| 3.3.8                         | Simulation of Non-Optimization five-levels      |    |

|                               | cascaded H-bridge multilevel inverter           |    |

|                               | by using MATLAB/SIMULINK                        | 32 |

3

| 3.4  | 4 Mathematical Technique of Switching by using |                                                  |    |

|------|------------------------------------------------|--------------------------------------------------|----|

|      | Newto                                          | on-Raphson                                       | 33 |

| 3.5  | Discus                                         | ssion on the Proposed Hardware Design            | 36 |

|      | 3.5.1                                          | Gate Drive for IGBT Switching                    | 36 |

|      | 3.5.2                                          | The Hardware for Single Phase Three Level        |    |

|      |                                                | and Five CHB-MLI                                 | 37 |

|      | 3.5.3                                          | Hardware Utilization Based on Digital            |    |

|      |                                                | Signal Processor (DSP)                           | 39 |

|      | 3.5.4                                          | Experimental Prototype Circuits of Three         |    |

|      |                                                | and Five Level CHB-MLI                           | 40 |

| 3.6  | Summ                                           | ary of the Method Use                            | 41 |

| RESU | LTS A                                          | ND DISCUSSION                                    |    |

| 4.1  | Introd                                         | uction to Project Results                        | 42 |

| 4.2  | Simula                                         | ation of a Single Phase CHB-MLI for Five         |    |

|      | and Three level                                |                                                  |    |

|      | 4.2.1                                          | Simulation Results for Optimization of a         |    |

|      |                                                | Single Phase Three-Level CHB-MLI design          |    |

|      |                                                | with $MI = 0.84$                                 | 43 |

|      | 4.2.2                                          | Simulation Results for Non-Optimization of a     |    |

|      |                                                | Single Phase Three-Level CHB-MLI design          |    |

|      |                                                | with $MI = 0.68$                                 | 47 |

|      | 4.2.3                                          | Simulation Results for Optimization of a         |    |

|      |                                                | Single Phase Five-Level CHB-MLI design           |    |

|      |                                                | with $MI = 0.84$                                 | 51 |

|      | 4.2.4                                          | Simulation Results for Non-Optimization of a     |    |

|      |                                                | Single Phase Five-Level CHB-MLI design           |    |

|      |                                                | with MI = 0.68                                   | 55 |

| 4.3  | Experi                                         | imental Hardware Results of a Single Phase       |    |

|      | Three-                                         | level CHB-MLI with Different Value of MI         | 59 |

|      | 4.3.1                                          | Experimental Results for Optimization Single     |    |

|      |                                                | Phase Three-level CHB-MLI with $(MI = 0.84)$     | 60 |

|      | 4.3.2                                          | Experimental Results for Non-Optimization Single |    |

|      |                                                | Phase Three-level CHB-MLI with $(MI = 0.68)$     | 63 |

|      |                                                |                                                  |    |

4

vi

|   | APPE | NDIX   |                                                  | 80 |

|---|------|--------|--------------------------------------------------|----|

|   | REFF | CRENC  | ES                                               | 78 |

| 5 | CON  | CLUSI  | ON AND RECOMMENDATION                            | 76 |

|   | 4.5  | Summ   | ary of the Results                               | 75 |

|   |      | CHB-   | MLI with Difference Value of MI                  | 74 |

|   |      | Exper  | imental Results of Three and Five level          |    |

|   | 4.4  | Perfor | mance Comparison of Simulation and               |    |

|   |      |        | Phase Five-Level CHB-MLI with $(MI = 0.68)$      | 70 |

|   |      | 4.3.4  | Experimental Results for Non-Optimization Single | e  |

|   |      |        | Phase Five-Level CHB-MLI with $(MI = 0.84)$      | 66 |

|   |      | 4.3.3  | Experimental Results for Optimization Single     |    |

# LIST OF TABLES

| TABLE | TITLE                                                            | PAGE |

|-------|------------------------------------------------------------------|------|

| 2.1   | Table of switching state for three-level NPC topology            | 10   |

| 2.2   | Table of switching state for three-level FC multilevel inverter  | 12   |

| 2.3   | Table of switching state for five-level CHB multilevel inverter  | 13   |

| 3.1   | The values of switching angles based on modulation index         | 35   |

| 4.1   | Performance comparison of simulation and experimental results of |      |

|       | three and five level CHB-MLI with different value of MI          | 74   |

# LIST OF FIGURES

## FIGURE

#### TITLE

## PAGE

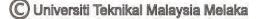

| 1.1  | Single phase Cascaded H-bridge Multilevel Inverter            | 2  |

|------|---------------------------------------------------------------|----|

| 2.1  | Basic connection of cascaded H-bridge inverter                | 6  |

| 2.2  | Inverter output waveforms                                     | 8  |

| 2.3  | Three -level Neutral Point Clamped topology                   | 10 |

| 2.4  | Three-level Flying Capacitor multilevel inverter              | 11 |

| 2.5  | Five-level Cascaded H-Bridge multilevel inverter              | 12 |

| 2.6  | Divided fundamental and harmonic waveforms                    | 14 |

| 3.1  | Flow Chart of the project                                     | 22 |

| 3.2  | Modeling of optimize single phase three-level cascaded        |    |

|      | H-bridge multilevel inverter by using MATLAB/SIMULINK         | 23 |

| 3.3  | Scope for three-level cascaded H-bridge multilevel inverter   |    |

|      | by using MATLAB/SIMULINK                                      | 24 |

| 3.4  | Switching design for a three-level CHB-MLI by using           |    |

|      | MATLAB/SIMULINK                                               | 25 |

| 3.5  | Pulse generator block connected to switching signal in        |    |

|      | three level CHB-MLI by using MATLAB/SIMULINK                  | 26 |

| 3.6  | Five-level cascaded H-bridge multilevel inverter design       |    |

|      | using MATLAB/SIMULINK                                         | 27 |

| 3.7  | Scope for five-level cascaded H-bridge multilevel inverter    |    |

|      | by using MATLAB/SIMULINK                                      | 28 |

| 3.8  | Switching design for a three-level CHB-MLI by using           |    |

|      | MATLAB/SIMULINK                                               | 29 |

| 3.9  | Pulse generator block connected to switching signal in        |    |

|      | five level CHB-MLI by using MATLAB/SIMULINK                   | 30 |

| 3.10 | Modeling of non-optimize single phase three-level cascaded    |    |

|      | H-bridge multilevel inverter by using MATLAB/SIMULINK         | 31 |

| 3.11 | Modeling of non-optimization single phase five-level cascaded |    |

|      | H-bridge multilevel inverter by using MATLAB/SIMULINK         | 32 |

| 3.12 | The prototype of gate drive connected with CHB-MLI            | 36 |

| 3.13    | The design of a single phase three-level CHB-MLI              | 38 |

|---------|---------------------------------------------------------------|----|

| 3.14    | The design of a single phase five-level CHB-MLI               | 38 |

| 3.15    | Digital Signal Processor (DSP) TMS320F2812                    | 39 |

| 3.16    | Set up of experimental prototype circuit of for three level   |    |

|         | CHB-MLI                                                       | 40 |

| 3.17    | Set up of experimental prototype circuit for five level       |    |

|         | CHB-MLI                                                       | 41 |

| 4.1     | Switching waveform for optimization three-level CHB-MLI       | 44 |

| 4.2     | Output voltage waveform of optimization single phase          |    |

|         | three level CHB-MLI                                           | 45 |

| 4.3     | Harmonic spectrum for voltage output waveform of optimization |    |

|         | three level CHB-MLI                                           | 45 |

| 4.4     | Output current waveform of optimization single phase          |    |

|         | three level CHB-MLI                                           | 46 |

| 4.5     | Harmonic spectrum for current output waveform of optimization |    |

|         | three level CHB-MLI                                           | 47 |

| 4.6     | Switching waveform for non-optimization three-level           |    |

|         | CHB-MLI                                                       | 48 |

| 4.7     | Output voltage waveform of non-optimization three level       |    |

|         | CHB-MLI                                                       | 49 |

| 4.8     | Harmonic spectrum for voltage output waveform non-            |    |

|         | optimization three level CHB-MLI                              | 49 |

| 4.9     | Output current waveform of non-optimization three level       |    |

|         | CHB-MLI                                                       | 50 |

| 4.10    | Harmonic spectrum for current output waveform non-            |    |

|         | optimization three level CHB-MLI                              | 50 |

| 4.11(a) | Upper switching waveform for optimization five-level          |    |

|         | CHB-MLI                                                       | 51 |

| 4.11(b) | Lower switching waveform for optimization five-level          |    |

|         | CHB-MLI                                                       | 52 |

| 4.12    | Output voltage waveform of optimization five level            |    |

|         | CHB-MLI                                                       | 53 |

| 4.13    | Harmonic spectrum of optimization voltage output waveform     |    |

|---------|---------------------------------------------------------------|----|

|         | for five level CHB-MLI                                        | 53 |

| 4.14    | Output current waveform of optimization five level CHB-MLI    | 54 |

| 4.15    | Harmonic spectrum of optimization current output waveform for |    |

|         | five level CHB-MLI                                            | 54 |

| 4.16(a) | Upper switching waveform for non-optimization five-level      |    |

|         | CHB-MLI                                                       | 55 |

| 4.16(b) | Lower switching waveform for non-optimization five-level      |    |

|         | CHB-MLI                                                       | 56 |

| 4.17    | Output voltage waveform of non-optimization five level        |    |

|         | CHB-MLI                                                       | 57 |

| 4.18    | Harmonic spectrum of non-optimization voltage output waveform | 1  |

|         | for five level CHB-MLI                                        | 57 |

| 4.19    | Output current waveform of non-optimization five level        |    |

|         | CHB-MLI                                                       | 58 |

| 4.20    | Harmonic spectrum of non-optimization output current waveform | ı  |

|         | for five level CHB-MLI                                        | 58 |

| 4.21    | Switching waveform for optimization three- level CHB-MLI      | 60 |

| 4.22    | Output voltage waveform for optimization of three-level       |    |

|         | CHB-MLI                                                       | 61 |

| 4,23    | Harmonic spectrum of voltage output waveform for optimization |    |

|         | of three-level CHB-MLI                                        | 61 |

| 4.24    | Current output waveform for optimization of three-level       |    |

|         | CHB-MLI                                                       | 62 |

| 4.25    | Harmonic spectrum of current output waveform for optimization |    |

|         | of three-level CHB-MLI                                        | 62 |

| 4.26    | Switching waveform for non-optimization three- level CHB-MLI  | 63 |

| 4.27    | Output voltage waveform for non-optimization of three-level   |    |

|         | CHB-MLI                                                       | 64 |

| 4.28    | Harmonic spectrum of voltage output waveform for non-         |    |

|         | optimization three-level CHB-MLI                              | 64 |

| 4.29    | Current output waveform for non-optimization of three-level   |    |

|         | CHB-MLI                                                       | 65 |

| 4.30    | Harmonic spectrum of the current output waveform for non-     |    |

|---------|---------------------------------------------------------------|----|

|         | optimization of three-level CHB-MLI                           | 65 |

| 4.31(a) | Upper switching waveform for optimization of five-level       |    |

|         | CHB-MLI                                                       | 66 |

| 4.31(b) | Lower switching waveform for optimization of five-level       |    |

|         | CHB-MLI                                                       | 67 |

| 4.32    | Output voltage waveform for optimization of five-level        |    |

|         | CHB-MLI                                                       | 67 |

| 4.33    | Harmonic spectrum of voltage output waveform for optimization |    |

|         | five-level CHB-MLI                                            | 68 |

| 4.34    | Current and voltage output waveform for optimization of       |    |

|         | five-level CHB-MLI                                            | 69 |

| 4.35    | Harmonic spectrum of the current output waveform for          |    |

|         | optimization of five-level CHB-MLI                            | 69 |

| 4.36(a) | Upper switching waveform for non-optimization of five-level   |    |

|         | CHB-MLI                                                       | 70 |

| 4.36(b) | Lower switching waveform for non-optimization of five-level   |    |

|         | CHB-MLI                                                       | 71 |

| 4.37    | Output voltage waveform for non-optimization of five-level    |    |

|         | CHB-MLI                                                       | 71 |

| 4.38    | Harmonic spectrum of voltage output waveform for non-         |    |

|         | optimization five-level CHB-MLI                               | 72 |

| 4.39    | Current and voltage output waveform for non-optimization of   |    |

|         | five-level CHB-MLI                                            | 73 |

| 4.40    | Harmonic spectrum of the current output waveform for non-     |    |

|         | optimization of five-level CHB-MLI                            | 73 |

#### **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Project Background

In this chapter, a single-phase Cascaded H-bridge Multilevel Inverter (CHB-MLI) has been used to alternating current (AC) voltage waveform of the inverter output. For the ordinary inverter, the process of energy conversion is to convert Direct Current (DC) to Alternating Current (AC) [1]. The function of inverter is opposite the function of rectifier. The upgrade of inverter that nowadays used is called multilevel inverters. Multilevel inverter have more advantages compared to ordinary inverter. Multilevel inverters was invented with many levels that show the highest level give the best output. The main function for the multilevel inverter is to combine the desired output voltage waveform from several steps of voltage. There are three types of multilevel inverters topology that commonly used such as Cascaded H-Bridge Multilevel Inverter (CHB-MLI), Diode Clamp Multilevel Inverters (DC-MLI), and Flying Capacitor Multilevel Inverters (FC-MLI). This project use CHB-MLI in order to reduce harmonic because it easy to control and also the output voltages level are doubled the number of sources.

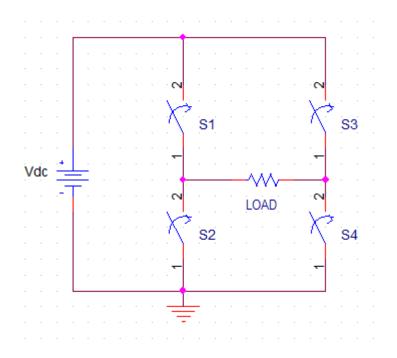

In this project, Cascaded H-bridge multilevel inverter (CHB-MLI) has been used to provide a sinusoidal output voltage. In single phase CHB-MLI, it uses several H-bridge inverters connected in series which each phase is connected to single dc source. Each level generates three voltage outputs which are positive, negative and zero [2]. The inverter will remain ON when two switches with the opposite positions will remain ON. When all the inverters switch ON or OFF, the inverter will turn OFF. Based on the Figure 1, when the S1 and S4 is ON, the inverter will ON. Same with when S2 and S3 is ON, inverter will ON. Inverter will OFF when S1, S2, S3 and S4 is ON or OFF.

Figure 1.1: Single phase Cascaded H-bridge Multilevel Inverter

#### **1.2** Problem Statement

Cascaded H-bridge multilevel inverter (CHB-MLI) is based on the series connection of the power cell and several H-bridge inverters to provide a sinusoidal output voltage. The main problem that always occurs in power electronics device is the harmonic content. In order to minimize the harmonic distortion, the switching angle has been used in the CHB-MLI for controlling the output voltage and current [3]. The major target is to decrease the total harmonic distortion (THD) in electronic devices. THD is the summation of all harmonic components of the voltage or current waveform that measured in a percentage. The higher the percentage of output voltage THD, the higher distortion that is present on the mains signal [4].

There are some control technique methods frequently used which are pulse width modulation (PWM), selective harmonic elimination (SHE), space vector pulse width modulation (SVPWM), and sinusoidal pulse width modulation (SPWM). The types of controllers cannot totally remove the harmonics because they cannot be applied in multilevel inverter with differing DC voltages. Thus, Newton-Raphson technique controller is the most suitable control technique in order to reduce the harmonic using CHB-MLI.

## 1.3 Objectives

The objective of this project are:

- To study types of multilevel inverter topologies that mainly used to minimize harmonic distortion.

- To investigate the harmonic minimization of optimization and non-optimization three-level and five-level single-phase Cascaded H-bridge Multilevel Inverter (CHB-MLI) by using MATLAB/SIMULINK.

- To analyse a prototype of a single phase cascaded H-bridge multilevel inverter (CHB-MLI) based on Newton Raphson technique controller using DSP TMS320F2812.

- To compare the differences of THD between simulation and hardware of three level and five level CHB-MLI.

## 1.4 Project Scope

Based on this research, there are three main types of multilevel inverter topologies which are Neutral Point Clamped (NPC), Flying Capacitor (FC) and Cascaded H-bridge (CHB). The main focus in this project is to simulate the proposed model and also to analyse the THD content of a single phase cascaded H-bridge multilevel inverter (CHB-MLI). Next, this project scope is also to analyse a prototype of a single phase CHB-MLI based on Newton Raphson technique controller using DSP TMS320F2812. The parameter from simulation will be used to analyze a prototype of a single phase cascaded H-bridge using DSP TMS320F2812 and the coding will be created using C++ programming. The proposed coding will be embedded with DSP TMS320F2812 in order to carry out the inverter.

## 1.5 Expected Project Outcome

In this study, this project propose is to minimize harmonic using three phase and five level cascaded H-bridge multilevel inverter (CHB-MLI) prototype based on simulation circuit design. Meanwhile, the prototype of a single phase CHB-MLI has been used in order to analyse the THD value. The comparison of THD between three level and five level CHB-MLI has been done to know which output level of multilevel inverter is better to reduce the harmonics.

#### **CHAPTER 2**

#### LITREATURE REVIEW

#### 2.1 Introduction

In this study, a single phase cascaded H-bridge multilevel inverter (CHB-MLI) has been used to produce alternating current (AC) voltage waveform of the inverter output. There are three types of multilevel inverter topologies which are Diode Clamp (DC), Flying Capacitor (FC), and Cascaded H-Bridge (CHB) multilevel inverter. There are three types of inverter output waveform that commonly utilized which are square wave, modified sine wave and sine wave. Therefore, this study is to minimize the harmonic of a single phase cascaded H-bridge multilevel inverter by analysing its regulated output voltage.

## 2.2 The Concept of Inverter

Inverter are a device or electronic component which is provides AC load voltage from a DC voltage source. There are many types of semi-conductor switching that can be used to control the operation of the inverter such as bipolar junction transistor (BJT), metal oxide semiconductor field effect transistor (MOSFET), insulated-gate bipolar transistor (IGBT) and gate turn off thyristor (GTO). A single phase inverter usually contain two or four switches that consist in half-bridge or full-bridge topologies [1].

Figure 2.1: Basic connection of cascaded H-bridge inverter

Based on figure 2.1, the voltage source supply is a DC source which is 240Vdc. The purpose of DC/AC power inverter is to convert the DC power supplied to AC power supplied which is usually operate at frequency from 50Hz to 60Hz. Each switches has its own function which is to turn ON or to turn OFF the inverter.

In order to reduce the harmonic, pulse-width modulation (PWM) methods can be used which is the process of adjusting the width of the pulses directly proportional to small control signal. The higher the voltage control, the more extensive the producing pulse become [5]. The primary objective in PWM scheme which is to calculate the converter switch ON times and create low frequency target of output voltage current. The secondary objective is to identify the most productive way of organizing the switching processes to reduce unnecessary harmonic distortion, switching losses, or any other specified performance criterion [6].

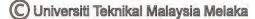

#### 2.2.1 Types of Inverter Output Waveform

There are three types of inverter output waveform that commonly used which are square wave, modified sine wave, and sine wave. Firstly, the square wave usually be the output waveform for the AC load voltage of the inverter as shown in the figure 2.2. The only advantages of square wave are can work with ordinary light bulb and the cost used is cheap. The square wave attempt to cause many problems for motors which is increase the motor power loss and caused reduction of efficiency in the motor [7]. Therefore, the square waveform has a very high harmonic content that form noise in electronic device particularly in audio device such as microphone or speaker [8].

The modified sine wave or also known as quasi-sine wave that show the enhancement over the square wave as shown in figure 2.2. The modified sine wave is quite similar to a square wave because it has "stepping" looks but different in the shape that more relates to the sine wave [8]. The quasi-sine wave have high power efficiency, and actually are suitable used for running some types of motors and incandescent lighting. The peak output voltage varies with the battery voltage is the main problems or disadvantages of quasi-sine wave which can produce harmonic [9].

Sine wave can be created by clarify more switching schemes and added circuitry that cause the cycle divided into smaller segments and creating a stepped voltage function that approximately looks like sine wave. Sine wave is a sinusoidal waveform as in figure 2.2 which is a better wave compared to square wave and modified sine wave. The advantages of sine wave is it has a very low harmonic distortion and high power efficiency. By using pulse width modulation (PWM) approached, the voltage and current pulses of varying width was created. The changing period of the pulse has the same result as a differing voltage magnitude. Therefore, pulse width modulation (PWM) definitely show a signal of changing magnitude. Thus, the harmonic content is minimize due to modification of square wave to sine wave using PWM approach. [8],[10]

Figure 2.2: Inverter output waveforms [10]

## 2.3 The Concept of Multilevel Inverter

Multilevel inverter mainly apply to combine a desired single or three-phase voltage waveform. By combining a few dc voltage sources, the desired multi-staircase output voltage can be acquired. There are three types of multilevel inverter topologies that commonly used nowadays which are neutral point clamp (NPC) or diode clamp (DC), cascaded H-bridge (CH), and flying capacitor (FCs). Cascaded H-bridge multilevel inverter has the higher output voltage and power levels (13.8k, 30MVA) compared to the other two topologies. Furthermore, cascaded multilevel inverter also has higher dependability due to its modular topology [11].

#### 2.3.1 Neutral Point Clamp Multilevel Inverter

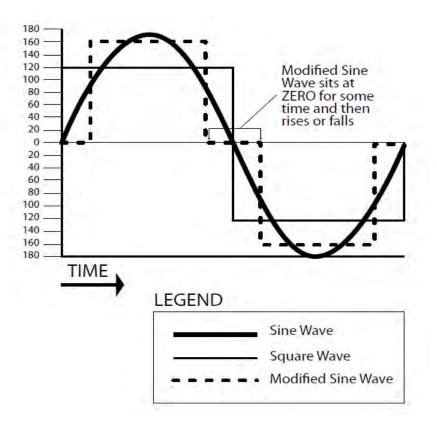

The neutral point clamped topology or also known as diode clamped topology has it main advantage which is it requires a single DC source, and contributes better execution. This NPC topology disadvantages is when the level 'n' increase, the number of clamping diodes will increases [12]. Thus, the NPC topology is generally utilized for three-level inverter as shown in Figure 2.3. Based on the table 2.1, it display about the switching state for three-level neutral point clamped (NPC) multilevel inverter. The output voltage will become +0.5Vdc if the S1 and S2 at ON condition and another two switches which are S3 and S4 at OFF condition. There are no output voltage will came out if S2 and S3 at ON condition. To get -0.5Vdc output voltage, S3 and S4 at ON condition.

Figure 2.3: Three -level Neutral Point Clamped topology

| S1 | S2 | S3 | S4 | Vo      |

|----|----|----|----|---------|

|    |    |    |    |         |

| 1  | 1  | 0  | 0  | +0.5Vdc |

|    |    |    |    |         |

| 0  | 1  | 1  | 0  | 0       |

|    |    |    |    |         |

| 0  | 0  | 1  | 1  | -0.5Vdc |

|    |    |    |    |         |

Table 2.1: Table of switching state for three-level NPC topology