# ANALYZE OF PROCESS PARAMETER IN 19nm WSi<sub>2</sub>/TiO<sub>2</sub> N-CHANNEL MOSFET USING STATISTICAL MODELLING

#### AMIRA EMYLIANA BINTI ZAILAN

This Report Is Submitted In Partial Of Requirements For The Bachelor Degree of Electronic Engineering (Computer Engineering)

Fakulti Kejuruteraan Elektronik Dan Kejuruteraan Komputer University Teknikal Malaysia Melaka

June 2017

#### UNIVERSTI TEKNIKAL MALAYSIA MELAKA FAKULTI KEJURUTERAAN ELEKTRONIK DAN KEJURUTERAAN KOMPUTER

#### BORANG PENGESAHAN STATUS LAPORAN PROJEK SARJANA MUDA II

| Tajuk Projek<br>Sesi Pengajian |                                                       | OF PROCESS PARAMETER IN 19nm WS./1702<br>EL MOSFET USING STATISTICAL MODELLING                                                                                                    |

|--------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | rkan Laporan Projek Sa                                | (HURUF BESAR) rjana Muda ini disimpan di Perpustakaan dengan syarat-syarat                                                                                                        |

| 2. Perpustakaan                | n dibenarkan membuat<br>n dibenarkan membuat<br>nggi. | Teknikal Malaysia Melaka.<br>salinan untuk tujuan pengajian sahaja.<br>salinan laporan ini sebagai bahan pertukaran antara institusi                                              |

|                                | SULIT*                                                | *(Mengandungi maklumat yang berdarjah keselamatan atau<br>kepentingan Malaysia seperti yang termaktub di dalam<br>AKTA RAHSIA RASMI 1972)                                         |

|                                | TERHAD** TIDAK TERHAD                                 | **(Mengandungi maklumat terhad yang telah ditentukan oleh<br>organisasi/badan di mana penyelidikan dijalankan)                                                                    |

| (TANDATAN<br>Tarikh: 2/6       | GAN PENULIS)                                          | Disahkan oleh:  (COP DAN TANDATANGAN PENYELIA)  DP. FAUZIYAH BINTI SALEHUDDIN  Faktin eji ara Levro dan  Tarikh: Eji ara Levro dan  Tarikh: Hang Tuah Jaya,  76-20 Disahkan oleh: |

"I declare that this thesis entitle "Analyze of Process Parameter in 19nm WSi2/TiO2 N-Channel MOSFET Using Statistical Modelling" is the result of my own research except as cited in the references. The thesis has been accepted for any degree and is not concurrently submitted in candidature of any other degree."

| Signature | · Fine                        |

|-----------|-------------------------------|

| Name      | : AMIRA EMYLIANA BINTI ZAILAN |

| Date      | . 2/6/17                      |

"I hereby declare that I have read this report and in my opinion this report is sufficient in terms of scope and quality for the award of Bachelor of Electronic Engineering (Computer Engineering) with Honors."

> . P.J. Signature : DR FAUZIYAH BINTI SALEHUDDIN Supervisor Name Date

Dedicated to my beloved family especially my parents, supervisor, lecturers and all my friends who helping me whether directly or indirectly.

## **ACKNOWLEGMENT**

I give thanks to the Almighty for His grace, I have managed to finish my project successfully. First of all I want to say a big thank you to Dr. Fauziyah Bt Sallehudin, the supervisor of this project, especially on his guidance, encouragement and advice provided and constructive ideas that have been shared with me throughout this project. Without the assistance and guidance, this project was not successful. All the knowledge that I'm gained and poured out I will use the best possible future for my future in the face of today's challenging job. I also want to thank all family members and friends for their support throughout this project. Lastly, I would like to express the gratitude to all other individual and parties that help in completing this thesis. Thank You.

#### ABSTRACT

This project investigates the impact of process parameter on threshold voltage (V<sub>TH</sub>), drive current (I<sub>ON</sub>) and leakage current (I<sub>OFF</sub>) for 19nm WSi<sub>2</sub>/TiO<sub>2</sub> NMOS device. using statistical modelling. The statistical methods that were used are 2k-factorial design and Taguchi method. The four process parameter, namely oxide growth temperature, V<sub>TH</sub> implant energy, pocket halo implant dose and compensate halo implant will be investigated and adjusted to improve the results. The simulated of the device was performed by using ATHENA module. While the electrical characterization of the device was implemented by using ATLAS module. These two modules will be combined with 2k-factorial and Taguchi Method to aid design and optimize the process parameters. The most effective process parameter with respect to threshold voltage, drive current and leakage current were chosen depend on the percentage of the factor effect on S/N ratio that indicate the relative power of factor to reduce variation. In this research, optimum condition for electrical characteristics have been compared using two methods to choose the best method for optimization process. The most dominant or significant factors for S/N Ratio are pocket halo implant dose and compensate implant dose. Meanwhile, the S/N Ratio values of V<sub>TH</sub>, I<sub>ON</sub> and I<sub>OFF</sub> after the optimization approaches for array L<sub>9</sub> is 41.30dB, 55.70dB and -14.17dBrespectively. In L<sub>9</sub> experiments, V<sub>TH</sub>, I<sub>ON</sub> and I<sub>OFF</sub> values for NMOS device after optimizations approaches are 0.530V, 622.667µA and 2.776pA respectively. The results obtained are closer to ITRS 2013 prediction. As conclusions, Taguchi Method was observed to be the most suitable method to be implemented in statistical modeling of 19nm WSi<sub>2</sub>/TiO<sub>2</sub> NMOS device.

#### **ABSTRAK**

Projek ini menyiasat kesan proses parameter di voltan ambang (V<sub>TH</sub>), drive current (I<sub>ON</sub>) dan arus kebocoran (I<sub>OFF</sub>) untuk peranti 19nm WSi<sub>2</sub> / TiO2 NMOS. menggunakan pemodelan statistik. Kaedah statistik yang digunakan adalah reka bentuk 2k-faktorial dan kaedah Taguchi. Empat proses parameter, iaitu suhu oksida pertumbuhan, implan tenaga V<sub>TH</sub>, poket halo implan dos dan mengimbangi halo implan akan disiasat dan diselaraskan untuk meningkatkan keputusan. Simulasi peranti telah dilakukan dengan menggunakan modul ATHENA. Manakala pencirian elektrik peranti telah dilaksanakan dengan menggunakan modul ATLAS. Kedua-dua modul akan digabungkan dengan 2k-faktorial dan Taguchi Kaedah untuk membantu reka bentuk dan mengoptimumkan parameter proses. Proses parameter paling berkesan berkenaan dengan voltan ambang, memandu semasa dan arus bocor dipilih bergantung kepada peratusan kesan faktor kepada nisbah S / N yang menunjukkan kuasa relatif faktor untuk mengurangkan variasi. Dalam kajian ini, keadaan optimum untuk ciri-ciri elcetrical telah dibandingkan dengan menggunakan dua kaedah untuk memilih kaedah yang terbaik untuk proses pengoptimuman. Faktor yang paling dominan atau penting untuk S / N Ratio adalah poket halo doktor dos dan mengimbangi dos implan. Sementara itu, S / N nilai Nisbah V<sub>TH</sub>, I<sub>ON</sub> dan I<sub>OFF</sub> selepas pengoptimuman menghampiri untuk pelbagai L<sub>9</sub> adalah 41.30dB, 55.70dB dan -14.17dB respectively. Dalam eksperimen L9, V<sub>TH</sub>, I<sub>ON</sub> dan I<sub>OFF</sub> nilai untuk peranti NMOS selepas pengoptimuman pendekatan yang 0.530V, masing-masing 622.667µA dan 2.776pA. Keputusan yang diperolehi adalah lebih dekat dengan ITRS 2013 ramalan. Sebagai kesimpulan, Taguchi Menghubungi diperhatikan sebagai kaedah yang paling sesuai untuk dilaksanakan dalam pemodelan statistik 19nm WSi2 peranti / TiO2 NMOS.

## TABLE OF CONTENT

| CHAPTER | TITLE                    | PAGES  |

|---------|--------------------------|--------|

|         |                          |        |

|         | PROJECT TITLE            | i      |

|         | REPORT VERIFICATION FORM | ii     |

|         | DECLARATION              | iii    |

|         | SUPERVISOR VERIFICATION  | iv     |

|         | DEDICATION               | v      |

|         | ACKNOWLEDGEMENT          | vi     |

|         | ABSTRACT                 | vii    |

|         | ABSTRAK                  | viii   |

|         | TABLE OF CONTENT         | ix-xii |

|         | LIST OF TABLES           | xiv    |

|         | LIST OF FIGURES          | xvi    |

|         | LIST OF ABBREVIATIONS    | xviii  |

#### INTRODUCTION 1

|   | 1.1 B  | ackground                                | 1  |

|---|--------|------------------------------------------|----|

|   | 1.2 O  | bjectives of This Project                | 2  |

|   | 1.3 Pı | roblem Statement                         | 2  |

|   | 1.4 Sc | cope of Project                          | 3  |

|   | 1.5 O  | rganization of Report                    | 3  |

|   |        |                                          |    |

| 2 | LITE   | ERATURE REVIEW                           |    |

|   |        |                                          |    |

|   | 2.1    | Introduction of MOSFET                   | 5  |

|   | 2.2    | Types of MOSFET                          | 6  |

|   | 2.3    | Operation Modes in MOSFET                | 7  |

|   | 2.4    | Electrical Characteristic of NMOS Device | 9  |

|   | 2.5    | Scaling                                  | 9  |

|   |        | 2.5.1 Short-Channel Effect (SCE)         | 10 |

|   |        | 2.5.2 Leakage Current                    | 10 |

|   | 2.6    | High-k Material                          | 11 |

|   | 2.7    | Statistical Modelling                    | 12 |

|   | 2.8    | Threshold Voltage                        | 12 |

|   | 2.9    | Ion Implantation                         | 12 |

|   | 2.1    | Halo Implantation                        | 13 |

|   | 2.11   | Taguchi Method                           | 13 |

| 2 | 12  | ) ) | k-fac  | ctorial | Design  | Method   |

|---|-----|-----|--------|---------|---------|----------|

|   | 1 4 | _   | IL ILL | COLIGI  | 2001511 | THECTHOO |

14

## 3 PROJECT METHODOLOGY

| 3.1 | Introduction |                                          | 15 |

|-----|--------------|------------------------------------------|----|

| 3.2 | Simul        | ation Using TCAD                         | 15 |

|     | 3.2.1        | ATLAS Simulator                          | 16 |

|     | 3.2.2        | ATHENA Simulator                         | 17 |

| 3.3 | Athen        | a – Fabrication step of 19nm WSi2/TiO2   | 17 |

|     | 3.3.1        | Mesh and Si substrate formation          | 17 |

|     | 3.3.2        | Gate Oxide Growth                        | 18 |

|     | 3.3.3        | Vth adjust implantation                  | 19 |

|     | 3.3.4        | High-k material deposition               | 20 |

|     | 3.3.5        | Halo implantation                        | 22 |

|     | 3.3.6        | Compensate implantation deposition       | 23 |

| 3.4 | ATHE         | ENA - Source code for 19nm WSi2/TiO2     | 24 |

|     | NMO          | S Transistor                             |    |

| 3.5 | Optim        | nization approach                        | 26 |

|     | 3.5.1        | Flowchart for Optimization Process       | 27 |

|     | 3.5.2        | Taguchi Method and 2k-factorial Approach | 28 |

|     | 3.6          | Identification of Process Parameters     | 29 |

|     |              | and their levels                         |    |

| 3.7 | The experiment setup for Taguchi Method | 29 |

|-----|-----------------------------------------|----|

| 3.8 | The experiment setup for 2k-factorial   | 31 |

|     | Design                                  |    |

## 4 RESULT AND ANALYSIS

| 4.1 | Introd | uction                                                                 |    | 33 |

|-----|--------|------------------------------------------------------------------------|----|----|

| 4.2 | Analy  | sis of 19nm WSi2/TiO2 NMOS device                                      |    | 33 |

| 4.3 | Analy  | sis of 2k-factorial                                                    |    | 37 |

|     | 4.3.1  | Estimation of Factor Effect                                            |    | 37 |

|     |        | toward VTH, ION and IOFF                                               |    |    |

|     | 4.3.2  | Analysis of Variance (ANOVA)                                           |    | 46 |

|     | 4.3.3  | Optimization Analysis via Desirability                                 |    | 48 |

|     |        | Function                                                               |    |    |

|     | 4.3.4  | Confirmation Test for 2k-Factorial                                     |    | 50 |

| 4.4 | Analy  | sis of Taguchi Method                                                  |    | 51 |

|     | 4.4.1  | $V_{\text{TH}},I_{\text{ON}},$ and $I_{\text{OFF}}$ values Acquisition | 52 |    |

|     | 4.4.2  | Analysis of process parameter effect                                   |    | 54 |

|     |        | on output response                                                     |    |    |

|     | 4.4.3  | Prediction S/N Ratio                                                   |    | 56 |

|     | 4.4.4  | Analysis of Variance (ANOVA)                                           |    | 62 |

|     | 4.4.5  | Analysis of Variance (ANOVA)                                           |    | 64 |

|     |        |                                                                        |    |    |

70

|       |              | for both optimization           |  |

|-------|--------------|---------------------------------|--|

|       | 4.4.6        | Confirmation Test               |  |

|       | 4.4.7        | Confirmation Test for           |  |

|       |              | Threshold Voltage Optimization  |  |

| 4.5   | Comparison b | between 2k-factorial design and |  |

|       | Taguchi Met  | hod                             |  |

|       |              |                                 |  |

|       |              |                                 |  |

| CON   | ICLUSION AN  | D FUTURE WORK                   |  |

|       |              |                                 |  |

| 510   | Conclusion   |                                 |  |

| 5.1 C |              |                                 |  |

REFERENCES

## LIST OF TABLES

| TABLE | TITLE                                                                        |    |

|-------|------------------------------------------------------------------------------|----|

| 3.1   | Process Parameter and their level of 19nm WSi <sub>2</sub> /Tio2             | 29 |

| 3.2   | Process parameter and their level                                            | 30 |

| 3.3   | Noise factor and their level                                                 | 30 |

| 3.4   | Taguchi Method L9 Orthogonal Array layout                                    | 31 |

| 3.5   | Process parameter and their level                                            | 32 |

| 3.6   | 2k-factorial design L8 Orthogonal Array layout                               | 32 |

| 4.1   | multiple properties of WSi <sub>2</sub> /TiO <sub>2</sub>                    | 37 |

| 4.2   | Estimation of Factor effect and Coefficient for $V_{TH}$                     | 38 |

| 4.3   | Estimation of Factor effect and Coefficient for IoN                          | 38 |

| 4.4   | Estimation of Factor effect and Coefficient for IOFF                         | 38 |

| 4.5   | ANOVA for V <sub>TH</sub>                                                    | 47 |

| 4.6   | ANOVA for Ion                                                                | 47 |

| 4.7   | ANOVA for I <sub>OFF</sub>                                                   | 47 |

| 4.8   | Preset Condition for Multi-Response Optimization                             | 48 |

| 4.9   | Optimum Level After Optimization Plot for Multiple Response                  | 49 |

| 4.10  | Best Setting of Control Factors                                              | 50 |

| 4.11  | Final Result of Confirmation Test for Multiple Properties                    | 50 |

| 4.12  | Process parameter and their level of 19nm WSi <sub>2</sub> /TiO <sub>2</sub> | 51 |

| 4.13  | Noise factor and their level of 19nm WSi <sub>2</sub> /TiO <sub>2</sub>      | 52 |

| 4.14  | V <sub>TH</sub> value for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>            | 52 |

| 4.15  | Ion value for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>                        | 53 |

| 4.16  | I <sub>ON</sub> value for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>            | 53 |

| 4.17  | Mean, Variance, and S/N ratio of Threshold Voltage, (V <sub>TH</sub> )       | 55 |

| 4.18 | S/N ratio of Drive Current, (IoN)             | 55 |

|------|-----------------------------------------------|----|

| 4.19 | S/N ratio of Leakage Current, (IOFF)          | 56 |

| 4.20 | Prediction S/N ratio for Nominal-the-Best     | 60 |

| 4.21 | Prediction S/N ratio for Larger-the-Best      | 61 |

| 4.22 | Prediction S/N ratio for Smaller-the-Best     | 61 |

| 4.23 | Best setting for V <sub>TH</sub> optimization | 62 |

| 4.24 | Best setting for IoN optimization             | 62 |

| 4.25 | Best setting for IOFF optimization            | 63 |

| 4.26 | Best setting for both optimization            | 64 |

| 4.27 | Confirmation test for V <sub>TH</sub>         | 65 |

| 4.28 | Confirmation test for IoN                     | 66 |

| 4.29 | Confirmation test for I <sub>OFF</sub>        | 66 |

| 4.30 | Comparison of result after optimization       | 67 |

## LIST OF FIGURES

| FIGURE | TITLE                                                                                | PAGE |

|--------|--------------------------------------------------------------------------------------|------|

| 2.1    | Structure of a MOSFET                                                                | 6    |

| 2.2    | Type of MOSFET                                                                       | 7    |

| 2.3    | Cross section of a MOSFET operating in the linear region                             | 8    |

| 2.4    | Cross section of a MOSFET operating in saturation                                    | 9    |

| 3.1    | Simulation Using TCAD                                                                | 16   |

| 3.2    | flowchart fabrication process for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>            | 17   |

| 3.3    | formation of Si substrate                                                            | 18   |

| 3.4    | Source code to build Silicon substrate                                               | 18   |

| 3.5    | Formation of gate oxide growth                                                       | 19   |

| 3.6    | Source code after gate oxide growth                                                  | 19   |

| 3.7    | Vth adjust implant structure                                                         | 20   |

| 3.8    | Source code of Vth adjust implant                                                    | 20   |

| 3.9    | Deposition of high-k material for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>            | 21   |

| 3.10   | Source code of formation high-k material                                             | 21   |

| 3.11   | Structure of 19nm WSi <sub>2</sub> /TiO <sub>2</sub> after process halo implantation | 22   |

| 3.12   | Source code of halo implantation                                                     | 22   |

| 3.13   | Deposition of compensate implantation in WSi <sub>2</sub> /TiO <sub>2</sub>          | 23   |

| 3.14   | Source code to do compensate implantation                                            | 23   |

| 3.15   | The source code for gate Oxide Growth Temperature                                    | 24   |

| 3.16   | The source code for Threshold Voltage Implant process                                | 25   |

| 3.17   | The source code for Pocket Halo Implant Process                                      | 25   |

| 3.18   | The source code for Compensate Implant Process                                       | 26   |

| 3.19   | Optimization process flow                                                            | 27   |

| 3.2    | Statistical method approach                                                          | 28   |

| 4.1    | WSi <sub>2</sub> /TiO <sub>2</sub> N-Channel MOSFET                                  | 34   |

| 4.2  | Contour of 19nm WSi <sub>2</sub> /TiO <sub>2</sub> N-Channel MOSFET         | 34 |

|------|-----------------------------------------------------------------------------|----|

| 4.3  | Graph I <sub>D</sub> -V <sub>G</sub> for WSi <sub>2</sub> /TiO <sub>2</sub> | 35 |

| 4.4  | Output window of WSi <sub>2</sub> /TiO <sub>2</sub>                         | 36 |

| 4.5  | Normal plot for V <sub>TH</sub>                                             | 39 |

| 4.6  | Normal plot for IoN                                                         | 40 |

| 4.7  | Normal plot for I <sub>OFF</sub>                                            | 41 |

| 4.8  | Pareto chart for V <sub>TH</sub>                                            | 42 |

| 4.9  | Pareto chart for I <sub>ON</sub>                                            | 42 |

| 4.10 | Pareto Chart for I <sub>OFF</sub>                                           | 43 |

| 4.11 | Main effect plot of V <sub>TH</sub>                                         | 44 |

| 4.12 | Main effect plot of I <sub>ON</sub>                                         | 45 |

| 4.13 | Main effect plot for I <sub>OFF</sub>                                       | 46 |

| 4.14 | Optimization Plot For Multiple Response                                     | 49 |

| 4.15 | S/N graph of Threshold Voltage for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>  | 57 |

| 4.16 | S/N graph of Drive Current for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>      | 58 |

| 4 17 | S/N graph of Leakage Current for 19nm WSi <sub>2</sub> /TiO <sub>2</sub>    | 59 |

## LIST OF ABBREVIATION

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

WSi<sub>2</sub> - Tungsten Silicide

TiO<sub>2</sub> - Titanium Oxide

SCE - Short Channel Effect

OA - Orthogonal Array

V<sub>TH</sub> - Threshold Voltage

Ion - Drive Current

I<sub>OFF</sub> - Leakage Current

EOT - Equivalent Oxide Thickness

#### CHAPTER 1

#### INTRODUCTION

## 1.1 Background

In this new technology, Metal Oxide Semiconductor Field Effect Transistor (MOSFET) technology now become famous in microelectronic industry for almost fifth decade. Because of that, the size of the MOSFET transistor has been decrease continuously through process of scaling validating based on Moore's Law [1]. Scaling down used to ensure the robust performance of transistor because of the user need for minor, quick, and affordable in price. Anyhow, there is some problem to further technology scaling which is short channel cause by expanding the process of fabrication of wafer. This lead to the introducing of high-K material such as Titanium Oxide (TiO<sub>2</sub>) [1]. Too many years the uses of Silicon oxide (SiO<sub>2</sub>) being gate dielectric material. Nowadays, replacing SiO<sub>2</sub> with high-k material as one of the new research initiatives to overcome those problems. Metal gate such as Tungsten Silicide (WSi<sub>2</sub>) are used for get rid of Poly-Si depletion which make leakage current are too high [2].

In this project, statistical method is used in order to analyzed the process parameter that impact most on the electrical characteristic especially threshold voltage (V<sub>TH</sub>). This is because threshold voltage is used to make sure whether the device working well or not. This consumed to better performance of IC. The most popular technique that used as statistical modelling called Taguchi method. This is because Taguchi method has ability to give the closer value to predicted value. Other than that,

Taguchi method also can verify the process parameter that give big impact on output response such as V<sub>TH</sub>, I<sub>ON</sub> and I<sub>OFF</sub>. The benefit of using Taguchi method than other method is Taguchi method only require small number of experiment but can studied the entire process [3].

### 1.2 Objective in this research

The objective in this research:

- (i) To optimize the process parameter variation and electrical characterization of 19nm WSi<sub>2</sub>/TiO<sub>2</sub> using 2k-factorial and Taguchi method.

- (ii) To analyze the significant input process parameters which will be impact most on the output responses of WSi<sub>2</sub>/TiO<sub>2</sub> MOSFET.

- (iii) To obtain the optimum solutions for nano scale MOSFETs device to verify the predicted optimal design.

#### 1.3 Problem Statement

The problem occurs because the further scaling of SiO2 is below 2nm gate layer thickness which can result in a large increase of the leakage current and short channel effect. In order to overcome this problem, many researchers are focusing on the metal gate with high –k materials that have the ability to be integrated in MOSFET flow [3]. Other than that, statistical modelling is one of the method to improve the performance of the ICs [2]. Optimization was the one of the solution to solve the problem related with performance of device without expanding the cost [2]

## 1.4 Scope of Project

First and foremost, based on the journal, previous research and reference books will be reviewed in more detail. The literature reviews of this project regarding of objective this project will be covered. This research mainly focused on the optimization of input process parameter variation and performance of electrical characteristics in WSi<sub>2</sub>/TiO<sub>2</sub> MOSFET device. This device will be optimized through out of this project using 2-k factorial and Taguchi Method. Virtual fabrication design of WSi<sub>2</sub>/TiO<sub>2</sub> MOSFET device will be carried out by using Silvaco ATHENA. The electrical characterization of device is going to be carried out by employing ATLAS. Other than that, there is also important to know more about characteristic of MOSFET in order to get the better value threshold voltage level (V<sub>TH</sub>), drive current (I<sub>ON</sub>), leakage current (I<sub>OFF</sub>) in International Technology Roadmap Semiconductor (ITRS) 2013 for Low Power (LP) technology requirements of year 2015 prediction [5].

## 1.5 Organization of Report

This thesis contains five chapter starting from introduction to the research, literature review that related with this research, result analysis and discussion based on the result and lastly the conclusion from the result that have done with the desired future work.

In chapter 1, starting from introduction of this research with explanation little bit about the project and objective to conduct this experiment. After that, followed by chapter 2 which is will discuss about past researcher work that related to this project. The literature review in this research will be focused on statistical modelling since it is the main objective of this project.

In this chapter 3, the project methodology will be discussed in this chapter. All the flowchart and flow of the whole process that related to the statistical modelling. Flow of the process to do optimization using Taguchi method and 2k-factorial will be analyzed in this chapter.

In chapter 4, the whole result of the modelling process starting from Taguchi method until 2k-factorial design will be analyzed in this chapter. The comparison will be finalized after complete the two process of optimization. Lastly, in chapter 5, the conclusion and future work will be finalized in this chapter.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### 2.1 Introduction

Metal-Oxide Semiconductor Field Effect Transistor (MOSFET) is a device that has been widely used in the industry. These devices are, such as the digital circuit, microprocessor and memory circuit industry. MOSFET is used as a switch to amplify the electronic signal. The integrated circuit (IC) comprises million numbers of MOSFET devices due to their small size characteristic, and this feature is another advantage of this device to the electronic industry in the world [1]. Since the 1970s the MOSFET has been the prevailing device in microprocessors, memory circuits and logic applications of many kinds. The fabrication process for MOSFET has become very mature over the 25 to 30 year lifetime of this device [3].

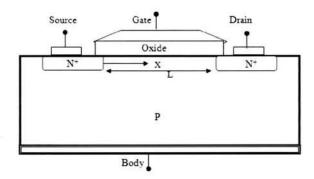

A MOSFET is based on the modulation of charge concentration caused by a MOS capacitance. The structure of a MOSFET is shown in Figure 2.1. The MOSFET has two terminals, called source and drain, which are connected to highly doped regions which are separated by a region called the channel. With an insulated gate MOSFET device no such limitations apply so it is possible to bias the gate of a MOSFET in either polarity, positive (+ve) or negative (-ve) [4]. This region is not so highly doped. The third electrode in the MOSFET, called the gate, is located above the body and insulated from all of the other regions by an oxide (usually an oxide of Si) [6].

Figure 2.1: Structure of a MOSFET

The source is so named because it is the origin of the charge carriers (electrons for n-channel, holes for p-channel) that flow through the channel; similarly, the drain is where the charge carriers leave the channel. The MOSFET can be of n-channel or p-channel depending on the doping material in the source and drain of the MOSFET [6].

### 2.3 Operation Modes in MOSFET

In the case of n-channel MOSFET, when there is no voltage applied to the gate there is no channel formation between source and drain and hence there is no current flow between them. However, when a positive gate-source voltage is applied, it creates a channel at the surface of the p- region which is negatively charged, under the oxide. When a negative voltage is applied between gate and source, the channel disappears and no current can flow between the source and the drain. The operation of a MOSFET can be divided into three different regions, depending upon the voltages at the terminals. The three regions of operation are cutoff, linear and saturation region [6].