## CHARACTERIZATION OF SILICON ON INSULATOR (SOI) MOSFET USING TCAD TOOLS

### MUHAMMAD NAZIRUL IFWAT BIN ABD AZIZ

This report is submitted in partial fulfilment of the requirements for the Bachelor of Electronic Engineering (Computer Engineering) with Honors

Faculty of Electronics and Computer Engineering

Universiti Teknikal Malaysia Melaka

June 2014

|             |                         | JTeN                             | UNIVERSTI TEKNIKAL MALAYSIA MELAKA<br>FAKULTI KEJURUTERAAN ELEKTRONIK DAN KEJURUTERAAN KOMPUTER                                                                                                                         |

|-------------|-------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and a state |                         |                                  |                                                                                                                                                                                                                         |

| UNIVER      | SITI TEKNIKA            | I MALAYSIA MELA                  | BORANG PENGESAHAN STATUS LAPORAN                                                                                                                                                                                        |

|             |                         |                                  | PROJEK SARJANA MUDA II                                                                                                                                                                                                  |

|             | Tajuk Pro               | DE                               | ARACTERIZATION OF SILICON ON INSULATOR(SOI) MOSFET<br>VICE USING TCAD TOOLS                                                                                                                                             |

|             | Sesi Peng               | gajian : 1                       | 1 3 / 1 4                                                                                                                                                                                                               |

| Sa          | 79                      | MUHA                             | MMAD NAZIRUL IFWAT BIN ABD AZIZ                                                                                                                                                                                         |

|             |                         | *****                            | (HURUF BESAR)                                                                                                                                                                                                           |

| me<br>sy:   | ngaku men<br>mat keguna | nbenarkan Lap<br>1an seperti ben | ooran Projek Sarjana Muda ini disimpan di Perpustakaan dengan syarat<br>ikut                                                                                                                                            |

| 1.          | Laporan                 | adal ah hakmi l                  | lik Universiti Teknikal Malaysia Melaka.                                                                                                                                                                                |

| 2           | Perpusta                | kaan dibenark                    | kan membuat sali nan untuk tujuan pengajian sahaja                                                                                                                                                                      |

| 3.          | Perpusta                | kaan dibenark                    | kan membuat salinan lapuran ini sebagai bahan pertukaran antara inst                                                                                                                                                    |

|             | pengajia                |                                  |                                                                                                                                                                                                                         |

| 4           | Silatand                | akan(v)                          |                                                                                                                                                                                                                         |

|             |                         | SULIT <sup>#</sup>               | *(Mengandungi maklumat yang berdarjah keselamatan atau<br>kepentingan Malaysia seperti yang termaktub di dalam AKTA<br>RAHSIA RASMI 1972)                                                                               |

|             |                         | TERHAD**                         | **(Mengandung maklumatterhadyangtelah ditentukan oleh<br>organisasi/badan di mana penyelidikan dijalankan)                                                                                                              |

|             | $\checkmark$            | TIDAK TERHAD                     |                                                                                                                                                                                                                         |

|             |                         | anti                             | DR. FAUZIYAH BINTI SALEHUDDIN<br>Di Steinstenabilkattian<br>Fakulti Kejuruteraan Elektronik dan<br>Kejuruteraan Kamputer<br>Univerniti Tenkkai Minayso kelake (UTEM)<br>Hang Tuan Jaya,<br>76100 Durran Tunggal, Melaka |

|             |                         | TANDADANGAN                      | PENULIS) (COP DAN TANDATANGAN PENYELIA)                                                                                                                                                                                 |

I

### DECLARATION

I declare that this thesis entitle "Characterization of Silicon on Insulator (SOI) using TCAD tools" is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

|           | and m-                              |

|-----------|-------------------------------------|

| Signature | · QVY                               |

| Name      | Muhammad Nazirul Ifwat Bin Abd Aziz |

| Date      | . 6 June 2013                       |

11

### DECLARATION

I declare that this thesis entitle "Characterization of Silicon on Insulator (SOI) using TCAD tools" is the result of my own research except as cited in the references. The thesis has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | and -                               |

|-----------|-------------------------------------|

| Name      | Muhammad Nazirul Ifwat Bin Abd Aziz |

| Date      | 6 June 2013                         |

### SUPERVISOR VERIFICATION

I hereby declare that I have read this report and in my opinion this report is sufficient in

termsof scope and quality for the award of Bachelor of Electronic Engineering (Computer Engineering) with Honours. DR. FAUZIYAH BINTI SALEHUDDIN Pengarah Kanan Fakuhr Buttersan Electronic transformer Signature Signature Hang Tuah Jaya. 76100 Durian Tunega, Melaka Supervisor's Name : DR. FAUZIYAH BINTI SALEHUDDIN

Date

6/6/2014 : .......... ......

Ш

Dedicated to my beloved family especially my parents, supervisor, lecturers, all my friends.

IV

## ACKNOWLEDGEMENT

In the name of Allah, the Most Gracious and the Most Merciful, all praises to Allah for the strengths and His blessing in completing this thesis.

First and foremost, I wish to express my sincere appreciation to my supervisor, Dr. Fauziyah Binti Salehuddin, for encouragement, guidance, advices and suggestions throughout the experimental and thesis works have contributed to the success of this project.

My sincere appreciation also extends to all my colleagues and others who have provided assistance at various occasions. Their views and tips are useful indeed. Unfortunately, it is impossible to list all of them in this limited space.

Finally, i would like to thank my family for their unconditional love and support during completing this project. I would not have been able to complete this thesis without their continuous love and encouragement.

V

### ABSTRACT

Thisproject present the result of process and device semulation using silvaco TCAD tools to develop Silicon on insulator (SOI) MOSFET. The aim for this project is to analyze the electrical characteristic of SOI MOSFET and the effect of Buried oxide layer (BOX) with the variation of thickness. The result obtained show that as the electrical characteristic of SOI MOSFET greatly increase with the presence of BOX layer. This SOI MOSFET has higher Drive current (ION), lower Leakage current and lower Subthreshold Swing (Ss). With this increasing perfomance, the switching speed for this MOSET device increase and it has lower power consumption as the ratio of ION/IOFF is larger. For information, the larger the ratio, the lower the power consumption. This project also analyze the effect of oxide layer thickness toward the electrical characteristic and the result shown that the thickness of oxide layer increase will decrease the perfomance of device. The best thickness is 100nm thickness layer but if its to thick then the Finfet technology need to be used as prevention because when the thickness become too smal it will also decrease the perfomance.Finfet refer as one of the types of multigate transistor. The term FinFET is to describe a nonplanar, double-gate transistor built on an SOI substrate.

#### ABSTRAK

Projek ini membentangkan hasil daripada proses dan peranti semulation menggunakan alat-alat silvaco TCAD untuk membangunkan Silikon pada penebat ( SOI) MOSFET . Tujuan projek ini adalah untuk menganalisis ciri elektrik MOSFET SOI dan kesan dikebumikan lapisan oksida ( BOX ) dengan perubahan ketebalan . Keputusan yang diperolehi menunjukkan bahawa ciri elektrik SOI MOSFET sangat meningkatkan dengan kehadiran lapisan BOX. Ini MOSFET SOI mempunyai arus yang lebih tinggi Drive (ION), lebih rendah Kebocoran Swing Subthreshold semasa dan lebih rendah ( SS) . Dengan Prestasi ini yang semakin meningkat, kelajuan pensuisan untuk ini peningkatan peranti MOSET dan ia mempunyai penggunaan kuasa lebih rendah sebagai nisbah ION / IOFF adalah lebih besar . Untuk pengetahuan, lebih besar nisbah , lebih rendah penggunaan kuasa. Projek ini juga menganalisis kesan oksida ketebalan lapisan ke arah ciri elektrik dan hasilnya menunjukkan bahawa ketebalan oksida lapisan peningkatan akan mengurangkan Prestasi peranti . Ketebalan terbaik adalah 100nm lapisan tebal tetapi jika untuk tebal maka teknologi Finfet yang perlu digunakan sebagai pencegahan kerana apabila ketebalan menjadi terlalu smal ia juga akan mengurangkan perfomance.Finfet rujuk sebagai salah satu jenis transistor multigate . FinFET adalah untuk menggambarkan tak satah, dua pintu transistor dibina di atas substrat SOI.

### TABLE OF CONTENTS

CHAPTER TITLE

PAGE

| PROJECT TITLE          | i    |

|------------------------|------|

| REPORT STATUS FORM     | ii   |

| DECLARATION            | iii  |

| SUPERVISORVERIFICATION | iv   |

| DEDICATION             | v    |

| ACKNOWLEDGEMENT        | vī   |

| ABSTRACT               | vii  |

| ABSTRAK                | viii |

| TABLEOFCONTENT         | ix   |

| LISTOFTABLES           | xii  |

| LISTOFFIGURES          | xiii |

| LISTOFABBREVIATIONS    | xv   |

|                        |      |

# 1 INTRODUCTION

| 1.1 | Introduction              | 1 |

|-----|---------------------------|---|

| 1.2 | Objectives of the project | 4 |

| 1.3 | Problem Statement         | 4 |

| 1.4 | Scope of the project      | 4 |

| 1.5 | Project outline           | 3 |

VIII

## LITERATURE REVIEW

| 2.1 |      | MOSI   | FET ( Metal-Oxide-Semiconductor Field Effect   |    |  |

|-----|------|--------|------------------------------------------------|----|--|

|     |      | Trans  | istor)                                         | 6  |  |

|     |      | 2.1.1  | Electrical characteristic of MOSFET            | 7  |  |

|     | 2.2  | Silico | n-On-Insulator(SOI) MOSFET Design.             | 8  |  |

|     | 2.3  | Short- | Channel effect                                 | 9  |  |

|     |      | 2.3.1  | Off-state Leakage Current (IOFF)               | 10 |  |

|     |      | 2.3.2  | V <sub>TH</sub> Roll-Off                       | 10 |  |

|     |      | 2.3.3  | Drain induced barrier lowering (DIBL)          | 11 |  |

|     | 2.4  | Floati | ng body charge on SOI                          | 12 |  |

|     | 2.5  | Kink l | Effect                                         | 13 |  |

|     | 2.6  | Impro  | ved sub threshold characteristic.              | 14 |  |

|     | 2.7  | SOI fa | brication material                             | 14 |  |

|     |      | 2.7.1  | Separation by Implantation of Oxygen (SIMOX)   | 15 |  |

|     |      | 2.7.2  | Zone melting Recrystallization (ZMR)           | 15 |  |

|     |      | 2.7.3  | Full isolation by Porous Oxidized Silicon      | 16 |  |

|     |      | 2.7.4  | Wafer Bonding (WB)                             | 16 |  |

|     |      | 2.7.5  | Silicon On Sapphire (SOS)                      |    |  |

|     |      |        | & Silicon On Zirconia (SOZ)                    | 17 |  |

|     | 2.8  | Fully- | Depleted SOI MOSFET and Partially-Depleted SOI |    |  |

|     |      | MOSE   | ET                                             | 18 |  |

|     | 2.9  | Drain  | Breakdown Mechanism in Ultra-thin-Film SOI     |    |  |

|     |      | MOSE   | FET                                            | 19 |  |

|     | 2.10 | lon Im | plantation                                     | 20 |  |

|     |      | 2.10.1 | Halo Implantation                              | 22 |  |

|     |      | 2.10.2 | Source Drain implants                          | 23 |  |

|     | 2.11 | Proces | s parameter Variantions                        | 24 |  |

|     |      | 2.11.1 | Taguchi Method                                 | 25 |  |

|     |      | 2.11.2 | Orthogonal array                               | 25 |  |

|     |      | 2.11.3 | Experiment Design strategy                     | 25 |  |

|     |      |        |                                                |    |  |

C Universiti Teknikal Malaysia Melaka

| 2.11.4 Signal-to-Boise (S/N) ratio | 26 |

|------------------------------------|----|

| 2.11.5 Analysis of variance        | 28 |

х

### 3 METHODOLOGY

3.1 Introduction 29 3.2 Basic flowchart of NMOS transistor 29 3.3 Fabrication and Design of 100n Silicon on Insulator(SOI) MOSFET. 31 Mesh Initialization 3.3.1 32 3.3.2 Well Oxidation 32 3.3.3 Box formation 33 3.3.4 Mask Nitride Deposition 34 3.3.5 Photoresist Layer Ethcing 35 3.3.6 Setup a Silicon Trench Machine 36 3.3.7 Trench Sidewall Passivation 37 Chemical Mechanical Polishing (CMP) 3.3.8 38 3.3.9 Sacrificial Oxidation 39 3.3.10 Gate Oxide Growth 40 3.3.11 Threshold Voltage Adjustment Implantation 41 3.3.12 Polysilicon Gate Deposition 42 3.3.13 Halo Implantation 43 3.3.14 Sidewall Spacer 44 3.3.15 Source/Drain Implantation 45 3.3.16 Silicide Growth 46 3.3.17 PECVD&BPSG Oxide Deposition 47 3.318 Pattern Source/Drain Contact and Compress Implantation 48 3.3.19 Aluminium Metallization 49 3.3.20 Aluminium Ethcing 50

C Universiti Teknikal Malaysia Melaka

# 3.3.21 Mirror SOI MOSFET Structure and Define

| Electrode                                           | 51                                                                                                      |                                                                                                       |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Optimization Approach                               | 53                                                                                                      |                                                                                                       |

| Taguchi Method Approach                             | 55                                                                                                      |                                                                                                       |

| Identification of Process Parameter and their level | 55                                                                                                      |                                                                                                       |

| Selection of Orthogonal Array                       | 56                                                                                                      |                                                                                                       |

|                                                     | Optimization Approach<br>Taguchi Method Approach<br>Identification of Process Parameter and their level | Optimization Approach53Taguchi Method Approach55Identification of Process Parameter and their level55 |

4

## **RESULTS AND DISCUSSION**

| 4.1  | Bulk MOSFET                                                                                      | 57 |  |

|------|--------------------------------------------------------------------------------------------------|----|--|

| 4.2  | Silicon on insulator (SOI) MOSFET                                                                | 60 |  |

| 4.3  | Comparison between Bulk MOSFET and 100nm                                                         |    |  |

|      | SOI MOSFET                                                                                       | 64 |  |

| 4.4  | 200nm SOI MOSFET                                                                                 | 64 |  |

| 4.5  | 300nm SOI MOSFET                                                                                 | 67 |  |

| 4.6  | Comparison between different thickness of Buried Oxide                                           |    |  |

|      | Layer (BOX)                                                                                      | 70 |  |

| 4.7  | Optimization of V <sub>TH</sub> , I <sub>OFF</sub> , I <sub>ON</sub> and S <sub>S</sub> using L9 |    |  |

|      | Taguchi Design                                                                                   | 71 |  |

| 4.8  | L9 array Design Taguchi Method                                                                   | 72 |  |

| 4.9  | V <sub>TH</sub> , I <sub>OFF</sub> , I <sub>ON</sub> and S <sub>S</sub> Values Acquisition       | 73 |  |

| 4.10 | Taguchi Method Analysis Response, $V_{TH}$ , $I_{OFF}$ , $I_{ON}$ and $S_S$                      | 75 |  |

|      | 4.10.1 Signal to Noise Analysis                                                                  | 76 |  |

|      | 4.10.2 Prediction S/N ratio                                                                      | 78 |  |

|      |                                                                                                  |    |  |

### 5

# CONCLUSION AND RECOMMENDATION

| 5.1        | Conclusion                             | 85 |

|------------|----------------------------------------|----|

| 5.2        | Recommendation and Future Developement | 86 |

| REF        | REFERENCES                             |    |

| APPENDIX A |                                        | 64 |

## LIST OF TABLES

## NO. TITLE

### PAGES

| 2.1  | L9 Experiments with two levels of Noise Factor                             | 26 |

|------|----------------------------------------------------------------------------|----|

| 3.1  | Process parameters variation of 100n SOI MOSFET                            | 56 |

| 3,2  | L9 Orthogonal array layout                                                 | 56 |

| 4.1  | Comparison between SOI MOSFET and Conventionak Bulk                        |    |

|      | MOSFET                                                                     | 64 |

| 4.2  | Comparison of electrical characteristic<br>between different BOX thickness | 71 |

| 4.3  | Process parameters and their levels                                        | 72 |

| 4.4  | Noise factor and thier levels                                              | 72 |

| 4.5  | Taguchi Experimental Layout using L9 Orthogonal array                      | 72 |

| 4.6  | V <sub>TH</sub> Values for 100nm SOI MOSFET Device                         | 73 |

| 4.7  | IoN Values for 100nm SOI MOSFET Device                                     | 74 |

| 4.8  | IOFF Values of 100n SOI MOSFET Device                                      | 74 |

| 4.9  | S <sub>8</sub> Values for 100n SOI MOSFET Device                           | 75 |

| 4.10 | Mean, variance and S/N ratio for VTH                                       | 76 |

| 4.11 | S/N ratio for Leakage current IOFF                                         | 77 |

| 4.12 | S/N ratio for Subthreshold swing, SS                                       | 77 |

| 4.13 | S/N ratio for Drive current, ION                                           | 78 |

| 4.14 | Prediction S/N ratio for nominal-the-best of VTH                           | 82 |

| 4.15 | S/N ratio for optimize leakage current                                     | 82 |

|      |                                                                            |    |

| 4.16 | Prediction S/N ratio for smaller-the-best of IOFF | 83 |  |

|------|---------------------------------------------------|----|--|

| 4.17 | S/N ratio for Subthreshold swing                  | 83 |  |

| 4.18 | Prediction S/N ratio for smaller-the-best of Ss   | 84 |  |

| 4.19 | S/N ratio for Drive current                       | 84 |  |

| 4.20 | Prediction S/N ratio for Larger-the-best of ION   | 82 |  |

|      |                                                   |    |  |

XIII

## LIST OF FIGURES

| NO.  | TITLE                                                                                                    | PAGES |  |

|------|----------------------------------------------------------------------------------------------------------|-------|--|

|      |                                                                                                          |       |  |

| 1.1  | The basic structure of the MOSFET device                                                                 | 2     |  |

| 2.1  | Basic structure of MOSFET                                                                                | 6     |  |

| 2.2  | MOSFET operating modes.                                                                                  | 7     |  |

| 2,3  | Physical structure of basic SOI devices                                                                  | 9     |  |

| 2.4  | Direct Carrier Injection.                                                                                | 11    |  |

| 2.5  | Example of a Drain-Induced Barrier-Lowering                                                              | 12    |  |

| 2.6  | Fabrication of SIMOX Wafers                                                                              | 15    |  |

| 2.7  | Unibond fabrication process                                                                              | 17    |  |

| 2.8  | Bulk type (a) Cross section of a partially depleted (b) and a Fully depleted (c) long channel SOI MOSFET | 18    |  |

| 2.9  | Localized Implantation of Boron Atoms                                                                    | 21    |  |

| 2.10 | Dopant Profile after implantation.                                                                       | 21    |  |

| 2.11 | Halo implant - only two quarters of total dose for two rotations.                                        | 23    |  |

| 3.1  | Basic NMOS Process Simulation Flowchart                                                                  | 30    |  |

| 3.2  | Flowchart of SOI MOSFET Design                                                                           | 28    |  |

| 3.3  | P-type Substrate Doping Concentration                                                                    | 32    |  |

| 3.4  | MOSFET Structure after Oxide Deposition                                                                  | 33    |  |

| 3.5  | Box Formation of SOI MOSFET                                                                              | 34    |  |

|      |                                                                                                          |       |  |

XIV

| 3.6  | MOSFET Structure after Nitiride Deposition and Photoresist     | 35 |

|------|----------------------------------------------------------------|----|

| 3.7  | MOSFET Structure after Photoresist Etching                     | 36 |

| 3.8  | MOSFET Structure after Nitride Etching and Photoresist removal |    |

| 3.9  | MOSFET structure after New Oxide Layer Deposition              | 38 |

| 3.10 | MOSFET Structure after CMP                                     | 39 |

| 3.11 | MOSFET Structure after sacrificial Oxidation                   | 40 |

| 3.12 | MOSFET structure after gate oxide Growth                       | 41 |

| 3.13 | MOSFET Structure after Threshold Voltage Adjusment Implantati  |    |

| 3.14 | MOSFET Structure after Polysilicon Gate Deposition             | 43 |

| 3.15 | MOSFET Structure before and after Halo Implantation            | 44 |

| 3.16 | MOSFET Structure after Depositing and Etching Nitride          | 45 |

| 3.17 | MOSFET Structure after Source/Drain implantation               | 46 |

| 3.18 | MOSFET Structure after silicide growth                         | 47 |

| 3.19 | MOSFET Structure after BPSG Process                            | 48 |

| 3.20 | MOSFET Sturcture after compress implantation                   | 49 |

| 3.21 | MOSFET Structure after aluminium Matellization                 | 50 |

| 3.22 | MOSfet Structure after after Aluminium etching                 | 51 |

| 3.23 | 100n SOI MOSFET Structure after mirorring                      | 52 |

| 3.24 | Optimization process Flowchart                                 | 54 |

| 3.25 | Major steps of implenting the taguchi method                   | 55 |

| 4.1  | Bulk MOSFET                                                    | 57 |

| 4.2  | Graph I <sub>D</sub> -V <sub>D</sub> for Bulk MOSFET           | 58 |

| 4.3  | Graph I <sub>D</sub> -V <sub>G</sub> for bulk MOSFET           | 59 |

| 4.4  | ION and IOFF value for bulk MOSFET                             | 59 |

| 4.5  | Output window of bulk MOSFET                                   | 60 |

| 4.6  | SOI MOSFET structures                                          | 61 |

1.0

xv

| 4.7  | Countour of 100nm SOI MOSFET                                    | 61 |

|------|-----------------------------------------------------------------|----|

| 4.8  | Graph I <sub>D</sub> -V <sub>D</sub> for 100nm SOI MOSFET       | 62 |

| 4.9  | Graph I <sub>D</sub> -V <sub>G</sub> for 100nm SOI MOSFET       | 62 |

| 4.10 | I <sub>ON</sub> and I <sub>OFF</sub> value for 100nm SOI MOSFET | 63 |

| 4.11 | Characteristic value of SOI MOSFET                              | 63 |

| 4.12 | 200nm SOI MOSFET Structure                                      | 65 |

| 4.13 | Graph I <sub>D</sub> -V <sub>D</sub> for 200nm SOI MOSFET       | 65 |

| 4.14 | Graph I <sub>D</sub> -V <sub>G</sub> for 200n SOI MOSFET        | 66 |

| 4.15 | ION and IOFF value 200nm SOI MOSFETS                            | 66 |

| 4.16 | Electrical Characteristic value of 200n SOI MOSFET              | 67 |

| 4.17 | 300nm SOI MOSFET design Structure                               | 68 |

| 4.18 | Graph I <sub>D</sub> -V <sub>D</sub> for 300nm SOI MOSFET       | 68 |

| 4.19 | Graph I <sub>D</sub> -V <sub>G</sub> for 300nm SOI MOSFET       | 69 |

| 4.20 | I <sub>ON</sub> and I <sub>OFF</sub> value 300nm SOI MOSFETS    | 69 |

| 4.21 | Electrical Characteristic value of 300nm SOI MOSFET             | 70 |

| 4.22 | S/N graph of threshold voltage for SOI MOSFET                   | 78 |

| 4.23 | S/N graph of Leakage Current for SOI MOSFET                     | 79 |

| 4.24 | S/N graph of Drive current (ION) for SOI MOSFET                 | 80 |

| 4.25 | S/N graph of Drive current (ION) for SOI MOSFET                 | 80 |

|      |                                                                 |    |

XVI

# LIST OF ABBREAVIATIONS

| SOI              | Silicon on Insulator                              |  |

|------------------|---------------------------------------------------|--|

| MOSFET -         | Metal-Oxide Semiconductor Field Effect Transistor |  |

| DIBL             | Drain induced Barrier Lowering                    |  |

| ITRS             | International Technology Roadmap Semiconductor    |  |

| SIO <sub>2</sub> | Silicon Dioxide                                   |  |

| TCAD             | Techonology Computer Aided System                 |  |

| SNR              | Signal to Noise Ratio                             |  |

| nm               | Nanometer                                         |  |

| NMOS             | N-Channel MOSFET                                  |  |

| PMOS             | P- Chanel MOSGET                                  |  |

|                  |                                                   |  |

XVII

# LIST OF SYMBOLS

| ID                         | -     | Drain Current             |

|----------------------------|-------|---------------------------|

| I <sub>OFF</sub>           | -     | Off-state Leakage Current |

| V <sub>DS</sub>            | ÷     | Drain to source Voltage   |

| V <sub>G</sub>             | -     | Gate Voltage              |

| V <sub>GS</sub>            | ÷     | Gate to source Voltage    |

| $\mathbf{V}_{\mathrm{TH}}$ | (*    | Threshold Voltage         |

| I <sub>ON</sub>            | der i | Drive current             |

| Ss                         |       | Subthreshold Swing        |

| S/N                        | ÷     | Signal to noise           |

|                            |       |                           |

XVIII

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

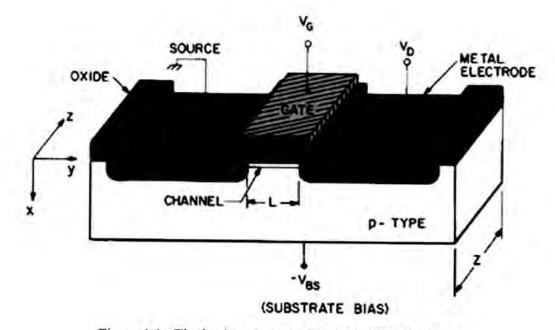

The Metal-Oxide Semiconductor Field Effect Transistor (MOSFET) is a device that widely used in industry, especially digital circuit, microprocessor and memory circuit industry. This MOSFET is used as a switch or to amplify the electronic signal. In one integrated circuit (IC), they will be a lot the number of MOSFET because of his small size characteristic thus simply make it another advantage of this device to the electronic industry in the world [3]. MOSFET technology is well-known in the industry. This technology has been used a lot and has been around for many years starting from early 60-70s. There have been a lot of gains in the performance of the MOSFET device since their creation with the size keeps decrease with improving years [1].

The cost and size are the main attribute of MOSFETS devices. Since the technology is well established thus make the fabrication process of this device have experienced decreased of cost. With the advantage of smaller physical shape than the others' technologies, thus allowing more devices in silicon wafer in fabrication makes MOSFET devices mainly used in the creation of Complementary Metal Oxide Semiconductor (CMOS) logic chips because of its cheap cost. Now MOSFET technologies have become the heart of every computer. An enhancement-type NMOS

transistor was used during this course of this project. Figure 1.1 shows the basic structure of MOSFET device.

Figure 1.1: The basic structure of the MOSFET device [2].

Silicon-On-Insulator (SOI) devices are new technology that recently popular. Although the technology has been around since 1960's, this SOI less popular of before and lately become popular because of the expense associated with producing the devices. SOI is the advancement of standard MOSFET technologies that improve in their characterizations. The main difference between SOI MOSFET and regular MOSFET is the inclusion of an insulating layer. SOI devices are created from a thin layer of silicon placed on top of a layer of insulating [1].

The purpose of this research is to design and analyze the electrical characterization of Silicon-On-Insulator (SOI) Metal-Oxide-Semiconductor Field Effect transistor (MOSFET) performance using Technology Computer-Aided Design (TCAD) tools. TCAD tool is a program that's been made to allow the creation, fabrication, and simulation of semiconductor devices. This TCAD tool is used for designing various

applications for semiconductor device. Silicon-On-Insulator (SOI) device is a siliconbased device built upon an insulating substrate [3].

Substrate for this SOI can be ranged from a rate material such as ruby, diamond and sapphire to common materials that largely been used in the semiconductor industry that is silicon dioxide. The SOI design that is being applied in this research was SOI MOSFET design, using silicon dioxide for the dielectric. The structure of SOI MOSFET is no different from a regular MOSFET design, but the difference is the existence of a thick layer of insulating material under the depletion region that gives a slightly different value of electrical value in this design thus improve its characteristic value. During this research, Silvaco's TCAD tools were used to create simulations of the device. These simulations provided a great deal of opportunities to examine the issue of various parameters on the overall device performance. Throughout the years, the operation of each simulated device gradually been improved and until an optimal device, configuration was produced for the particular applications.

The primary advantage of SOI performance over conventional bulk CMOS is more often than not from lower average threshold-voltage due to transient floating body (FB) operation and lower junction capacitance. SOI MOSFET has two types, which is the partial depleted and fully depleted SOI MOSFET. Nowadays, the partially depleted (PD) instead of fully depleted (FD) SOI becomes the desirable choice for mainstream digital applications, due to the easy manufacturing, better controlling of short channel effect, large design window for the threshold voltage and lower self-heating effect.

### 1.2 Objectives of the project

There are three main objectives of this research:

- i) To create an initial SOI-MOSFET device design.

- ii) To analyze the characterization of SOI MOSFET.

- iii) To compare the electrical characteristic between SOI MOSFET and conventional bulk MOSFET.

4

### 1.3 Problem statement

In the material universe, before certain MOSFET device, proceed with the fabrication process the SILVACO TCAD tools (virtually fabrication tools) will be used to design it at the 1st hand. This will make the cost of production been minimized effectively. In current MOSFET devices, there is physical limitation, which is the short channel effect that is found in conventional MOSFETS as the gate length is further downsized. There are also a few problems in device performance for such an example, switching effect, which came from the higher leakage current (I<sub>OFF</sub>) [3]. Besides that because of the high-power usage and low speed characteristic of conventional circuit MOSFET must be improved to a new level so that this device can improve and be a lot more useful for future. Hence, the new device concept that has more improved than conventional MOSFET is introduced. That device calls Silicon-On-Insulator (SOI) MOSFET. To prove that statement, research has been conducted to analyze the characteristic of SOI MOSFET.

#### 1.4 Scope of the project

This research mainly focused on designing the device structure and determined the characterization of Silicon - On - Insulator (SOI) MOSFET. Besides that, this project was conducted by using Silvaco's TCAD tool. The Silvaco's TCAD simulation tool is