## DESIGN AND ANALYSIS OF A LOW POWER OPERATIONAL AMPLIFIER USING CADENCE

#### NABILAH BINTI SK.ABD.AZIZ

This report is submitted in partial fulfillment of requirements for the bachelor degree of electronic engineering (computer engineering)

Fakulti Kejuruteraan Elektronik dan Kejuruteraan Komputer Universiti Teknikal Malaysia Melaka

**JUNE 2014**

# UTEM UNIVERSITI TEKNIKAL MALAYSIA MELAKA

#### UNIVERSTI TEKNIKAL MALAYSIA MELAKA

FAKULTI KEJURUTERAAN ELEKTRONIK DAN KEJURUTERAAN KOMPUTER

### BORANG PENGESAHAN STATUS LAPORAN PROJEK SARJANA MUDA II

| Tajuk Proj | jek                   | •     | DESIGI<br>CADEN  |         | <u>ANAL`</u>        | YSIS OI  | A LO    | W POV   | NER OPERATIONAL AMPLIFIER USING                                                          |

|------------|-----------------------|-------|------------------|---------|---------------------|----------|---------|---------|------------------------------------------------------------------------------------------|

| Sesi Penga | ajian                 | :     | 1                | 3       | /                   | 1        | 4       |         |                                                                                          |

|            |                       |       |                  |         |                     |          |         |         | u membenarkan Laporan Projek Sarjana<br>naan seperti berikut:                            |

| 1. Lap     | ooran ad              | alah  | hakmil           | ik Univ | ersiti <sup>·</sup> | Teknik   | al Mal  | aysia N | Melaka.                                                                                  |

| 2. Pe      | rpustaka              | an di | benark           | an me   | embua               | t salina | an unti | uk tuju | uan pengajian sahaja.                                                                    |

|            | rpustaka<br>titusi pe |       |                  |         | embua               | t salina | ın lapo | oran in | ii sebagai bahan pertukaran antara                                                       |

| 4. Sila    | a tandak              | an (  | <b>v</b> ):      |         |                     |          |         |         |                                                                                          |

|            |                       | SULI  | Т*               |         |                     | kepen    | -       | Malays  | klumat yang berdarjah keselamatan atau<br>sia seperti yang termaktub di dalam AKTA<br>2) |

|            |                       | TERI  | HAD**            |         |                     |          |         |         | aklumat terhad yang telah ditentukan oleh<br>mana penyelidikan dijalankan)               |

|            |                       | TIDA  | AK TERH <i>i</i> | AD      |                     |          |         |         |                                                                                          |

|            |                       |       |                  |         |                     |          |         |         | Disahkan oleh:                                                                           |

|            |                       |       |                  |         |                     |          |         |         |                                                                                          |

|            | (TAND                 | ATAN  | GAN PEN          | IULIS)  | _                   |          |         |         | (COP DAN TANDATANGAN PENYELIA)                                                           |

|            |                       |       |                  |         |                     |          |         |         |                                                                                          |

| Ti         | arikh:                |       |                  |         |                     |          |         | Taril   | kh:                                                                                      |

"I hereby declare that this report is the result of my own work except for quotes as cited in the references."

Signature :

Author : NABILAH BINTI SK.ABD.AZIZ

Date : 06 JUNE 2014

"I hereby declare that I have read this report and in my opinion this report is sufficient in terms of the scope and quality for the award of Bachelor of Electronic Engineering (Computer Engineering) With Honors'."

Signature :

Supervisor's Name : ENGR. MUHAMMAD IDZDIHAR BIN IDRIS

Date : 06 JUNE 2014

Dedicated to my beloved family especially my father, lecturer and to all my beloved friends.

#### ACKNOWLEDGEMENT

Alhamdullilah, thanks to Allah for giving me chance to complete my final year project. Firstly I would like to express my gratitude towards people who always supported me and believed in me. I am very thankful to my project supervisor Engr. Muhammad Idzdihar for giving me the opportunity to work under him and giving every support at every stage of this project work. I truly appreciate and value all his guidance and encouragement from the beginning to the end of this thesis.

I also want to express my thankful to my friend Norzayani who always guide and help me when I face difficulty during finishing my project. I would also like to thank my project panel Ms. Hashimah and Mdm. Syafeeza for their useful comment regarding on my project. It really helps me a lot on improving my project and also for my future career. Special thanks to my classmate friend Muhammad Hazari for his help and support during completing my writing thesis.

Finally, I wish to thank to my lovely father and my siblings whom always pray the best for me.

#### **ABSTRACT**

In this paper a low power operational amplifier consisted of two stages and operates at 1.8V power supply is design by using 130nm technology. It is designed to meet a set of provided specification. Designers are able to work at low input bias current and also at low voltage due to the unique behavior of the MOS transistors in sub-threshold region. The design of two-stage operational amplifier provides a gain of 69.73dB and a 28.406MHz of gain bandwidth product for a load of 2pF capacitor. It has CMRR of 62.93dB and output slew rate of 20V/µs. The two-stage op-amp has a PSRR+ of 99.76 dB and PSRR- of 90.91dB. The presented op-amp has an Input Common Mode Range (ICMR) of 0.8V to 1.6V and power consumption of 0.389mW. This two-stage op-amp is design using the Silterra 130nm technology library. The layout has been draw and its area had been calculated. The proposed two stage op-amp consist of NMOS current mirror as bias circuit, differential amplifier as the first stage and common source amplifier as the second stage. The first stage of an op-amp contributed high gain while the second stage contributes a moderate gain.

#### **ABSTRAK**

Dalam laporan ini penguat kuasa operasi yang rendah dibentangkan dimana skematiknya terdiri daripada dua peringkat dan beroperasi pada 1.8V bekalan kuasa dengan menggunakan teknologi 130nm. Ia direka untuk memenuhi satu set spesifikasi yang disediakan. Pereka mampu untuk bekerja di rendah input berat sebelah semasa dan juga pada voltan rendah kerana tingkah laku transistor MOS yang unik di rantau subambang. Reka bentuk dua peringkat penguat operasi menyediakan peningkatan sebanyak 69.73dB dan 28.406MHz peningkatan jalurlebar produk bagi beban 2pF kapasitor. Ia mempunyai CMRR degan nilai 62.93dB dan slew rate 20V/us. Kedua-dua peringkat penguat kuasa mempunyai PSRR+ dengan nilai 99.76 dB dan PSRR – dengan nilai 90.91dB. Penguat kuasa yang dibentangkan ini juga mempunyai Input biasa Mod Range (ICMR) dari nilai 0.8V sehingg 1.6V dengan penggunaan kuasa 0.389mW. Dua peringkat penguat kuasa ini telah direka bentuk dengan menggunakan Silterra perpustakaan teknologi 130nm. Susun atur ini telah direka bentuk dan luas kawasannya telah dikira. Dua peringkat penguat kuasa yang di gunakan ini terdiri daripada NMOS arus semasa sebagai litar berat sebelah , penguat kebezaan sebagai peringkat pertama dan sumber penguat biasa sebagai peringkat kedua. Peringkat pertama penguat kuasa selalunya menyumbang peningkatan yang tinggi manakala peringkat kedua menyumbang peningkatan yang sederhana.

#### TABLE OF CONTENT

| DEDIC  | CATION                             | ii: |

|--------|------------------------------------|-----|

| ACKN   | IOWLEDGEMENT                       | iv  |

| ABSTI  | RACT                               | V   |

| ABSTI  | RAK                                | V   |

| TABLI  | E OF CONTENT                       | vi  |

| LIST C | OF TABLE                           | Х   |

| LIST C | OF FIGURE                          | X   |

| LIST C | OF ABBREVIATIONS                   | xii |

| LIST C | OF APPENDIX                        | xiv |

|        |                                    |     |

| CI     | HAPTER I                           | 1   |

| INTI   | RODUCTION                          | 1   |

| 1.1    | Background                         | 1   |

| 1.2    | Op-Amps Applications               |     |

| 1.3    | Low Power of Operational Amplifier | 4   |

| 1.4    | Problem Statement                  | 4   |

| 1.5    | Objectives                         | 2   |

| 1.6    | Scope of Work                      | 5   |

| 1.7    | Thesis Organization                | 5   |

| CI   | HAPT | TER II                                         | 6   |

|------|------|------------------------------------------------|-----|

| LITI | ERAT | TURE REVIEW                                    | 6   |

| 2.1  | Cu   | rrent Mirror                                   | 6   |

| 2.   | 1.1  | Basic Current Mirror                           | 7   |

| 2.2  | Dif  | fferential Amplifier                           | 9   |

| 2.2  | 2.1  | Differential Amplifier Overview                | 9   |

| 2.3  | Co   | mmon Source Amplifier                          | 11  |

| 2.4  | Co   | mmon Source Stage with Current Source Load     | 13  |

| 2.5  | Op   | erational Amplifier                            | 14  |

| 2.:  | 5.1  | Idealized Characteristic                       | 15  |

| 2.:  | 5.2  | Two Stage Operational Amplifier                | 17  |

| 2.:  | 5.3  | Small Signal Analysis of CMOS Two Stage Op-Amp | 18  |

| 2.:  | 5.4  | Proposed Circuit Design                        | 19  |

| 2.:  | 5.5  | Basic Principle Of Two Stage Op-Amp            | 20  |

| 2.:  | 5.6  | Phase Margin                                   | 22  |

| 2.:  | 5.7  | Work Comparison                                | 23  |

|      |      |                                                |     |

| CI   | НАРТ | TER III                                        | 24  |

|      |      | METHODOLOGY                                    | 24  |

| 2.1  |      |                                                | 2.4 |

| 3.1  |      | oject Process Flow                             |     |

| 3.2  |      | sign Specification                             |     |

| 3.3  | De   | sign Calculation                               | 27  |

| 3.4  | De   | sign Simulation and Layout                     | 29  |

| 3 5  | S111 | mmary                                          | 20  |

| CF    | HAPTER IV                            | 30 |

|-------|--------------------------------------|----|

| RES   | ULTS AND DISCUSSION                  | 30 |

|       |                                      |    |

| 4.1   | Introduction                         |    |

| 4.2   | Transient Analysis                   | 30 |

| 4.3   | AC Gain and Phase Analysis           | 31 |

| 4.4   | Input Common Mode Range (ICMR)       | 33 |

| 4.5   | Common Mode Rejection Ratio (CMRR)   | 33 |

| 4.6   | Power Supply Rejection Ration (PSRR) | 35 |

| 4.7   | Slew Rate                            | 36 |

| 4.8   | Output Offset Voltage                | 38 |

| 4.9   | Power Dissipation                    | 38 |

| 4.10  | Discussion                           | 39 |

|       |                                      |    |

| CI    | HAPTER V                             | 41 |

| CON   | NCLUSION AND RECOMMENDATION          | 41 |

| 5.1   | Conclusion                           | 41 |

| 5.2   | Recommendation and Future Work       | 42 |

|       |                                      |    |

| REFER | RENCES                               | 43 |

|       |                                      |    |

| APPEN | NDIX A                               | 46 |

#### LIST OF TABLE

| NO.       | TITLE                         | PAGE |

|-----------|-------------------------------|------|

|           |                               |      |

| Table 2-1 | Work Comparison               | 23   |

| Table 3-1 | Proposed Design Specification | 26   |

| Table 3-2 | Calculated Size of MOSFETs    | 28   |

| Table 3-3 | Optimization Size of MOSFETs  | 29   |

#### LIST OF FIGURE

| NO. OF<br>FIGURE | TITLE                                                     | PAGE |

|------------------|-----------------------------------------------------------|------|

|                  |                                                           |      |

| Figure 1-1       | Symbol of Op-Amp                                          | 1    |

| Figure 1-2       | Block Diagram of Two Stage Op-Amp                         | 2    |

| Figure 1-3       | Differential Amplifier [6]                                | 3    |

| Figure 1-4       | Summing circuit[6]                                        | 3    |

| Figure 2-1       | Basic Current Mirror[8]                                   | 7    |

| Figure 2-2       | NMOS Current Mirror[9]                                    | 8    |

| Figure 2-3       | MOSFET Current Mirror Using Resistor R <sub>ref</sub> [5] | 8    |

| Figure 2-4       | PMOS Current Mirror[5]                                    | 9    |

| Figure 2-5       | Differential Amplifier with Active Loads[7]               | 10   |

| Figure 2-6       | PMOS Common Source Amplifier [5]                          | 13   |

| Figure 2-7       | Common Source with Current Source Load [5]                | 13   |

| Figure 2-8       | Equivalent Circuit of an Ideal Operational Amplifier [5]  | 15   |

| Figure 2-9       | Two Stage Operational Amplifier [11]                      | 18   |

| Figure 2-10      | Small Signal Module for Two Pole System [11]              | 19   |

| Figure 2-11      | Proposed Two Stage Circuit Design                         | 20   |

| Figure 2-12      | the Graph of Increasing Voltage                           | 21   |

| Figure 2-13      | the Graph of Decreasing Voltage                           | 21   |

| Figure 2-14      | Frequency Response of the Amplifier [5]                   | 22   |

| Figure 3-1       | Project Flow Chart                                        | 25   |

|             |                        | xii |

|-------------|------------------------|-----|

| Figure 4-1  | Transient Analysis     | 31  |

| Figure 4-2  | Op-Amp Gain for ICMR + | 32  |

| Figure 4-3  | Op-Amp Gain for ICMR-  | 32  |

| Figure 4-4  | ICMR                   | 33  |

| Figure 4-5  | Differential Mode Gain | 34  |

| Figure 4-6  | Common Mode Gain       | 34  |

| Figure 4-7  | PSRR+                  | 35  |

| Figure 4-8  | PSRR-                  | 36  |

| Figure 4-9  | Rising Edge            | 37  |

| Figure 4-10 | Falling Edge           | 37  |

| Figure 4-11 | Output Offset Voltage  | 38  |

#### LIST OF ABBREVIATIONS

Op-Amp Operational Amplifier

PM Phase Margin

Common Mode Rejection Ration **CMRR**

**PSRR** Power Supply Rejection Ration

Input Common Mode Range **ICMR**

DC Direct Current

AC **Alternating Current**

VCM Voltage Common Mode

#### LIST OF APPENDIX

| NO. | TITLE                           | PAGE |

|-----|---------------------------------|------|

|     |                                 |      |

| A   | Two Stage Layout View           | 46   |

|     | Power Dissipation for VCM=1.6V  | 47   |

|     | Power Dissipation for VCM =0.8V | 47   |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Background

The operational amplifier (op-amp) is a core part in designing an analog electronic circuitry and mixed signal systems[1][2]. There are various levels of complexities when designing an operational amplifier and thus make it a versatile device that ranging from a dc bias generation to a high speed amplifications to filtering[3][4][5]. Operational amplifier is widely used in electronic devices today as it being used in industrial, scientific devices and in a vast array of consumer.

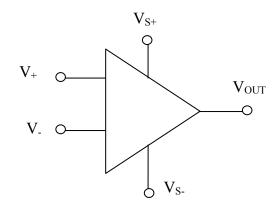

Figure 1-1 Symbol of Op-Amp

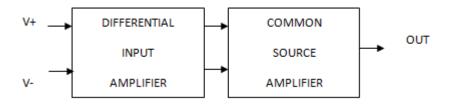

Op-amps is said to be a linear devices as it has nearly all the properties required for not only ideal DC amplification but also widely used for signal conditioning, filtering and performing mathematical operations such as additional, subtraction, differentiation, integration etc[5][4]. A general operational amplifier consist of 3 terminal devices which two of it are inverting input represent by a negative sign ("-") and non-inverting input represent by a positive sign ("+") and both of its have a very high input impedance. The third terminal of an operational amplifier is output port where it can both sinking and sourcing either a voltage or a current. The difference between the two signals being applied to the two inputs of an operational amplifier is called the amplified output signal. Due to this, a differential amplifier is generally used as the input stage of an operational amplifier and hence an operational amplifier is also called a DC-coupled high-gain electronic voltage amplifier. Block diagram of an operational amplifier is described in figure 1-2 where differential input amplifier is a first stage with two input voltage and common source stage as the second stage.

Figure 1-2 Block Diagram of Two Stage Op-Amp

#### 1.2 Op-Amps Applications

It is difficult to describe all of op-amps application as op-amps itself are used in many applications. In this chapter, only some simple but widely used applications of op-amps will be explained which are:

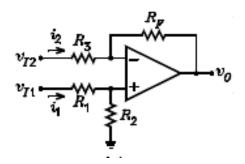

1) Differential Amplifier: The differential amplifier have two inputs, so this two input wil produces the algebraic difference as shown in figure 1-3. As RA=RB

and RF=Rin, the output of differential amplifier can be given as Vo = $\frac{RA}{RF}(V_A - V_B)$ . This connection will amplifies the differences of this two voltages by a constant gain set by the used resistances[5].

Figure 1-3 Differential Amplifier [6]

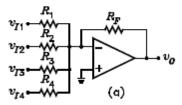

2) Summing Amplifier (Adder): This type of amplifier is handy circuit where it's enabling to add several signals together. From figure 1-4, by keeping the negative terminal approximate to 0V or close to ground, the op-amp will essentially nails one leg of R1, R2 and R3 to a 0V potential and thus makes it easier to write the current in these R1,R2 and R3 resistors.

$$I_1 = \frac{V_1}{R_1}; \quad I_2 = \frac{V_2}{R_2}; \quad I_3 = \frac{V_3}{R_3}...$$

(1)

Based on Kirchhoff's law, the total current,  $I_t = I_1 + I_2 + I_3$  and

$$V_O = -R_F \left( \frac{V_1}{R_2} + \frac{V_2}{R^2} + \frac{V_3}{R_3} \right)$$

(2)

Figure 1-4 Summing circuit[6]

#### 1.3 Low Power of Operational Amplifier

A low power operational amplifier gives advantages in many applications as it prolonging the battery life and thus making it suitable for portable devices. In analog devices product development, it offers in term of power efficient without compromising in term of speed, noise and precision. Low power op-amp is widely used as a biopotential amplifier where it is used to amplify and filter extremely weak bio-potential signals[7]. In industry it is widely used in the usage of barcode scanner.

#### 1.4 Problem Statement

Nowadays, the need on smaller size chip with very small power dissipation had increase the demand on low power design. But the obstacles on designing a good performance of a low power op-amp are on operating with power supplies that is smaller than 1 Volt, on getting an ideal characteristic of op-amp specification and on designing a circuit with the same or better performance than circuits designed for a larger power supply.

#### 1.5 Objectives

The objectives of this project are:

i.To design a low power of operational amplifier and implement it using 130nm CMOS process technology

ii. To simulate and analyze the performance of the proposed design

#### 1.6 Scope of Work

This project scope focus on designing a low power of operational amplifier using Cadence tool, to simulate and analyze the operational amplifier schematic design and to draw the layout of the schematic

#### 1.7 Thesis Organization

This thesis comprises five chapters: Introduction, Literature Review, Project Methodology, Result and Discussion, and Conclusion and Recommendation. The introduction of the project in Chapter 1 will explains the background of the project before move on to the details of the thesis. Chapter 2, the Literature review, reviews the theory on each stage of the design op-amp, and existing work, also several other topics related to the project. Chapter 3 discusses the methodology of the overall project from beginning till the end of the project. The results and discussion are explained in further details in Chapter 4. Finally, the thesis ends with Chapter 5 which concludes the overall project followed by some recommendation for future work.

#### **CHAPTER II**

#### LITERATURE REVIEW

#### 2.1 Current Mirror

The current mirror is one of the most basic circuits which commonly used in linear IC design and it is made by using active devices and used as biasing elements and also as load devices in the amplifier stages. It is a circuit block functions to produce a copy of the current in one active devices the replicated the current in second active devices. Current mirror is a relatively high in output resistance that helps to keep the input current constant regardless of drive conditions.

Practically, an ideal current mirror is considered as an ideal current amplifier. There are three main specifications of current mirror characterization. One of it is the current level it produces. Second is the AC output resistance and it determines how much the output current varies with the voltage applied to the mirror. The last specification is the minimum voltage across the output current mirror terminal that needs to be maintained in order for it to work properly. This minimum voltage will also keep the output transistor of the mirror is in active mode.

For an ideal current mirror, the output current produce is a product of the input current and a desired voltage gain. The input current is reflected to the output due to a unity gain. This ideal current mirror gain must be independent of input current frequency while the output current must be independent to the voltage at the output node. For instance neither is the gain independent of the input frequency nor does the current mirror output current stays independent of voltage variations at the output node[5].

#### 2.1.1 Basic Current Mirror

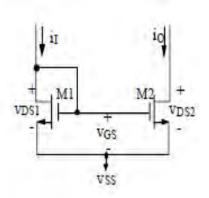

Figure 2.1 below show the basic current mirror implemented using MOSFET transistor. M1 and M2 transistor in the figure 2-1 is assume operating in saturation or active mode. The output current  $I_{OUT}$  is directly related  $I_{REF}$ .

Figure 2-1 Basic Current Mirror[8]

The function for both the gate-source voltage  $(V_{GS})$  and the drain-to-gate voltage  $(V_{DS})$  is the drain current of a MOSFET,  $I_D$  and is given by  $I_D$ = $f(V_{GS}, V_{DG})$ . This relationship is derived from the functionality of the MOSFET device. The drain-to-source voltage is expressed as:

$$V_{DS} = V_{DG} + V_{GS}$$

(3)

Figure 2-2 NMOS Current Mirror[9]

Figure 2-2 shows the NMOS Current Mirror circuit where this two MOSFET have the same  $V_{GS}$  since their gates are shorted and both of their sources are connected to  $V_{SS}$  or ground terminal.

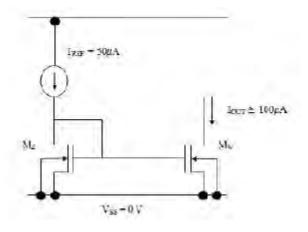

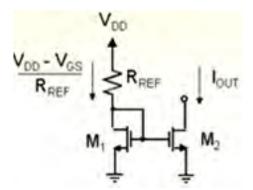

The MOSFET current mirror with the usage of  $R_{REF}$  as shown in figure 2-3 below is for NMOS. From this figure, M2 will acts as a current sink since it pull the current  $I_O=I_{D2}$  from the load which in this case it will be the amplifier of the op-amp.

Figure 2-3 MOSFET Current Mirror Using Resistor R<sub>ref</sub>[5]

For PMOS current mirror in figure 2-4, the PMOS source is connected to the  $V_{DD}$  and Q2 acts as a current source since it pushes current  $I_0$ = $I_{D2}$  into the load