# **UNIVERSITI TEKNIKAL MALAYSIA MELAKA**

## **COMPARATIVE EVALUATION OF MODULATION**

## ALGORITHMS FOR THREE-PHASE NEUTRAL POINT CLAMPED

## (NPC) MULTILEVEL INVERTER

## FINAL YEAR PROJECT REPORT

# FACULTY OF ELECTRICAL ENGINEERING

- NAME : HO SHUN TEN

- COURSE : 4 BEKP S1

- MATRIC NO. : B011010008

- YEAR : 2013/2014

- SUPERVISOR : WAHIDAH BINTI ABDUL HALIM

C Universiti Teknikal Malaysia Melaka

"I hereby declare that I have read through this report entitle "Comparative evaluation of modulation algorithms for three-phase neutral point clamped (NPC) multilevel inverter" and found that it has comply the partial fulfilment for awarding the degree of Bachelor of Electrical Engineering (Industrial Power)"

| Signature         | : |  |

|-------------------|---|--|

| Supervisor's Name | : |  |

| Date              | : |  |

# COMPARATIVE EVALUATION OF MODULATION ALGORITHMS FOR THREE-PHASE NEUTRAL-POINT-CLAMPED (NPC) MULTILEVEL INVERTER

HO SHUN TEN

A report submitted in partial fulfilment of the degree of Electrical Engineer (Industrial Power)

Faculty of Electrical Engineering

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

2013/2014

C Universiti Teknikal Malaysia Melaka

"I declare that this report entitle "Comparative evaluation of modulation algorithms for threephase neutral point clamped (NPC) multilevel inverter" is the result of my own research except as cited in the references. The report has not been accepted for any degree and is not concurrently submitted in candidature of any other degree.

| Signature | : |  |

|-----------|---|--|

| Name      | : |  |

| Date      | : |  |

#### ACKNOWLEDGEMENT

First of all, I would like to express my sincere appreciation to Pn. Wahidah Binti Abdul Halim for help and support me. Precious advice from her had greatly enhanced my understanding on the project title.

Furthermore, I would like to Universiti Teknikal Malaysia Melaka for providing friendly atmosphere to finish this project. Next, I would like thank some of the lecturer for being help and support; especially Pn. Maaspaliza Binti Azri and my academic advice, Mr. Azhar Bin Ahmad.

Finally, I would like to thanks for whole family for having strong faith and believe on me; especially to my father and mother.

#### ABSTRACT

This project gives a comparative evaluation of modulation algorithms for neutral point clamped (NPC), which is a multilevel inverter topology which converted DC sources to AC sources. Neutral point clamped topology is progressively applied in motor drive applications due to their low harmonic output and low switching losses. Nevertheless, higher number levels of NPC multilevel inverter topology and increasing number of semiconductor devices promotes the difficulty to balance capacitors' potential and raise the complexity of switching techniques involved. The important parameters of inverter such as total harmonic distortion (THD) measurements and voltage balancing are controlled by the adopted switching technique. Two switching modulation techniques have been proposed in this study, which are sinusoidal pulsewidth modulation (SPWM) and space vector pulse-width modulation (SVPWM), but the selection of switching technique is based on several key properties which are simple, flexible, and produce low harmonic output. Besides that, this project also presents comparisons between two-level conventional inverter, three-level NPC and five-level NPC. The simulation will done using MATLAB/Simulink. Maintaining the THD level as low as possible is very crucial, because it would cost less effort on filtering. The percentages of voltage THD can be lessened by increasing the modulation index. Besides that, the implementation of SPWM is easier but the THD level is higher, than SVPWM.

#### ABSTRAK

Projek ini adalah perbandingan penilaian algoritma modulasi untuk titik neutral diapit (NPC), ia merupakan topologi penyonsang bertingkat yang menukar sumber arus terus ulang-alik. sumber Kebanyakkan kepada arus aplikasi topologi titik neutral diapit digunakan dalam aplikasi-aplikasi pemacu motor disebabkan oleh harmonik keluaran yang rendah dan kehilangan pensuisan yang rendah. Walau bagaimanapun, pertambahan tingkat bagi topologi titik neutral diapit dan peningkatan jumlah peranti semikonduktor akan menghadapi masalah keseimbangan potensi kapasitor dan meningkatkan kerumitan teknik pensuisan. Parameter penting dalam penyongsang bertingkat adalah jumlah herotan harmonik (THD) dan keseimbangan voltan adalah dikawal oleh teknik pensuisan yang digunakan. Dua teknik modulasi pensuisan telah dicadangkan dalam kajian ini, iaitu modulasi bentuk lebar denyut sinus (SPWM) dan modulasi lebar denyut vektor ruang (SVPWM). Pemilihan teknik pensuisan adalah berdasarkan beberapa ciriciri iaitu kesederhanaan, fleksibiliti, dan menghasilkan keluaran harmonik yang rendah. Selain itu, projek ini juga akan menunjukkan perbandingan antara penyongsang dua tingkat konvensional, tiga tingkat NPC dan lima tingkat NPC. Simulasi tersebut akan dilakukan dengan menggunakan MATLAB/Simulink. Mengekalkan tahap THD yang serendah yang mungkin adalah sangat penting, kerana ia akan mengurangkan kos yang melibatan penapis. Peratusan voltan THD boleh dikurangkan dengan meningkatkan indeks pemodulatan. Di samping itu, pelaksanaan SPWM adalah lebih mudah namun mempunyai tahap THD yang lebih tinggi daripada SVPWM.

### **TABLE OF CONTENTS**

| CHAPTER | TITLE                                                | PAGE |

|---------|------------------------------------------------------|------|

|         | ACKNOWLEDGEMENT                                      | iv   |

|         | ABSTRACT                                             | v    |

|         | TABLE OF CONTENTS                                    | vii  |

|         | LIST OF TABLES                                       | X    |

|         | LIST OF FIGURES                                      | xi   |

|         | NOMENCLATURE                                         | XV   |

| 1       | INTRODUCTION                                         |      |

|         | 1.1 Motivation                                       | 1    |

|         | 1.2 Problem Statement                                | 2    |

|         | 1.3 Objectives                                       | 2    |

|         | 1.4 Scope                                            | 3    |

| 2       | LITRERATURE REVIEW                                   |      |

|         | 2.1 Introduction                                     | 4    |

|         | 2.2 Inverters                                        | 4    |

|         | 2.2.1 Two-level Conventional Inverter                | 5    |

|         | 2.2.2 Neutral Point Clamped Multilevel Inverter      | 7    |

|         | 2.2.3 Flying Capacitor Multilevel Inverter           | 11   |

|         | 2.2.4 Cascaded H-bridge Multilevel Inverter          | 13   |

|         | 2.2.5 Other's Multilevel Inverter Topologies         | 14   |

|         | 2.2.5.1 Hybrid Cascaded H-Bridge Multilevel Inverter | 15   |

|         | 2.2.5.2 Active Neutral Point Clamped                 | 16   |

|         | 2.2.5.3 Hybrid Five-level Multilevel Inverter        | 16   |

|     |                                           | 17 |

|-----|-------------------------------------------|----|

| 2.3 | Control Switching Modulation              | 18 |

|     | 2.3.1 Sinusoidal Pulse-Width Modulation   | 21 |

|     | 2.3.2 Space Vector Pulse-Width Modulation | 25 |

|     | 2.3.2 | Space Vector Pulse-Width Modulation  | 25 |

|-----|-------|--------------------------------------|----|

|     | 2.3.3 | Selective Harmonic Distortion        | 26 |

| 2.4 | Appli | cation of Multilevel Inverter        | 26 |

|     | 2.4.1 | Renewable Energy Multilevel Inverter | 29 |

|     | 2.4.2 | Adjustable Speed Drive               | 30 |

2.5 Summary

### **3 RESEACH METHODOLOGY**

| 3.1 | Introd   | uction                                                | 31 |  |

|-----|----------|-------------------------------------------------------|----|--|

| 3.2 | Contr    | ol Switching Modulation of Two-level Conventional     | 31 |  |

|     | Inverter |                                                       |    |  |

|     | 3.2.1    | Two-level Sinusoidal Pulse-Width Modulation           | 32 |  |

|     | 3.2.2    | Two-level Space Vector Pulse-Width Modulation         | 35 |  |

| 3.3 | Contr    | ol Switching Modulation of Three-level and Five-level | 38 |  |

|     | NPC-MLI  |                                                       |    |  |

|     | 3.3.1    | Multicarrier Sinusoidal Pulse-Width Modulation        | 40 |  |

|     | 3.3.2    | Three-level Space Vector Pulse-Width Modulation       | 44 |  |

| 3.4 | Sumn     | nary                                                  | 52 |  |

### 4 ANALYSIS AND DISCUSSION

| 4.1 | Introd | uction                                            | 53 |

|-----|--------|---------------------------------------------------|----|

| 4.2 | Two-l  | evel Conventional Inverter                        | 53 |

|     | 4.2.1  | THD Analysis of Two-level Conventional Inverter   | 57 |

| 4.3 | Three  | -level Neutral Point Clamped Multilevel Inverter  | 61 |

|     | 4.3.1  | THD Analysis of Three-level Neutral Point Clamped | 66 |

|     |        | Multilevel Inverter                               |    |

|     | 4.3.2  | Balancing of Three-level Neutral Point Clamped    | 70 |

|     |        | Multilevel Inverter                               |    |

| 4.4 | Five-l | level Neutral Point Clamped Multilevel Inverter  | 74  |

|-----|--------|--------------------------------------------------|-----|

|     | 4.4.1  | THD Analysis of Five-level Neutral Point Clamped | 79  |

|     |        | Multilevel Inverter                              |     |

|     | 4.3.2  | Balancing of Three-level Neutral Point Clamped   | 83  |

|     |        | Multilevel Inverter                              |     |

| 4.5 | Comp   | parison Performances of the Topologies           | 91  |

| 4.6 | Sumn   | nary                                             | 93  |

|     |        |                                                  |     |

| CO  | NCLU   | SION                                             |     |

| 5.1 | Concl  | lusion                                           | 94  |

| 5.2 | Recor  | mmendation                                       | 95  |

|     |        |                                                  |     |

| RE  | FERE   | NCES                                             | 96  |

|     |        |                                                  |     |

| AP  | PENDI  | ICES                                             | 106 |

5

### LIST OF TABLES

| TABLE | TITLE                                                     | PAGE |

|-------|-----------------------------------------------------------|------|

| 2.1   | Switching state of three-level NPC-MLI                    | 9    |

| 2.2   | Switching states of five-level multilevel NPC-MLI         | 10   |

| 2.3   | Switching states for two-level inverter                   | 23   |

| 3.1   | Simulation parameters for two-level conventional inverter | 32   |

| 3.2   | Simulation parameters for three-level NPC-MLI             | 38   |

| 3.3   | Simulation parameters for five-level NPC-MLI              | 40   |

| 3.4   | Rule for selection small triangle                         | 47   |

| 4.1   | Important simulation parameter of two-level inverter      | 54   |

| 4.2   | Important simulation parameter of three-level NPC-MLI     | 61   |

| 4.3   | Important simulation parameter of five-level NPC-MLI      | 74   |

| 4.4   | Summaries and comparison of the characteristics           | 93   |

### LIST OF FIGURES

| FIGURE | TITLE                                                 | PAGE |

|--------|-------------------------------------------------------|------|

| 2.1    | Schematic diagram of two-level conventional inverter  | 6    |

| 2.2    | Phase voltage of two-level conventional inverter      | 6    |

| 2.3    | Phase voltage output waveform of multilevel inverter. | 7    |

| 2.4    | Schematic diagram of three-level NPC-MLI              | 8    |

| 2.5    | Schematic diagram of five-level NPC-MLI               | 9    |

| 2.6    | Switches operations of five-level NPC-MLI             | 10   |

| 2.7    | Difference between FC-MLI and NPC-MLI                 | 11   |

| 2.8    | Single-phase of five-level FC-MLI                     | 12   |

| 2.9    | Single cell of H-bridge inverter                      | 13   |

| 2.10   | Schematic Diagram of three-phase five-level CHB-MLI   | 14   |

| 2.11   | HCHB-MLI with single input sources                    | 15   |

| 2.12   | Single-phase three-level ANPC converter               | 16   |

| 2.13   | Hybrid five-level multilevel inverter                 | 17   |

| 2.14   | Comparator                                            | 18   |

| 2.15   | Operation of sinusoidal wave and triangle wave        | 18   |

| 2.16   | Number of level of SPWM                               | 20   |

| 2.17   | MSPWM control strategies                              | 20   |

| 2.18   | The hexagon and small triangle of different level     | 21   |

| 2.19   | Eight vectors hexagon of two-level SVPWM              | 22   |

| 2.20   | Output voltage waveform of two-level inverter         | 24   |

| 2.21   | Vector in sector 1                                    | 24   |

| 2.22   | Switching angles of SHE-PWM in three-level            | 25   |

| 2.23   | Operation of wind farm to national grid               | 27   |

| 2.24   | Operation of wave energy station to national grid     | 27   |

| 2.25 | Operation of standalone PV station to national grid                  | 28 |

|------|----------------------------------------------------------------------|----|

| 2.26 | Back-to-back converter                                               | 29 |

| 2.27 | Adjustable speed drive                                               | 20 |

| 3.1  | Simulink models for three-phase two-level conventional inverter      | 32 |

| 3.2  | Comparison between reference and carrier waveform                    | 33 |

| 3.3  | Gate signal generation for SPWM                                      | 33 |

| 3.4  | Three phase sinusoidal waveform with carrier waveform                | 34 |

| 3.5  | Schemes of three phase switching                                     | 34 |

| 3.6  | Reference voltage vector, $V_{ref}$ and the phase angle, $\theta$    | 35 |

| 3.7  | Division of six sectors                                              | 35 |

| 3.8  | Hexagon with six active vectors                                      | 36 |

| 3.9  | Vector switching states                                              | 36 |

| 3.10 | Determining the switching period                                     | 37 |

| 3.11 | Switching schemes of SVPWM                                           | 37 |

| 3.12 | Simulink models for three-phase three-level NPC-MLI                  | 38 |

| 3.13 | Simulink models for three-phase three-level NPC-MLI                  | 39 |

| 3.14 | Comparator for three-level MSPWM                                     | 40 |

| 3.15 | Gate signal generation for three-level MSPWM                         | 41 |

| 3.16 | Comparator for five-level MSPWM                                      | 41 |

| 3.17 | Gate signal generation for five-level MSPWM                          | 42 |

| 3.18 | Three reference signals with multiple carrier signals                | 43 |

| 3.19 | Three-level MSPWM in Matlab/SIMULINK                                 | 43 |

| 3.20 | Hexagon for three-level SVPWM                                        | 44 |

| 3.21 | Determination of $V_{ref}$ and $\theta$                              | 45 |

| 3.22 | Determination of sector, S and its angle within the sector, $\gamma$ | 45 |

| 3.23 | Calculation of coordinates ( $V_{\alpha}$ , $V_{\beta}$ )            | 46 |

| 3.24 | Small triangles in sector 1: area 1, area 2, area 3, and area 4      | 46 |

| 3.25 | Coordinate in area 3 and new coordinate in area 4                    | 48 |

| 3.26 | Selection of small triangle                                          | 48 |

| 3.27 | Calculation of switching time                                        | 49 |

| 3.28 | Switching pattern of small triangle in sector 1                      | 50 |

|      |                                                                      |    |

| 3.29 | Switching pattern for area 2 in Matlab/SIMULINK                   | 50 |

|------|-------------------------------------------------------------------|----|

| 3.20 | The overall schematic diagram of SVPWM                            | 51 |

| 4.1  | Modelling of the two-level conventional inverter                  | 54 |

| 4.2  | Phase voltage of two-level conventional inverter                  | 54 |

| 4.3  | Simulation output waveforms of SPWM                               | 55 |

| 4.4  | Simulation output waveforms of two-level SVPWM                    | 56 |

| 4.5  | Simulation with varying switching frequency from 1kHz to 5kHz for | 57 |

|      | line voltage                                                      |    |

| 4.6  | Simulation with varying switching frequency from 1kHz to 5kHz for | 58 |

|      | output current                                                    |    |

| 4.7  | Simulation with varying modulation index from 0.5 to 1 for line   | 59 |

|      | voltage                                                           |    |

| 4.8  | Simulation with varying modulation index from 0.5 to 1 for output | 60 |

|      | current                                                           |    |

| 4.9  | Modelling of three-level neutral-point-clamped                    | 61 |

| 4.10 | Phase voltage of three-level NPC-MLI                              | 62 |

| 4.11 | Simulation output waveforms of PD switching modulation            | 63 |

| 4.12 | Simulation output waveform of POD switching modulation            | 64 |

| 4.13 | Simulation output waveforms of three-level SVPWM                  | 65 |

| 4.14 | Simulation with varying switching frequency from 1kHz to 5kHz for | 66 |

|      | line voltage                                                      |    |

| 4.15 | simulation with varying switching frequency from 1kHz to 5kHz for | 67 |

|      | output current                                                    |    |

| 4.16 | Simulation with varying modulation index from 0.5 to 1 for line   | 68 |

|      | voltage                                                           |    |

| 4.17 | Simulation with varying modulation index from 0.5 to 1 for output | 69 |

|      | current                                                           |    |

| 4.18 | Additional circuit on three-level NPC-MLI                         | 70 |

| 4.19 | Switching technique for additional circuit                        | 70 |

| 4.20 | Voltage split among the capacitor with method PD after additional | 71 |

|      | circuit                                                           |    |

|      |                                                                   |    |

| 4.21 | Comparison output voltage with 330µF                               | 72 |

|------|--------------------------------------------------------------------|----|

| 4.22 | Voltage split among capacitor by method POD                        | 73 |

| 4.23 | Self-balancing effect of three-level SVPWM                         | 73 |

| 4.24 | Modelling of five-level neutral-point-clamped                      | 74 |

| 4.25 | Phase voltage of five-level NPC-MLI                                | 75 |

| 4.26 | Simulation output waveforms of PD switching modulation             | 76 |

| 4.27 | Simulation output waveforms of five-level POD switching            | 77 |

|      | modulation                                                         |    |

| 4.28 | Simulation output waveforms of APOD switching modulation           | 78 |

| 4.29 | Simulation with varying switching frequency from 1kHz to 5kHz for  | 79 |

|      | line voltage                                                       |    |

| 4.30 | Simulation with varying switching frequency from 1kHz to 5kHz for  | 80 |

|      | output current                                                     |    |

| 4.31 | Simulation with varying modulation index from 0.5 to 1 for line    | 81 |

|      | voltage                                                            |    |

| 4.32 | Simulation with varying modulation index from 0.5 to 1 for output  | 82 |

|      | current                                                            |    |

| 4.33 | Imbalance capacitors voltage of five-level NPC-MLI                 | 83 |

| 4.34 | Distorted line voltage of PD switching modulation                  | 84 |

| 4.35 | Distorted line voltage of POD switching modulation                 | 84 |

| 4.36 | Distorted line voltage of APOD switching modulation                | 85 |

| 4.37 | Additional power circuit of five-level NPC-MLI                     | 86 |

| 4.38 | Balancing of PD after adding the additional circuit                | 87 |

| 4.39 | Balancing of POD after adding the additional circuit               | 87 |

| 4.40 | Balancing of APOD after adding the additional circuit              | 88 |

| 4.41 | Balancing line voltage of PD after adding the additional circuit   | 88 |

| 4.42 | Balancing line voltage of POD after adding the additional circuit  | 89 |

| 4.43 | Balancing line voltage of APOD after adding the additional circuit | 89 |

| 4.44 | comparison of line voltage with 1500µF                             | 90 |

| 4.45 | Comparison % of THD with different output level topologies         | 91 |

| 4.46 | Output waveform with different output levels                       | 92 |

### NOMENCLATURE

| DC    | Direct current                            |

|-------|-------------------------------------------|

| AC    | Alternative current                       |

| MLI   | Multilevel inverter                       |

| SPWM  | Sinusoidal pulse width modulation         |

| SVPWM | Space vector pulse width modulation       |

| NPC   | Neutral point clamped multilevel inverter |

| FC    | Flying capacitor multilevel inverter      |

| CHB   | Cascaded H-bridge multilevel inverter     |

C Universiti Teknikal Malaysia Melaka

#### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 Motivation

The applications of the inverter have become widely used in all aspects during this modern generation, including home appliances, renewable energy field, and industry field. Due to advance of science and technology, emphasizes on green technology had grown rapidly. Hence, more research has been focused on renewable energy. The renewable energy gained from natural environment is needed to transmit back to national grid; inverter plays a very important role to convert the DC renewable source to AC grid source. Currently, engineers have to work harder on the investment of the high efficiency and low harmonic distortion inverters. The design of inverters involved many circuit theory, switching control theory, control processors, and knowledge on power electronics. Advances in power electronics elements with the suitable switching control method will come out desired outputs that guarantee the efficiency and performance of the inverter. It ensures encourages fast growing on good performance technology.

In this study would mainly concentrate on multilevel inverter neutral point clamped (NPC) topology. Operation and performance of every kind of inverter depend on the switching control modulations that been adopted. The switching control modulation that proposed in this study to control the three-phase NPC multilevel inverter are sinusoidal pulse width modulation (SPWM) and space vector pulse-width modulation (SVPWM).

### **1.2 Problem Statement**

Inverters are electronics device that converts the DC source to AC source. Inverters have proven their great benefits on industrial field such as in power grid system to convert renewable source to power grid AC source. Without a doubt, applications of inverter had experienced rapid growth in the past few decades.

However, due to higher harmonic contents and switching losses of conventional inverter, three main multilevel inverter topologies have been widely reviewed, which are neutral point clamped inverter (NPC), cascaded H-bridge inverter and flying capacitor inverter. Neutral point clamped particularly adopted in motor drive application.

The main advantages of the NPC inverter are improving output voltage waveform quality and less output current ripple, which mean less effort required for filtering. The major drawbacks of NPC are increasing number of switches and semiconductor, and thus increase overall costs and control complexity.

The biggest concern of neutral point clamped inverter is the capacitor voltage imbalance problem, which may cause over-voltages of the switches and increase overall harmonic content and switching losses. Suitable control algorithms have to imply to balance the capacitor DC voltage.

### 1.3 Objectives

The objectives of this project are:

- To study modulation methods based on multicarrier pulse-width modulation and space vector pulse-width modulation.

- 2) To solve the neutral point clamped (NPC) voltage imbalance problem.

- 3) To compare the adopted performances of inverter (in terms of THD) with two-level conventional inverter.

### 1.4 Scope

- Analysis performance of conventional inverter and neutral point clamped inverter in term of their voltage imbalance problem, and THD by using MATLAB/Simulink.

- Simulation and modelling process by using MATLAB/Simulink with using different switching techniques to obtain inverters output waveforms

- Performance of inverters with different switching techniques will be analyses and compared with varied switching frequency from 1 kHz to 5 kHz and modulation index from 0.5 to 1.0

#### **CHAPTER 2**

#### LITERATURE REVIEWS

#### 2.1 Introduction

Multilevel inverters having an unshakable position in this industrial field and become an inevitable equipment in most of the applications. This chapter would discussed about the general inverter topologies, such as two-level conventional inverter, neutral point clamped (NPC) multilevel inverter, flying capacitor (FC) multilevel inverter, cascaded H-bridge (CHB) multilevel inverter and asymmetric hybrid multilevel inverter. Asymmetric hybrid multilevel inverter having unique characteristics, as it will combine the advantages of each combine topologies. Besides that, this chapter would also discussed relevant control switching modulation for these inverter topologies; sinusoidal pulse-width modulation (SPWM), space vector pulse-width modulation (SVPWM), and selective harmonic elimination (SHE). Different control switching modulation with different topologies would produce different output power quality. Finally, in this chapter extra attention would pay on the latest application of the multilevel inverters technologies, such as application of inverter in renewable energy field, and adjustable speed device.

### 2.2 Inverters

Nowadays, multilevel inverters are gained intense attention in the electrical field due to its advantages of lower power dissipation in power switches, low harmonic and low electromagnetic interference outputs [3]. Inverters are the devices used to generate AC voltage from constant DC voltage. Multilevel inverter is the circuit can produce more output voltage level compare with the conventional inverter. An additional voltage levels is to smoother the output waveform, thus lower the total harmonic distortions [4]. In other words, multilevel inverters are categories as the output levels that are more than two. There are several famous multilevel inverters topologies that are used in industry, which are neutral point diode clamped multilevel inverter (NPC-MLI), flying capacitor multilevel inverter (FC-MLI), cascaded H-bridge multilevel inverter (CHB-MLI) and asymmetric hybrid multilevel inverter. The first three types are the most common inverter; meanwhile the asymmetric hybrid multilevel inverter is the combination of various types of inverter. The applications of the inverters have enhanced tremendously especially in the field of renewable energy sources and motor drives applications. For example, the original energy that being collected from PV solar cells is in the DC sources form, but the energy feed into national grid must in AC sources form [1].

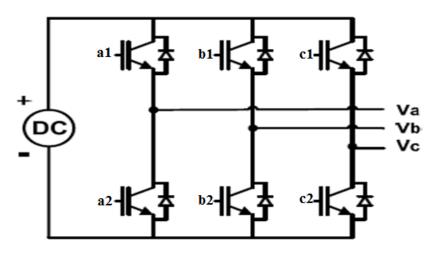

### 2.2.1 Two-Level Conventional Inverter

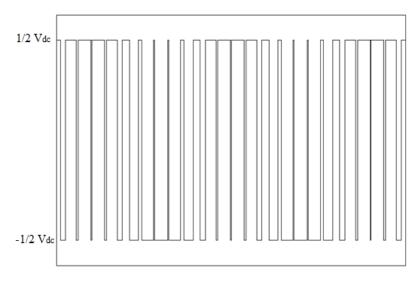

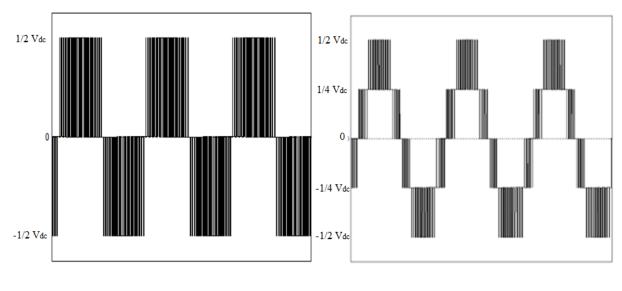

Nowadays, due rapid develop in power electronics field, multilevel inverters which being led to higher-level are available in market. The origin design of these multilevel inverters is based on two-level conventional inverter as shown in Figure 2.1. This topology has two advantages compared to multilevel inverter. The first advantage that is very obvious and can be easily observed in two-level conventional inverter is less switching devices needed, thus easier control the switching modulation. The second advantage is conventional inverter does not facing any DC-link voltage imbalance problem as faced by multilevel inverter [5]. However, this topology has a defeat which is higher harmonic content and makes it less suitable to sensitive devices. Two-level conventional inverter can only generate two output stages,  $\frac{1}{2} V_{dc}$  and  $-\frac{1}{2}$  $V_{dc}$  as can be seen in Figure 2.2 [6]. With multilevel inverter, the output can be three level, five level or other higher levels. The phase output of three levels is +  $\frac{1}{2} V_{dc}$ , 0, -  $\frac{1}{2} V_{dc}$ , meanwhile the output of the five levels is +  $\frac{1}{2}V_{dc}$ , +  $\frac{1}{4}V_{dc}$ , 0, -  $\frac{1}{4}V_{dc}$ , and -  $\frac{1}{2}V_{dc}$  as illustrated in Figure 2.3. The upper switch and lower switch in one leg are work in complementary manner, which is when the lower switch is turned on and the upper switch must in turned off modes. There are no a single moment for both of switches in one leg are turned on or turned off, or else the DC supply would be shorted [7].

Figure 2.1: Schematic diagram of two-level conventional inverter

Figure 2.2: Phase voltage of two-level conventional inverter

(a) Three-level (b) Five-level Figure 2.3: Phase voltage output waveform of multilevel inverter

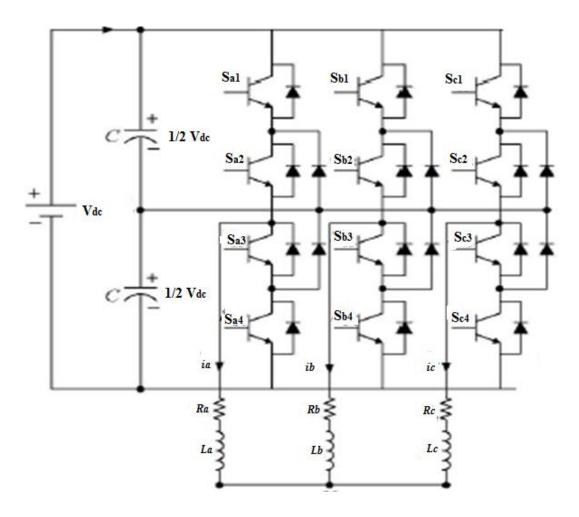

#### 2.2.2 Neutral Point Clamped Multilevel Inverter

Neutral point clamped (NPC-MLI) multilevel inverter was introduced by A. Nabae, I. Takahashi and H. Akagi in 1980 [3]. Multilevel inverters have become common and popular in medium voltage high-power applications. The NPC-MLI utilized several DC capacitors and clamping diodes to produce AC waveforms with multiple levels. Major advantages of NPC-MLI compared to two-level conventional inverter are improving power quality in terms of THD, and reduce the switching losses [9]. However, NPC-MLI still received a lot of attention from researcher due to the dc-link voltage imbalance problem. The DC input sources must divide equally between the series DC capacitors; the imbalance voltage between series DC capacitors would increase distortion of output waveforms. Figure 2.4 shows the three-level NPC inverter. Three-level NPC inverter consists of two series dc-link capacitors, four IGBTs connected in series and two clamping diodes in one phase [31].

Figure 2.4: Schematic diagram of three-level NPC-MLI

The number of capacitors,  $N_c$  used depends on the number of output voltage levels of the inverters as given in Equation (2.1), where *n* is number of voltage level. The voltage across each capacitor,  $V_c$  must be balanced according to Equation (2.2).

Number of capacitor in NPC,  $N_c = (n - 1)$  (2.1)

$$V_c = \frac{V_{dc}}{N} \tag{2.2}$$

As illustrated in Table 2.1, three possible switching states, P, O, N can occurs in each phase. When the upper two IGBTs, S<sub>1</sub> and S<sub>2</sub> are switched ON, the switching state is P. Then, when the middle two IGBTs, S<sub>2</sub> and S<sub>3</sub> are switched ON, the switching state is O. Later, when the lower two IGBTs, S<sub>3</sub> and S<sub>4</sub> are switched on, the switching state is N. Switches S<sub>1</sub> and S<sub>3</sub> are work in complementary manner. With one switched ON, the other switched must be switched OFF. Same operations work on switches S<sub>2</sub> and S<sub>4</sub> [32].