## UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## SINGLE PHASE CAPACITOR CLAMPED MULTILEVEL INVERTER

This report submitted in accordance with requirement of the Universiti Teknikal Malaysia Melaka (UTeM) for the Bachelor Degree of Electrical Engineering Technology (Industrial Power)(Hons.)

by

## AHMAD HAFIZ BIN AYOB B071110012 920423115355

# FACULTY OF ENGINEERING TECHNOLOGY 2014

C Universiti Teknikal Malaysia Melaka

UNIVERSITI TEKNIKAL MALAYSIA MELAKA

## BORANG PENGESAHAN STATUS LAPORAN PROJEK SARJANA MUDA

| BORANG PENGESAHAN STATUS EAFORAN PROJER SARJAI                                                                                                                                                                                                                                                                                                                                                              |                                           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| TAJUK: SINGLE PHASE CAPACITOR CLAMPED MULTILEVEL INVERTER                                                                                                                                                                                                                                                                                                                                                   |                                           |  |  |  |

| SESI PENGAJIAN: 2014/15 Semester 7                                                                                                                                                                                                                                                                                                                                                                          |                                           |  |  |  |

| Saya AHMAD HAFIZ BIN AYOB                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |  |  |

| mengaku membenarkan Laporan PSM ini disimpan di Perpustak<br>Teknikal Malaysia Melaka (UTeM) dengan syarat-syarat kegunaan sep                                                                                                                                                                                                                                                                              |                                           |  |  |  |

| <ol> <li>Laporan PSM adalah hak milik Universiti Teknikal Malaysia Melaka dan penulis.</li> <li>Perpustakaan Universiti Teknikal Malaysia Melaka dibenarkan membuat salinan<br/>untuk tujuan pengajian sahaja dengan izin penulis.</li> <li>Perpustakaan dibenarkan membuat salinan laporan PSM ini sebagai bahan<br/>pertukaran antara institusi pengajian tinggi.</li> <li>**Sila tandakan (✓)</li> </ol> |                                           |  |  |  |

| SULIT (Mengandungi maklumat yang berdarja<br>atau kepentingan Malaysia sebagaimana<br>dalam AKTA RAHSIA RASMI 1972)                                                                                                                                                                                                                                                                                         |                                           |  |  |  |

| TERHAD (Mengandungi maklumat TERHAD yang oleh organisasi/badan di mana penyelidika                                                                                                                                                                                                                                                                                                                          |                                           |  |  |  |

| TIDAK TERHAD                                                                                                                                                                                                                                                                                                                                                                                                |                                           |  |  |  |

| Disahkan o                                                                                                                                                                                                                                                                                                                                                                                                  | leh:                                      |  |  |  |

| Alamat Tetap:                                                                                                                                                                                                                                                                                                                                                                                               |                                           |  |  |  |

| Lot 2762, Kampung Bukit Petiti, Manir<br>21200 Kuala Terengganu,<br>Terengganu                                                                                                                                                                                                                                                                                                                              |                                           |  |  |  |

| Tarikh:                                                                                                                                                                                                                                                                                                                                                                                                     |                                           |  |  |  |

| ** Jika Laporan PSM ini SULIT atau TERHAD, sila lampirkan surat daripada pihak berkenaan dengan menyatakan sekali sebab dan tempoh laporan PSM ini perlu SULIT atau TERHAD.                                                                                                                                                                                                                                 | perkuasa/organisasi<br>dikelaskan sebagai |  |  |  |

C Universiti Teknikal Malaysia Melaka

#### FAKULTI TEKNOLOGI KEJURUTERAAN

Tel : +606 234 6623 | Faks : +606 23406526

Rujukan Kami (Our Ref) : Rujukan Tuan (Your Ref) :

01JAN 2015

Pustakawan Perpustakaan UTeM Universiti Teknikal Malaysia Melaka Hang Tuah Jaya, 76100 Durian Tunggal, Melaka.

Tuan/Puan,

### PENGKELASAN LAPORAN PSM SEBAGAI SULIT/TERHAD LAPORAN PROJEK SARJANA MUDA TEKNOLOGI KEJURUTERAAN ELEKTRIK (KUASA INDUSTRI): AHMAD HAFIZ BIN AYOB

Sukacita dimaklumkan bahawa Laporan PSM yang tersebut di atas bertajuk "Single Phase Capacitor Clamped Multilevel Inverter" mohon dikelaskan sebagai \*SULIT / TERHAD untuk tempoh LIMA(5) tahun dari tarikh surat ini.

2. Hal ini adalah kerana <u>IANYA MERUPAKAN PROJEK YANG DITAJA</u> <u>OLEH SYARIKAT LUAR DAN HASIL KAJIANNYA ADALAH SULIT</u>.

Sekian dimaklumkan. Terima kasih.

Yang benar,

\* Potong yang tidak berkenaan

## DECLARATION

"I hereby declare that the content in this project is the result of my own work expect references and citations which I have clearly stated the source of origin"

| Signature | :                      |

|-----------|------------------------|

| Name      | : AHMAD HAFIZ BIN AYOB |

| Date      | : 20TH DEC 2014        |

## APPROVAL

This report is submitted to the Faculty of Engineering Technology of UTeM as a partial fulfillment of the requirements for the degree of Bachelor of Electrical Engineering Technology (Industrial Power) with Honors. The member of the supervisory committee is as follow:

.....

(Project Supervisor)

## ABSTRAK

Penyongsang pelbagai peringkat adalah sebuah alat yang mampu menghasilkan aras voltan berperingkat. Terdapat tiga jenis topologi utama penyongsang pelbagai peringkat, penurunan jambatan-H, diod, pengapit diod dan pengapit kapasitor. Topologi pengapit kapasitor mempunyai voltan semulajadi. Pengapit kapasitor pelbagai peringkat terdiri daripada beberapa gabungan keadaan suis untuk membentuk satu aras arus terus bagi penyongsang, jadi pemilihan gabungan keadaan suis sangat penting supaya setiap MOSFET boleh ditukarkan dengan sama. Tujuan projek ini adalah untuk memahami satu fasa pengapit kapasitor pelbagai peringkat dan mensimulasi topologi dicadangkan menggunakan perisian yang Simulink/Matlab. Pelan litar termasuk litar pemacu disimulasi pada perisian Simulink. Selain itu, projek ini menggunakan pemodulatan lebar denyut (PWM) sebagai kaedah pengawalan sementara MOSFET sebagai suis kuasanya.

### ABSTRACT

Multilevel inverter is a device that capable of produce different voltage level. There are three main types of the multilevel inverter topology, cascaded H-bridge, diode clamped and capacitor clamped. Capacitor clamped topology has a natural voltage balancing property. Capacitor clamped multilevel inverter (CCMI) consists of several switching state combination for one DC level of the inverter, so the selection of switching state combination is important so that every MOSFETs can be switched on equally. The aim of this project is to study a single phase capacitor clamped multilevel inverter and simulate the proposed topology using Simulink software. The designs of the circuit including the triggering circuit were done on the Simulink/Matlab simulation software. This project is using pulse width modulation (PWM) as its control methods meanwhile MOSFETs as its power switch.

## DEDICATION

To my beloved parents AYOB BIN MAMAT (FATHER) AZNAN BINTI AWANG (MOTHER)

## ACKNOWLEDGEMENT

First and foremost, I would like to take this golden opportunity to express my appreciation to my final year project supervisor, Miss Suziana for being a dedicated lecturer guiding me through this project to run smoothly. This project cannot be completed and perfected if without the valuable suggestion and useful information from my supervisor. Her patience and enthusiastic in guided me through this final year project have gave me a great courage in completing this project.

Apart from that, I also would like to thanks to my lecturers and all my friends for the helped in giving me their morals support during this project development and also shared some information with regards to the multilevel inverter and the software guide.

Last but not least, I would like to express my deepest love and gratitude to my beloved parents for giving me unlimited encouragement during my studies in University Technical Malaysia Malacca (UTeM).

Finally, to the God Almighty (Thank you - Alhamdulillah)

## **TABLE OF CONTENTS**

| DECLA  | ARATION                                         | i   |

|--------|-------------------------------------------------|-----|

| APPRO  | OVAL                                            | ii  |

| ABST   | RAK                                             | iii |

| ABSTE  | RACT                                            | iv  |

| DEDIC  | ATION                                           | v   |

| ACKN   | OWLEDGEMENT                                     | vi  |

| LIST C | OF TABLES                                       | ix  |

| LIST C | OF FIGURES                                      | х   |

| LIST C | F ABBREVIATIONS, SYMBOLS AND NOMENCLATURE       | xi  |

| CHAP   | TER 1                                           | 1   |

| 1.1    | Background                                      | 1   |

| 1.2    | Problem Statement                               | 2   |

| 1.3    | Objective of Project                            | 3   |

| 1.4    | Scope of Study                                  | 3   |

| CHAP   | TER 2                                           | 4   |

| 2.1    | Inverter                                        | 4   |

| 2.2    | Voltage Source Inverter                         | 5   |

| 2.3    | Multilevel Inverter (MLI)                       | 6   |

| 2      | 3.1 Capacitor Clamped Multilevel Inverter       | 6   |

| 2      | 3.2 Diode Clamped Multilevel Inverter           | 7   |

| 2      | 3.3 Cascade H-Bridge Multilevel Inverter (CHMI) | 8   |

| 2.4    | Switching Device                                | 8   |

| 2.5    | Pulse Width Modulation (PWM)                    | 9   |

| 2.6    | Total Harmonic Distortion (THD)                 | 10  |

| CHAP   | TER 3                                           | 11  |

| 3.1    | Process Flow Chart                              | 11  |

| 3.2    | Circuit Development                             | 13  |

| 3.2    | 2.1 Matlab/Simulink                             | 14  |

| 3.2    | 2.2 Proteus                                     | 16  |

| 3.2    | 2.3 Code Composer Studio (CCS)                  | 17  |

| 3.3         | На     | rdware Implementation                       | 18 |

|-------------|--------|---------------------------------------------|----|

| 3.          | 3.1    | Etching Process                             | 18 |

| 3.          | 3.2    | Soldering Process                           | 22 |

| 3.          | 3.3    | Testing Connection Process                  | 23 |

| 3.          | 3.4    | Driver                                      | 23 |

| 3.          | 3.5    | The MOSFET                                  | 24 |

| 3.          | 3.6    | Microcontroller                             | 25 |

| 3.          | 3.7    | Troubleshooting                             | 25 |

| 3.          | 3.8    | Bill of Materials (BOM)                     | 27 |

| 3.4         | Re     | port Writing                                | 27 |

| CHAP        | TER    | 4                                           | 28 |

| 4.1         | Sir    | nulation Development Results and Discussion | 28 |

| 4.2         | На     | rdware Development Results and Discussion   | 30 |

| CHAP        | TER    | 5                                           | 33 |

| 5.1         | Co     | nclusion                                    | 33 |

| 5.2         | Fu     | ture Work                                   | 34 |

| 5.3         | Co     | ommercialization                            | 34 |

| REFER       | RENC   | CES                                         | 35 |

| APPEN       | NDIC   | ES                                          | 37 |

| APPEN       | NDIX   | ζ Α                                         | 38 |

| Calcula     | ations | 5                                           | 38 |

| APPEN       | NDIX   | C B                                         | 40 |

| Gantt C     | Chart  | S                                           | 40 |

| APPENDIX C  |        |                                             | 41 |

| Data Sheets |        |                                             | 41 |

## LIST OF TABLES

| Tables         | Title           | Page |

|----------------|-----------------|------|

|                |                 |      |

| Table 2.1: The | Switching State | 7    |

| Table 3.2: BOI | M               | 27   |

| Table 4.3: THI | D Value         | 30   |

## LIST OF FIGURES

## Figure Title

| Figure 2.1: Inverter                         | 4  |

|----------------------------------------------|----|

| Figure 2.2: The VSI Segment.                 | 5  |

| Figure 2.3: The MOSFET.                      | 9  |

| Figure 2.4: Pulse Width Modulation Waveform. | 9  |

| Figure 3.5: THD Setup.                       | 16 |

| Figure 3.6: The Scematic Drawing for CCMI.   | 16 |

| Figure 3.7: The PCB Drawing for CCMI.        | 17 |

| Figure 3.8: The Microcontroller.             | 18 |

| Figure 3.9: Printed PCB.                     | 19 |

| Figure 3.10: UV Curing Machine.              | 19 |

| Figure 3.11: Cleaning Process.               | 20 |

| Figure 3.12: Photoresist Stripper.           | 21 |

| Figure 3.13: Board Being Dried.              | 21 |

| Figure 3.14: Drilling Process.               | 22 |

| Figure 3.15: The Complete Soldering.         | 23 |

| Figure 3.16: The Driver.                     | 24 |

| Figure 3.17: The MOSFET.                     | 24 |

| Figure 3.18: Microcontroller F2808.          | 25 |

| Figure 3.19: The Troubleshooting of Driver.  | 26 |

| Figure 3.20: The Troubleshooting of MOSFET.  | 26 |

## LIST OF ABBREVIATIONS, SYMBOLS AND NOMENCLATURE

- IGBT Insulated Gated Bipolar Transistor

- THD Total Harmonic Distortion

- MOSFET Metal Oxide Semiconductor Field Effect Transistor

- PWM Pulse Width Modulation

- AC Alternating Current

- DC Direct Current

- MLI Multilevel Inverter

- CCMI Capacitor Clamped Multilevel Inverter

- CCS Code Composer Studio

- PCB Printed Circuit Board

## CHAPTER 1 INTRODUCTION

Chapter 1 will explained on the background research of this project research. This chapter will also include the problem statement, the objectives, scope, and project significance.

### 1.1 Background

Multilevel inverter is an alternative structure to the conventional power inverter. Multilevel inverter's operation depends on the structure and the number of the power switches in the inverter. The main feature of the multilevel inverter is it has the ability to reduce the voltage stress on each of the multiple levels in DC bus of the circuit. It also has smaller distortion in the multilevel inverter AC side waveform can be achieved even though at low switching frequency. Besides, switching losses in the inverter are reduced by the increased flexibility for voltage waveform produced by increasing number of voltage level. There are three main types of the multilevel inverter.

Capacitor clamped multilevel inverter involves in the usage of extra capacitor clamped to the power switches phase rail to provide the DC voltage level. This structure allow for the inverter to supply high capabilities especially during the power outages due to the redundancy in switching states provided by the clamping capacitor. This type of multilevel inverter also provides the switching combination redundancy that is very useful for the voltage level balancing. In this project we are using pulse width modulation (PWM) strategies. As the switches, the project is using MOSFET. This is because MOSFET are low power consumption and dissipation, low waste heat, and low mass production costs. In the project, the five level output with sixteen MOSFET is constructed.

### **1.2 Problem Statement**

Due to current source inverter has slower dynamic response and big in size, it may cause main problem in power application. In additional, voltage of CSI need to be maintained continuously and causes a complexity system while reduce its reliability. Besides that, voltage source inverter has decreasing power factor with decreasing speed. This type of inverter also has induced harmonics.

Lately multilevel inverter have been accepted and used in many applications such as motor drivers and static power conditioning systems. Due to electromagnetic compatibility (EMC) problem in an inverter, multilevel inverters can minimize electromagnetic compatibility (EMC) problems as well as generate the output voltages with very low distortion and reduce the dv/dt stresses. It also produce smaller common-mode (CM) voltage, therefore the stress in the bearings of a motor connected to a multilevel motor drive can be reduced. Multilevel converters also can draw input current with low distortion. Besides, multilevel converters can operate at both fundamental switching frequency and high switching frequency PWM. It should be noted that lower switching frequency usually means lower switching loss and higher efficiency.

### 1.3 Objective of Project

The objectives of this project are as follows:

- i. To study a single phase capacitor clamped multilevel inverter.

- ii. To simulate a proposed topology using Matlab/Simulink.

- iii. To implement the hardware of the proposed topology.

### 1.4 Scope of Study

In order to achieve this objective, several scopes had been outlined. The single phase capacitor clamped multilevel inverter using pulse width modulation (PWM) as its control methods meanwhile MOSFETs as its power switch. Simulation of the proposed configuration will be done in Matlab 2011. A coding control and configuration will be done in m-file/Matlab and Simulink/Matlab respectively. This project will be using eight MOSFETs. In additional, DC power supply and capacitor will be used in this project.

## CHAPTER 2 LITERATURE REVIEW

Literature review is a review of a research that has been made regarding the particular problem that has been identified and needs to be solved. This review should describe summarize, evaluate and clarify the project. It also goes beyond the search for information and includes the identification and articulation of relationships between the literature and the field of research.

In this chapter 2, reviews of the previous researches project that are related with this project research will be discussed. The information will be become additional source for the project to make some improvement and more successful. To have a brief understanding of the researches related to the project, a few literature reviews had been done.

### 2.1 Inverter

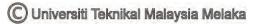

The inverter is an electrical device which converts DC input voltage to AC output voltage. Figure 2.1 shows that DC converts to AC using inverter (Mailah, F. Nashiren et al. 2010).

Figure 2.1: Inverter

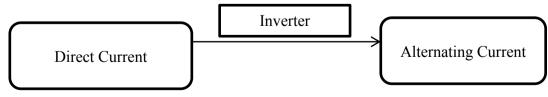

The DC source can be the voltage or current source, it is VSI and CSI. Inverters allowing portability by providing the AC power in areas where only batteries can make it available. Figure 2.2 below shows the course of VSI segment.

Figure 2.2: The VSI Segment

### 2.2 Voltage Source Inverter

DC voltage source for the input of the inverter means that the inverter is a voltages source inverter (VSI). VSI circuit has direct control over output and the shape of voltage waveforms output should be vary to the load that connected at the output.

The advantages of VSI as the following (Bogdan M. Wilamowski et al. 2011):

- i. Good speed range.

- ii. Simple regulator design.

The disadvantages of VSI as the following:

- i. Decreasing power factor with decreasing speed.

- ii. Induced harmonics.

### 2.3 Multilevel Inverter (MLI)

Multilevel inverter is an alternative way to the conventional power converter that had been accepted and used in many applications (Rashid, M. H et al. 2004). The structure and the number of the power switches in the inverter circuit affected its operation. The performance of the inverter can be improved by increasing the number of the power switches in the circuit (A. Tahri, A. Draou and M. Ermis). The main feature of the multilevel inverter is it has the ability to reduce the voltage stress on each of the power switches. Besides, smaller distortion in the multilevel inverter AC side waveform can be achieved even though at low switching frequency.

There are three main type of the multilevel inverter topology (Mailah, F. Nashiren et al. 2010):

- i. Cascaded Multilevel Inverter (CMI)

- ii. Diode Clamped Multilevel Inverter (DCMI)

- iii. Capacitor Clamped Multilevel Inverter (CCMI)

### 2.3.1 Capacitor Clamped Multilevel Inverter

CCMI involves in the usage of extra capacitor clamped to power switches to provide the DC voltage level. This structure allows for the inverter to supply high capabilities especially during the power outages due to the redundancy in switching states provided by the clamping capacitor. This type of multilevel inverter inverters also provides the switching combination redundancy that is very useful for the voltage level balancing.

The advantages of CCMI as the following (Mailah, F. Nashiren et al. 2010):

- i. Does not requiring diode clamping.

- ii. The real and reactive power flow can be controlled.

- iii. Phase redundancies are available for balancing the voltage levels of the capacitors.

- iv. The big number of capacitors enables the inverter to ride through short duration outages and deep voltage stages.

The switching state is the most crucial part in the CCMI topology. So after the studied on CCMI, Table 2.1 shows the switching combination.

|        | Sa <sub>1</sub> | Sa <sub>2</sub> | Sa <sub>3</sub> | Sa <sub>4</sub> | Sa'ı | Sa' <sub>2</sub> | Sa' <sub>3</sub> | Sa' <sub>4</sub> |

|--------|-----------------|-----------------|-----------------|-----------------|------|------------------|------------------|------------------|

| Vdc    | 1               | 1               | 1               | 1               | 0    | 0                | 0                | 0                |

| 3Vdc/4 | 1               | 1               | 1               | 0               | 1    | 0                | 0                | 0                |

| Vdc/2  | 1               | 1               | 0               | 0               | 1    | 1                | 0                | 0                |

| Vdc/4  | 1               | 0               | 0               | 0               | 1    | 1                | 1                | 0                |

| 0      | 0               | 0               | 0               | 0               | 1    | 1                | 1                | 1                |

Table 2.1: The Switching State

### 2.3.2 Diode Clamped Multilevel Inverter

Diode clamped multilevel inverter (DCMI) using the diode as the clamping device to clamp the DC bus voltage to achieve the level of output voltage.

The advantages of DCMI as the following (Khomfoi, S. and Tolbert, L. M. 2007):

- i. The efficiency of the inverter is high because all devices are switched at the fundamental frequency.

- ii. The total harmonic contain is very low when the number of level is high to avoid from filtered.

- iii. The capacitor can be pre-charged as group.

The disadvantages of DCMI as the following:

- i. The excessive clamping diode is required when the number of level is high.

- ii. The real power of individual converter is hard to control in MLI system.

### 2.3.3 Cascade H-Bridge Multilevel Inverter (CHMI)

Cascade H-bridge multilevel inverter is using a series of single phase full bridges makes up a phase for the inverter.

The advantages of CHMI as the following (Prattipati, J. and Kommukuri, V.S. 2012):

- i. Lesser components needed to design the same number of voltage level compared to DCMI and CCMI.

- ii. Since each H-bridge has the same structure, modularized circuit layout and packaging are possible.

- iii. No need extra clamping diode and voltage balancing capacitor.

The disadvantages of CHMI as the following:

i. Separate dc sources are required, resulting in limited applicability.

### 2.4 Switching Device

Switching device is mainly used for the turn on and off mode. For multilevel inverter, the common switching device used for it is Insulated Gate Bipolar Transistors (IGBT) and Metal Oxide Semiconductor Field Effect Transistors

(MOSFET). For this project MOSFET have been chose instead of IGBT because of voltage level for MOSFET is lower than IGBT. Furthermore, the price for MOSFET is cheaper than the IGBT. MOSFET have low power consumption and dissipation, low heat waste and low mass production costs (Josefsson, O. 2013). Figure 2.3 shows the type of MOSFET that been used in this project.

Figure 2.1: The MOSFET

### 2.5 Pulse Width Modulation (PWM)

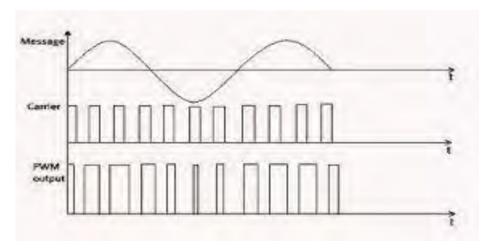

Pulse width modulation is usually used as switching technique. For industrial purposed, the control of voltage output is important to adjust with variation of dc input voltage, to regulate voltage inverter and satisfy the contain volts and frequency requirement (A. Tahri, A. Draou and M. Ermis). Figure 2.4 shows the PWM waveform.

Figure 2.4: Pulse Width Modulation (PWM) Waveform